数字信号控制器中断系统及其设置方法

时间:06-16

来源:互联网

点击:

1.引言

数字信号控制器(Digital Signal Controller, DSC)是将DSP内核与MCU接口相结合的微处理芯片。DSC同时具有数字信号处理能力和MCU控制接口,并且中断系统功能非常丰富。中断是指CPU正在处理某件事情时,突然发生的某一外部事件(如一个电平的变化,一个脉冲沿的发生或定时器的计数溢出等)请求CPU迅速去处理,此时,若条件允许,CPU暂时中断当前的工作,转去处理所发生的事件(中断服务程序),处理完后,再回到原来中断的地方,继续原来的工作,这样一个完整的过程称为中断。外设在需要时通过中断,中止CPU当前的工作,进行信息交换;这样可以实现CPU和多个外设同时工作,提高系统的吞吐率和使用效率。因此,中断具有处理突发事件、提高CPU的效率、可以实现多任务数据事件管理等特点。

当多个中断源发出中断请求时,CPU需要选择接收哪一个中断源,这就带来中断源选择问题。解决这个问题的方法有屏蔽选择法、优先级选择法和优先屏蔽选择法三种。屏蔽选择法主要是通过屏蔽手段将某些中断源请求与CPU隔离;这种屏蔽中断方法可以屏蔽系统所有中断,也可以只屏蔽某个模块中断。屏蔽系统所有中断意味着系统所有中断请求CPU都不接受,屏蔽某个模块中断说明只是屏蔽的模块中断请求CPU不接受,其它没屏蔽模块中断请求可以进入CPU。传统51芯片采用这种方法,飞思卡尔的MC9S08AW60也采用该种方法。屏蔽选择法通过屏蔽手段,有效地解决某些中断源的干扰问题。

优先级选择法通过对中断源设置不同的优先级,当多个中断源发出请求时,优先级高的中断请求率先进入CPU,该中断处理完成后,次优先级的中断源进入CPU,以此类推。这种方法有效避免了屏蔽选择法造成的被屏蔽中断永远不能被处理的不足。

优先屏蔽选择法同时具有上述两种方法的功能,即可屏蔽所有中断源,也可屏蔽某些模块中断源,也可以对非屏蔽的中断源进行优先级设置。这个优先级级别有多种,而51芯片优先级只有两种(高优先级或低优先级)。这种方法即能避免优先级选择法不能解决某些中断源的干扰问题的缺点,又能有效避免了屏蔽选择法造成的被屏蔽中断永远不能被处理的缺点。该种方法目前逐步被DSC芯片商采用,如MC56F8257芯片就采用这种方法。

从上面分析看出,DSC对中断处理比51芯片要复杂,但从另外角度看,DSC中断带来更大的灵活性。灵活性与稳定性一对矛盾,本文以MC56F8257为例,从分析DSC中断系统及其中断处理技术入手,阐述其中断处理方法,并给出处理步骤,为其应用提供指导。

2.MC56F8257中断系统

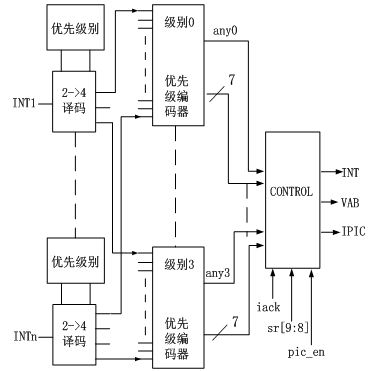

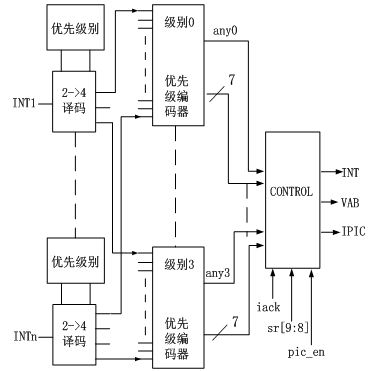

MC56F8257共有67个中断源,5个中断优先级。中断的请求是通过中断控制器模块控制的。中断控制器模块由中断源、优先级设置和控制部分组成,其框图如图1所示,主要用于配置中断优先级、解析中断请求并且将中断向量交给CPU执行。从图1看出,在中断请求处理过程中,当有多个中断源发出请求(INT1…INTn)时,首先优先级别译码模块根据用户设置的优先级进行译码,译码后进入相应的优先级编码器进行编码,最后通过控制模块进行优先级的配置。控制模块根据DSP56800E核中的状态寄存器SR中的屏蔽等设置位,对编码后的中断源进行处理,处理后的结果反映在控制寄存器INTC_CTRL中的INT、IPIC和VAB位。

图1 中断控制器框图

INT是中断位,该位反映内核中断的状态。当该位值为1时,有中断送入内核;否则,无中断送入内核。IPIC是中断优先级位,该位表示送入内核的中断源的优先级,也表示当前内核所接收的中断的最高优先级。VAB是中断矢量号,也是对应中断在中断矢量表中的地址的[7:1]位[9]。

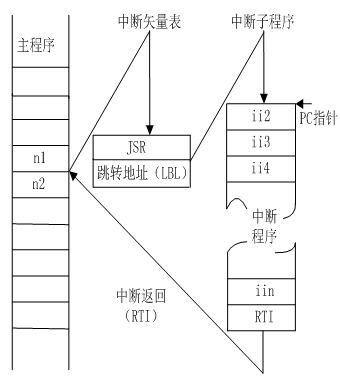

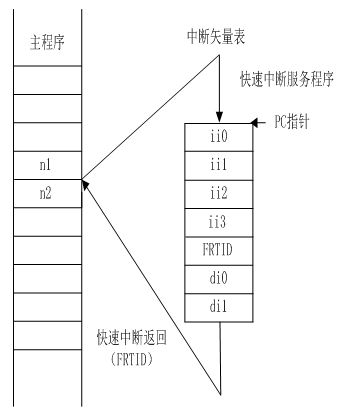

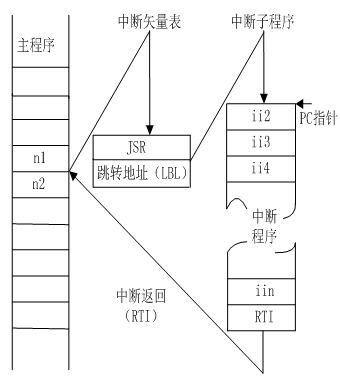

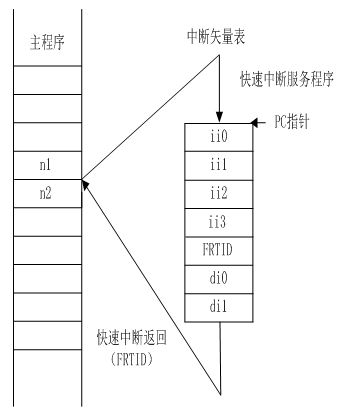

MC56F8257内核为16位增强型DSP56800E,该内核处理中断请求有两种模式:标准和快速中断处理。MC56F8257标准中断处理模式具体流程如图2所示,从图2看出该模式通过JSR指令,转向中断服务程序,占用一定数量的软件开销,但所有级别中断都支持该模式;快速中断处理不需要执行JSR指令(如图3),而是通过快速中断向量地址寄存器获得中断服务程序首地址,节省了软件资源,但它只能用于中断优先级为2级的中断。具体采用何种模式,应根据实际应用需要进行设置。

图2 一般中断处理的控制流程图

图3 快速中断处理的控制流程图

3.MC56F8257中断设置方法

3.1 中断的关闭与开放

开放MC56F8257中某个模块中断,通常需要开放总中断及模块中断来实现。这两部分缺一不可,并且开放总中断在前,开放模块中断在后。同理,关闭MC56F8257中某个模块中断,需要关闭总中断及模块中断来实现,先关闭模块中断,再关闭总中断;如果允许中断嵌套情况,不需关闭总中断。

开放MC56F8257总中断,通过清中断控制寄存器(INTC_CTRL)的INT_DIS位;关闭总中断,需置该位即可,具体代码如下:

#define EnableInterrupt() INTC_CTRL&=~INTC_CTRL_INT_DIS_MASK

#define DisableInterrupt() INTC_CTRL|=INTC_CTRL_INT_DIS_MASK

开放或关闭模块中断,需设置模块内部的控制寄存器的相应位。如开放QSCI模块的接收中断0,需置位QSCI控制寄存器1(QSCIx_CTRL1)中的RFIE位;关闭该中断,清RFIE位即可,具体代码如下:

#define EnableQSCIReInt(0) QSCI_C1(0)|=(QSCI1_CTRL1_RFIE_MASK)

#define DisableQSCIReInt(0) QSCI_C1(0)&=~(QSCI1_CTRL1_RFIE_MASK)

3.2 中断优先级的设置

DSP56800E内核支持5级中断:LP、0、1、2和3,其优先级别依次升高。最低优先级LP只能由系统SWILP指令产生;0~2优先级用户可以编程设置,主要用于外设和外部中断请求;级别3是最高优先级且不可屏蔽。

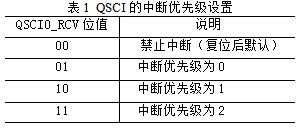

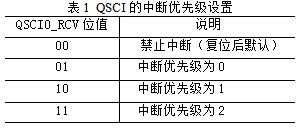

具体设置某个中断源的中断优先级,可通过设置中断优先级寄存器(INTC_IPR0~INTC_IPR7)中的相应位。如设置QSCI中断优先级,通过设置中断优先级寄存器(INTC_IPR2)中的QSCI0_RCV位实现,该位具体含义见表1所示。

从表1看出,QSCI中断可配置三个不同级别,即优先级0、1和2。如果用户不配置QSCI中断的优先级,系统复位时,自动分配其优先级为0;但是复位后,紧接着初始化QSCI模块,其优先级由0级变为2级。

3.3 设置中断屏蔽

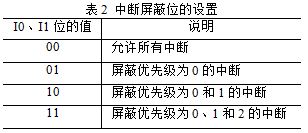

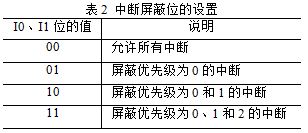

通过设置DSP56800E内核中的状态寄存器SR的I0、I1位,实现屏蔽不同级别优先级中断,具体设置如表2所示。

屏蔽某个优先级中断,可通过使能中断优先级相应的优先级中断来实现。例如,屏蔽优先级0中断,可通过使能优先级1,2,3中断实现,具体代码如下:

#define EnInt(1) {asm(bfset #0x0100,SR); asm(bfclr #0x0200,SR);}

另外,也可以同时屏蔽2个以上级别中断,如屏蔽优先级0,1,2中断,通过使能优先级3中断实现,具体代码如下:

#define EnInt(3) {asm(bfset #0x0300,SR);}

在设置中断屏蔽时,应注意的是主函数的屏蔽中断优先级代码与中断服务程序的相应代码应保证所需的中断不被屏蔽。

3.4 中断矢量表的定义

MC56F8257的67个中断源,其矢量号从0到66 [9]。每个中断源的中断服务程序首地址放入中断矢量表中。当有中断请求时,CPU通过中断矢量号在中断矢量表中找到其中断服务程序的首地址,根据这个首地址找到中断服务程序,进行中断处理。

中断矢量表在FLSAH中的位置由向量基地址寄存器(VBA)决定。向量基地址寄存器VBA[12:0]为21位中断矢量表首地址的高13位,低8位自动补0。具体到某个模块中断服务程序首地址在中断矢量表中的位置,由向量基地址寄存器(VBA)及控制寄存器(INTC_CTRL)的VAB位决定;向量基地址寄存器VBA[12:0]为其在中断矢量表地址[20:0]的高13位[20:8],控制寄存器(INTC_CTRL)的VAB位为其地址的[7:1],低位补0。

系统复位后,VBA的复位值为0x0000,系统进入复位中断(矢量号为0),相应的起始地址在0x00 0000处,这个过程系统自动完成。如果开放某个模块中断,需要将该模块中断服务程序的首地址加载到中断矢量表中的相应位置。具体过程如下:首先建立中断矢量表;没有开放的模块中断,在表中对应位置放入空函数的首地址(通过JSR isrDummy实现);开放的模块中断,在表中对应位置放入中断服务程序的首地址,通常中断服务程序由函数实现,在这里通过放入具体函数首地址实现,如开放QSCI0的接收中断(矢量号为32),其中断服务函数为isrSCI0_Recv,即可通过在矢量表中加入JSR isrSCI0_Recv代码实现,具体如下:

volatile asm void _vect(void);

#pragma define_section interrupt_vectors "interrupt_vectors.text" RX

#pragma section interrupt_vectors begin

volatile asm void _vect(void)

{

JSR init_MC56F824x_5x_ISR_HW_RESET /* Interrupt no. 0 (Used) - ivINT_Reset */

JSR isrDummy /* Interrupt no. 1 (Used) - ivINT_COPReset */

JSR isrDummy /* Interrupt no. 2 (Unused) - ivINT_Illegal_Instruction */

.

.

.

JSR isrSCI0_Recv /* Interrupt no. 32 (Used) - ivINT_QSCI0_RxFull */

.

.

.

JSR isrDummy /* Interrupt no. 65 (Unused) - ivINT_GPIO_A */

JSR isrDummy /* Interrupt no. 66 (Unused) - ivINT_LP */

}

#pragma section interrupt_vectors end

其中, isrDummy的函数形式如下:

void isrDummy(void)

{

}

该函数首地址用来充当未开放模块中断的中断服务程序的首地址,加载到中断矢量表中。

4.MC56F8257中断设置过程

MC56F8257中断设置主要包括关闭总中断、设置中断屏蔽和开放总中断三个过程。中断的设置过程在主函数和中断服务程序中都得体现,但二者中设置过程有所差异。

主函数中的中断设置过程除了包括上述三个过程外,还包括开放模块中断及设置中断优先级,具体流程如下:一是关闭总中断,目的是实现后续各个模块中断设置过程中不被外界干扰;二是开放模块中断,如果需要某个模块中断,可以使能该模块中断;三是设置各模块中断优先级,主要应用于多个中断请求的情况。在这种情况下,根据应用环境决定各个模块中断优先顺序,设置中断优先级。如果不设置优先级,系统会自动产生默认的优先级;四是设置中断屏蔽,通过屏蔽一定级别的中断,使系统避免受其干扰;五开放总中断,在上述设置步骤完成后,通过开放总中断,使其设置有效。

中断服务程序中的中断设置包括关闭总中断、设置中断屏蔽和开放总中断三个过程。关闭总中断和开放总中断过程同主函数,设置中断屏蔽过程与主函数类似,但需要注意的是主函数与中断服务程序中的中断屏蔽设置中应保证所需的中断不被屏蔽。

5.测试及其分析

5.1 测试条件与环境

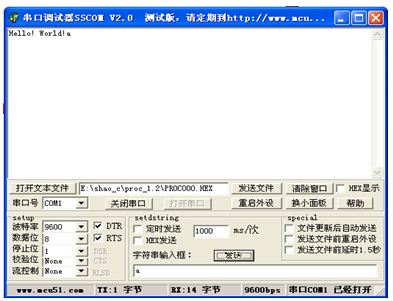

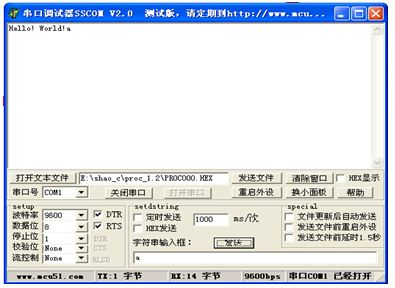

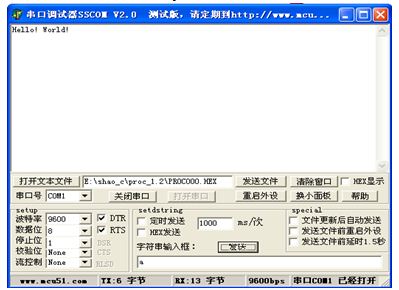

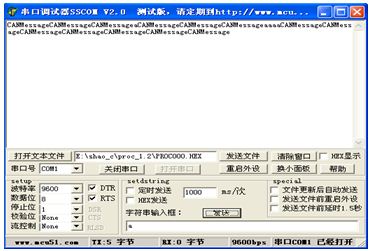

现以MC56F8257中的QSCI模块中断及CAN模块中断为例,说明上述中断设置方法及实施过程,并对其过程进行分析。选用QSCI模块的QSCI0传输数据,波特率设为9600。CAN模块接收数据,CAN通信频率为800KHz。程序编译调试环境为CodeWarrior 10.4。测试环境为串口调试工具SSCOM V2.0。

5.2 测试结果与分析

从不带中断优先级、带中断优先级和优先级嵌套三个方面,测试分析MC56F8257中断设置及实施过程。

(1)不带中断优先级

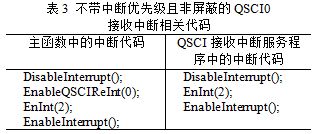

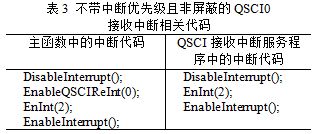

开放QSCI0接收中断,不设置其中断优先级,采用系统默认优先级2,不屏蔽该级别中断,其主函数和中断服务程序中的中断代码如表3所示。

从表3看出,代码DisableInterrupt()在主函数和中断服务程序中都有,但作用不一样。在主函数中的作用是禁止所有中断,为后续中断设置提供良好环境;中断服务程序中的作用是禁止其他中断,防止中断的嵌套。EnableQSCIReInt(0)使能QSCI0接收中断。EnInt(2)使能2,3级别的中断。主函数和中断服务程序中的EnableInterrupt()作用是开放总中断。

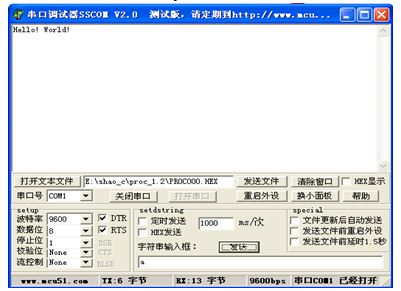

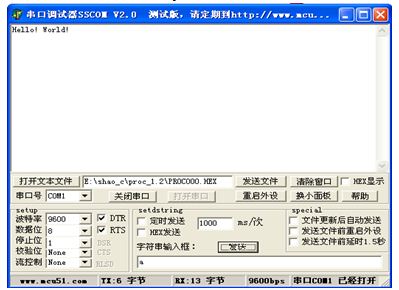

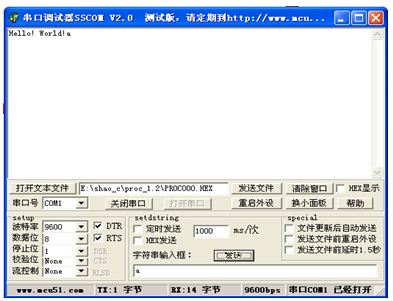

运行程序,从串口调试工具SSCOM V2.0发送字符“a”给MC56F8257,MC56F8257的QSCI0中断接收,并将接收的数据发送给PC机,显示串口调试工具窗口中,具体结果如图2(a)所示。

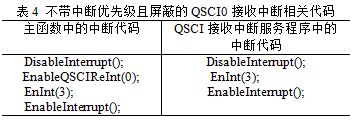

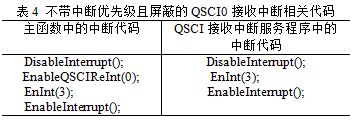

如果屏蔽QSCI0接收中断的默认优先级2,其主函数和QSCI接收中断服务程序中的中断代码有所不同,具体见表4所示。

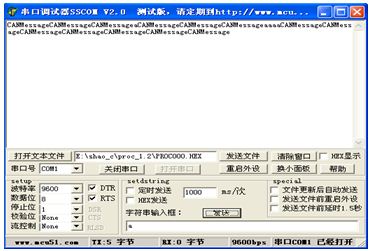

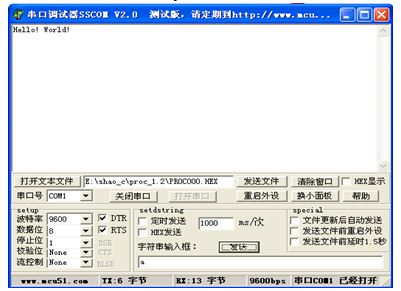

从表4看出,代码EnInt(3)屏蔽了中断优先级0、1和2,只允许优先级为3的中断,无法响应优先级为2的QSCI0接收中断。测试条件同上,其结果如图4(b)所示。从图4(b)看出,接收不到字符“a”。

(a)不屏蔽QSCI0接收中断的结果

(b) 屏蔽QSCI0接收中断的结果

图4 不带中断优先级的QSCI0中断接收结果

(2)带中断优先级

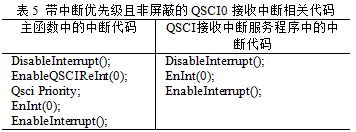

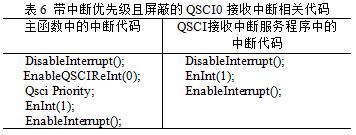

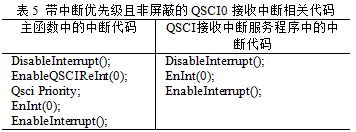

开放QSCI0接收中断,设置其中断优先级,不屏蔽该级别中断,其主函数和中断服务程序中的中断代码如表5所示。

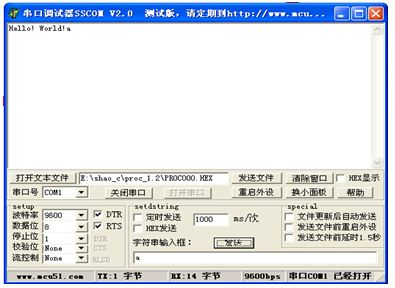

从表5看出,代码Qsci Priority的作用是设置QSCI0接收中断优先级为0;EnInt(0)使能0,1,2,3级别的中断。测试条件同上,其结果如图3(a)所示。从图3(a)看出,同样也能接收到字符“a”。

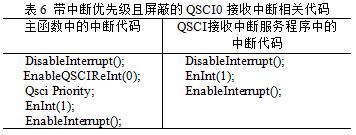

如果屏蔽QSCI0接收中断的优先级0,其主函数和QSCI接收中断服务程序中的中断代码有所不同,具体见表6所示。

从表6看出,代码EnInt(1) 屏蔽了中断优先级0,允许优先级为1,2,3的中断,因此QSCI0接收中断被屏蔽,其测试结果如图5(b)所示。从图5(b)看出,同样接收不到字符“a”。

(a)不屏蔽QSCI0接收中断的结果

(b) 屏蔽QSCI0接收中断的结果

图5 带中断优先级的QSCI0中断接收结果

(3)优先级嵌套

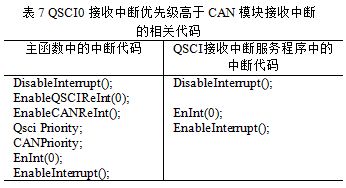

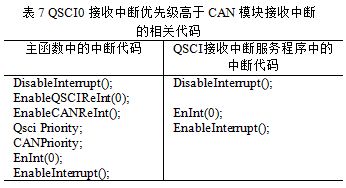

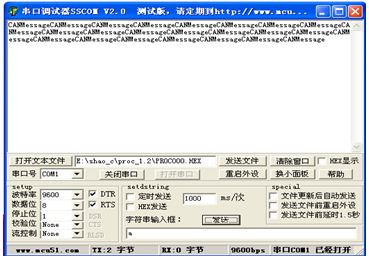

同时开放QSCI0接收中断和CAN模块接收中断,并且前者优先级高于后者,其主函数和中断服务程序中的中断代码如表7所示。

从表7看出,代码Qsci Priority设定QSCI0接收中断的优先级为1,CANPriority 设定CAN接收中断的优先级为0,即QSCI0接收中断的优先级高于CAN接收中断。

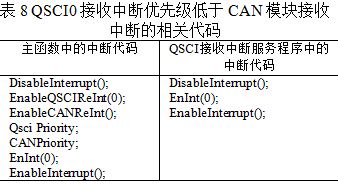

运行程序,当仅有CAN接收中断请求时,CAN接收中断服务程序接收字符串“CANMessage”,并通过QSCI0将该字符发送给串口调试工具,如图6(a)所示。如果在这个过程中,又有QSCI0接收中断请求,CPU则暂停CAN接收中断服务程序的执行,转向QSCI0接收中断服务程序处理,从串口调试工具窗口接收字符“a”,并发送给串口调试工具窗口。将QSCI0接收中断服务程序执行完成后,返回CAN接收中断服务程序继续执行,其结果如图6(a)所示。

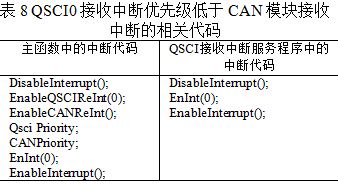

如果开放QSCI0接收中断和CAN模块接收中断,并且前者优先级低于后者,其主函数和中断服务程序中的中断代码如表8所示。

从表8看出,代码Qsci Priority设定QSCI0接收中断的优先级为0,CANPriority设定CAN接收中断的优先级为1,即QSCI0接收中断的优先级低于CAN接收中断。

运行程序,当仅有CAN接收中断请求时,CAN接收中断服务程序接收字符串“CANMessage”,并通过QSCI0将该字符发送给串口调试工具,如图6(b)所示。如果在这个过程中,又有QSCI0接收中断请求,CPU则不会响应其请求,继续执行CAN接收中断服务程序,继续发送字符串“CANMessage” 给串口调试工具,如图6(b)所示。

(a) QSCI0接收中断优先级高于CAN模块接收中断

(b) QSCI0接收中断优先级低于CAN模块接收中断

图6 优先级嵌套时中断处理结果

6.总结

本文以MC56F8257为例,分析DSC中断系统,该系统具有处理多达67个中断源的能力,并能够给这些中断源赋予不同的优先级,实现中断嵌套,并提供标准和快速中断处理两种模式,这些特点促进其广泛被应用。

上述特点也带来中断设置的灵活性,但是如果设置不当,会出现错误。本文在分析中断系统的同时给出其中断设置方法及过程,并详细分析中断优先级设置过程及注意事项。

最后,以MC56F8257中的QSCI模块中断及CAN模块中断为例,从不带中断优先级、带中断优先级和优先级嵌套三个方面,分析中断设置过程及响应结果,结果分析进一步验证MC56F8257中断处理具有屏蔽及优先级可配置等特点。

数字信号控制器(Digital Signal Controller, DSC)是将DSP内核与MCU接口相结合的微处理芯片。DSC同时具有数字信号处理能力和MCU控制接口,并且中断系统功能非常丰富。中断是指CPU正在处理某件事情时,突然发生的某一外部事件(如一个电平的变化,一个脉冲沿的发生或定时器的计数溢出等)请求CPU迅速去处理,此时,若条件允许,CPU暂时中断当前的工作,转去处理所发生的事件(中断服务程序),处理完后,再回到原来中断的地方,继续原来的工作,这样一个完整的过程称为中断。外设在需要时通过中断,中止CPU当前的工作,进行信息交换;这样可以实现CPU和多个外设同时工作,提高系统的吞吐率和使用效率。因此,中断具有处理突发事件、提高CPU的效率、可以实现多任务数据事件管理等特点。

当多个中断源发出中断请求时,CPU需要选择接收哪一个中断源,这就带来中断源选择问题。解决这个问题的方法有屏蔽选择法、优先级选择法和优先屏蔽选择法三种。屏蔽选择法主要是通过屏蔽手段将某些中断源请求与CPU隔离;这种屏蔽中断方法可以屏蔽系统所有中断,也可以只屏蔽某个模块中断。屏蔽系统所有中断意味着系统所有中断请求CPU都不接受,屏蔽某个模块中断说明只是屏蔽的模块中断请求CPU不接受,其它没屏蔽模块中断请求可以进入CPU。传统51芯片采用这种方法,飞思卡尔的MC9S08AW60也采用该种方法。屏蔽选择法通过屏蔽手段,有效地解决某些中断源的干扰问题。

优先级选择法通过对中断源设置不同的优先级,当多个中断源发出请求时,优先级高的中断请求率先进入CPU,该中断处理完成后,次优先级的中断源进入CPU,以此类推。这种方法有效避免了屏蔽选择法造成的被屏蔽中断永远不能被处理的不足。

优先屏蔽选择法同时具有上述两种方法的功能,即可屏蔽所有中断源,也可屏蔽某些模块中断源,也可以对非屏蔽的中断源进行优先级设置。这个优先级级别有多种,而51芯片优先级只有两种(高优先级或低优先级)。这种方法即能避免优先级选择法不能解决某些中断源的干扰问题的缺点,又能有效避免了屏蔽选择法造成的被屏蔽中断永远不能被处理的缺点。该种方法目前逐步被DSC芯片商采用,如MC56F8257芯片就采用这种方法。

从上面分析看出,DSC对中断处理比51芯片要复杂,但从另外角度看,DSC中断带来更大的灵活性。灵活性与稳定性一对矛盾,本文以MC56F8257为例,从分析DSC中断系统及其中断处理技术入手,阐述其中断处理方法,并给出处理步骤,为其应用提供指导。

2.MC56F8257中断系统

MC56F8257共有67个中断源,5个中断优先级。中断的请求是通过中断控制器模块控制的。中断控制器模块由中断源、优先级设置和控制部分组成,其框图如图1所示,主要用于配置中断优先级、解析中断请求并且将中断向量交给CPU执行。从图1看出,在中断请求处理过程中,当有多个中断源发出请求(INT1…INTn)时,首先优先级别译码模块根据用户设置的优先级进行译码,译码后进入相应的优先级编码器进行编码,最后通过控制模块进行优先级的配置。控制模块根据DSP56800E核中的状态寄存器SR中的屏蔽等设置位,对编码后的中断源进行处理,处理后的结果反映在控制寄存器INTC_CTRL中的INT、IPIC和VAB位。

图1 中断控制器框图

INT是中断位,该位反映内核中断的状态。当该位值为1时,有中断送入内核;否则,无中断送入内核。IPIC是中断优先级位,该位表示送入内核的中断源的优先级,也表示当前内核所接收的中断的最高优先级。VAB是中断矢量号,也是对应中断在中断矢量表中的地址的[7:1]位[9]。

MC56F8257内核为16位增强型DSP56800E,该内核处理中断请求有两种模式:标准和快速中断处理。MC56F8257标准中断处理模式具体流程如图2所示,从图2看出该模式通过JSR指令,转向中断服务程序,占用一定数量的软件开销,但所有级别中断都支持该模式;快速中断处理不需要执行JSR指令(如图3),而是通过快速中断向量地址寄存器获得中断服务程序首地址,节省了软件资源,但它只能用于中断优先级为2级的中断。具体采用何种模式,应根据实际应用需要进行设置。

图2 一般中断处理的控制流程图

图3 快速中断处理的控制流程图

3.MC56F8257中断设置方法

3.1 中断的关闭与开放

开放MC56F8257中某个模块中断,通常需要开放总中断及模块中断来实现。这两部分缺一不可,并且开放总中断在前,开放模块中断在后。同理,关闭MC56F8257中某个模块中断,需要关闭总中断及模块中断来实现,先关闭模块中断,再关闭总中断;如果允许中断嵌套情况,不需关闭总中断。

开放MC56F8257总中断,通过清中断控制寄存器(INTC_CTRL)的INT_DIS位;关闭总中断,需置该位即可,具体代码如下:

#define EnableInterrupt() INTC_CTRL&=~INTC_CTRL_INT_DIS_MASK

#define DisableInterrupt() INTC_CTRL|=INTC_CTRL_INT_DIS_MASK

开放或关闭模块中断,需设置模块内部的控制寄存器的相应位。如开放QSCI模块的接收中断0,需置位QSCI控制寄存器1(QSCIx_CTRL1)中的RFIE位;关闭该中断,清RFIE位即可,具体代码如下:

#define EnableQSCIReInt(0) QSCI_C1(0)|=(QSCI1_CTRL1_RFIE_MASK)

#define DisableQSCIReInt(0) QSCI_C1(0)&=~(QSCI1_CTRL1_RFIE_MASK)

3.2 中断优先级的设置

DSP56800E内核支持5级中断:LP、0、1、2和3,其优先级别依次升高。最低优先级LP只能由系统SWILP指令产生;0~2优先级用户可以编程设置,主要用于外设和外部中断请求;级别3是最高优先级且不可屏蔽。

具体设置某个中断源的中断优先级,可通过设置中断优先级寄存器(INTC_IPR0~INTC_IPR7)中的相应位。如设置QSCI中断优先级,通过设置中断优先级寄存器(INTC_IPR2)中的QSCI0_RCV位实现,该位具体含义见表1所示。

从表1看出,QSCI中断可配置三个不同级别,即优先级0、1和2。如果用户不配置QSCI中断的优先级,系统复位时,自动分配其优先级为0;但是复位后,紧接着初始化QSCI模块,其优先级由0级变为2级。

3.3 设置中断屏蔽

通过设置DSP56800E内核中的状态寄存器SR的I0、I1位,实现屏蔽不同级别优先级中断,具体设置如表2所示。

屏蔽某个优先级中断,可通过使能中断优先级相应的优先级中断来实现。例如,屏蔽优先级0中断,可通过使能优先级1,2,3中断实现,具体代码如下:

#define EnInt(1) {asm(bfset #0x0100,SR); asm(bfclr #0x0200,SR);}

另外,也可以同时屏蔽2个以上级别中断,如屏蔽优先级0,1,2中断,通过使能优先级3中断实现,具体代码如下:

#define EnInt(3) {asm(bfset #0x0300,SR);}

在设置中断屏蔽时,应注意的是主函数的屏蔽中断优先级代码与中断服务程序的相应代码应保证所需的中断不被屏蔽。

3.4 中断矢量表的定义

MC56F8257的67个中断源,其矢量号从0到66 [9]。每个中断源的中断服务程序首地址放入中断矢量表中。当有中断请求时,CPU通过中断矢量号在中断矢量表中找到其中断服务程序的首地址,根据这个首地址找到中断服务程序,进行中断处理。

中断矢量表在FLSAH中的位置由向量基地址寄存器(VBA)决定。向量基地址寄存器VBA[12:0]为21位中断矢量表首地址的高13位,低8位自动补0。具体到某个模块中断服务程序首地址在中断矢量表中的位置,由向量基地址寄存器(VBA)及控制寄存器(INTC_CTRL)的VAB位决定;向量基地址寄存器VBA[12:0]为其在中断矢量表地址[20:0]的高13位[20:8],控制寄存器(INTC_CTRL)的VAB位为其地址的[7:1],低位补0。

系统复位后,VBA的复位值为0x0000,系统进入复位中断(矢量号为0),相应的起始地址在0x00 0000处,这个过程系统自动完成。如果开放某个模块中断,需要将该模块中断服务程序的首地址加载到中断矢量表中的相应位置。具体过程如下:首先建立中断矢量表;没有开放的模块中断,在表中对应位置放入空函数的首地址(通过JSR isrDummy实现);开放的模块中断,在表中对应位置放入中断服务程序的首地址,通常中断服务程序由函数实现,在这里通过放入具体函数首地址实现,如开放QSCI0的接收中断(矢量号为32),其中断服务函数为isrSCI0_Recv,即可通过在矢量表中加入JSR isrSCI0_Recv代码实现,具体如下:

volatile asm void _vect(void);

#pragma define_section interrupt_vectors "interrupt_vectors.text" RX

#pragma section interrupt_vectors begin

volatile asm void _vect(void)

{

JSR init_MC56F824x_5x_ISR_HW_RESET /* Interrupt no. 0 (Used) - ivINT_Reset */

JSR isrDummy /* Interrupt no. 1 (Used) - ivINT_COPReset */

JSR isrDummy /* Interrupt no. 2 (Unused) - ivINT_Illegal_Instruction */

.

.

.

JSR isrSCI0_Recv /* Interrupt no. 32 (Used) - ivINT_QSCI0_RxFull */

.

.

.

JSR isrDummy /* Interrupt no. 65 (Unused) - ivINT_GPIO_A */

JSR isrDummy /* Interrupt no. 66 (Unused) - ivINT_LP */

}

#pragma section interrupt_vectors end

其中, isrDummy的函数形式如下:

void isrDummy(void)

{

}

该函数首地址用来充当未开放模块中断的中断服务程序的首地址,加载到中断矢量表中。

4.MC56F8257中断设置过程

MC56F8257中断设置主要包括关闭总中断、设置中断屏蔽和开放总中断三个过程。中断的设置过程在主函数和中断服务程序中都得体现,但二者中设置过程有所差异。

主函数中的中断设置过程除了包括上述三个过程外,还包括开放模块中断及设置中断优先级,具体流程如下:一是关闭总中断,目的是实现后续各个模块中断设置过程中不被外界干扰;二是开放模块中断,如果需要某个模块中断,可以使能该模块中断;三是设置各模块中断优先级,主要应用于多个中断请求的情况。在这种情况下,根据应用环境决定各个模块中断优先顺序,设置中断优先级。如果不设置优先级,系统会自动产生默认的优先级;四是设置中断屏蔽,通过屏蔽一定级别的中断,使系统避免受其干扰;五开放总中断,在上述设置步骤完成后,通过开放总中断,使其设置有效。

中断服务程序中的中断设置包括关闭总中断、设置中断屏蔽和开放总中断三个过程。关闭总中断和开放总中断过程同主函数,设置中断屏蔽过程与主函数类似,但需要注意的是主函数与中断服务程序中的中断屏蔽设置中应保证所需的中断不被屏蔽。

5.测试及其分析

5.1 测试条件与环境

现以MC56F8257中的QSCI模块中断及CAN模块中断为例,说明上述中断设置方法及实施过程,并对其过程进行分析。选用QSCI模块的QSCI0传输数据,波特率设为9600。CAN模块接收数据,CAN通信频率为800KHz。程序编译调试环境为CodeWarrior 10.4。测试环境为串口调试工具SSCOM V2.0。

5.2 测试结果与分析

从不带中断优先级、带中断优先级和优先级嵌套三个方面,测试分析MC56F8257中断设置及实施过程。

(1)不带中断优先级

开放QSCI0接收中断,不设置其中断优先级,采用系统默认优先级2,不屏蔽该级别中断,其主函数和中断服务程序中的中断代码如表3所示。

从表3看出,代码DisableInterrupt()在主函数和中断服务程序中都有,但作用不一样。在主函数中的作用是禁止所有中断,为后续中断设置提供良好环境;中断服务程序中的作用是禁止其他中断,防止中断的嵌套。EnableQSCIReInt(0)使能QSCI0接收中断。EnInt(2)使能2,3级别的中断。主函数和中断服务程序中的EnableInterrupt()作用是开放总中断。

运行程序,从串口调试工具SSCOM V2.0发送字符“a”给MC56F8257,MC56F8257的QSCI0中断接收,并将接收的数据发送给PC机,显示串口调试工具窗口中,具体结果如图2(a)所示。

如果屏蔽QSCI0接收中断的默认优先级2,其主函数和QSCI接收中断服务程序中的中断代码有所不同,具体见表4所示。

从表4看出,代码EnInt(3)屏蔽了中断优先级0、1和2,只允许优先级为3的中断,无法响应优先级为2的QSCI0接收中断。测试条件同上,其结果如图4(b)所示。从图4(b)看出,接收不到字符“a”。

(a)不屏蔽QSCI0接收中断的结果

(b) 屏蔽QSCI0接收中断的结果

图4 不带中断优先级的QSCI0中断接收结果

(2)带中断优先级

开放QSCI0接收中断,设置其中断优先级,不屏蔽该级别中断,其主函数和中断服务程序中的中断代码如表5所示。

从表5看出,代码Qsci Priority的作用是设置QSCI0接收中断优先级为0;EnInt(0)使能0,1,2,3级别的中断。测试条件同上,其结果如图3(a)所示。从图3(a)看出,同样也能接收到字符“a”。

如果屏蔽QSCI0接收中断的优先级0,其主函数和QSCI接收中断服务程序中的中断代码有所不同,具体见表6所示。

从表6看出,代码EnInt(1) 屏蔽了中断优先级0,允许优先级为1,2,3的中断,因此QSCI0接收中断被屏蔽,其测试结果如图5(b)所示。从图5(b)看出,同样接收不到字符“a”。

(a)不屏蔽QSCI0接收中断的结果

(b) 屏蔽QSCI0接收中断的结果

图5 带中断优先级的QSCI0中断接收结果

(3)优先级嵌套

同时开放QSCI0接收中断和CAN模块接收中断,并且前者优先级高于后者,其主函数和中断服务程序中的中断代码如表7所示。

从表7看出,代码Qsci Priority设定QSCI0接收中断的优先级为1,CANPriority 设定CAN接收中断的优先级为0,即QSCI0接收中断的优先级高于CAN接收中断。

运行程序,当仅有CAN接收中断请求时,CAN接收中断服务程序接收字符串“CANMessage”,并通过QSCI0将该字符发送给串口调试工具,如图6(a)所示。如果在这个过程中,又有QSCI0接收中断请求,CPU则暂停CAN接收中断服务程序的执行,转向QSCI0接收中断服务程序处理,从串口调试工具窗口接收字符“a”,并发送给串口调试工具窗口。将QSCI0接收中断服务程序执行完成后,返回CAN接收中断服务程序继续执行,其结果如图6(a)所示。

如果开放QSCI0接收中断和CAN模块接收中断,并且前者优先级低于后者,其主函数和中断服务程序中的中断代码如表8所示。

从表8看出,代码Qsci Priority设定QSCI0接收中断的优先级为0,CANPriority设定CAN接收中断的优先级为1,即QSCI0接收中断的优先级低于CAN接收中断。

运行程序,当仅有CAN接收中断请求时,CAN接收中断服务程序接收字符串“CANMessage”,并通过QSCI0将该字符发送给串口调试工具,如图6(b)所示。如果在这个过程中,又有QSCI0接收中断请求,CPU则不会响应其请求,继续执行CAN接收中断服务程序,继续发送字符串“CANMessage” 给串口调试工具,如图6(b)所示。

(a) QSCI0接收中断优先级高于CAN模块接收中断

(b) QSCI0接收中断优先级低于CAN模块接收中断

图6 优先级嵌套时中断处理结果

6.总结

本文以MC56F8257为例,分析DSC中断系统,该系统具有处理多达67个中断源的能力,并能够给这些中断源赋予不同的优先级,实现中断嵌套,并提供标准和快速中断处理两种模式,这些特点促进其广泛被应用。

上述特点也带来中断设置的灵活性,但是如果设置不当,会出现错误。本文在分析中断系统的同时给出其中断设置方法及过程,并详细分析中断优先级设置过程及注意事项。

最后,以MC56F8257中的QSCI模块中断及CAN模块中断为例,从不带中断优先级、带中断优先级和优先级嵌套三个方面,分析中断设置过程及响应结果,结果分析进一步验证MC56F8257中断处理具有屏蔽及优先级可配置等特点。

- F1aSh存储器在TMS320C3X系统中的应用(11-11)

- 基于PIC18F系列单片机的嵌入式系统设计(11-19)

- DSP在卫星测控多波束系统中的应用(01-25)

- 基于PCI总线的双DSP系统及WDM驱动程序设计(01-26)

- 利用Virtex-5 FPGA实现更高性能的方法(03-08)

- DSP与单片机通信的多种方案设计(03-08)