ARM920T Clockmodes

时间:03-28

来源:互联网

点击:

第一次翻译文档,不对的地方老鸟不要笑。

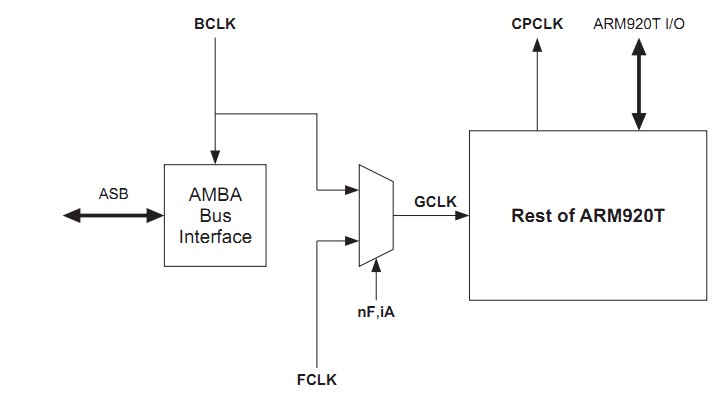

ARM920T有两个功能时钟输入,BCLK和FCLK。内部的,ARM920T用GCLK计时。GCLK可以来自BCLK或FCLK,这需要依靠时钟模式,通过CP15寄存器1的nF位和iA位进行选择。ARM920T的3个时钟模式是快速总线模式,同步模式,异步模式。ARM920T是一个静态设计,你可以无限的停止两个时钟而不丢失状态。

快速总线模式

在快速总线模式,GCLK来自于BCLK,FCLK输入被忽略。这意味着BCLK被用来控制AMBA ASB接口和内部的ARM920T处理器核。复位时,ARM920T进入快速总线模式,操作使用BCLK。一般快速总线模式在启动代码时执行,然后由软件配置PLL产生高频的FCLK。在PLL稳定后可以切换ARM920T到同步或异步时钟,使用FCLK进行操作。

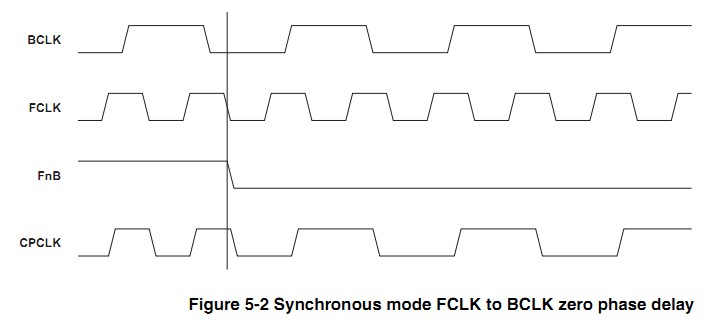

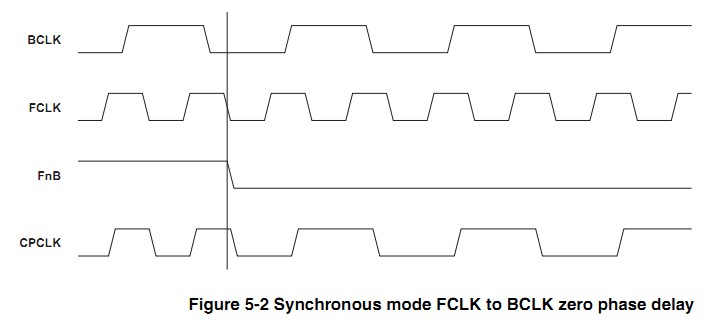

同步模式

在这个操作模式GCLK来自于BCLK或FCLK。但是对于BCLK和FCLK要满足3个条件:

l FCLK必须比BCLK有更高的频率

l FCLK必须是BCLK频率的整数倍数

l 无论BCLK怎么转换,FCLK的频率都要高于BCLK

BCLK被用来控制AMBA ASB总线接口,FCLK用来控制内部的ARM920T处理器核。从FCLK切换到BCLK与BCLK切换到FCLK的代价是相等的。需要耗费0~1个时钟周期使核重新同步。从FCLK切换到BCLK的代价是0~1个BCLK。从BCLK切换到FCLK的代价是0~1个FCLK。

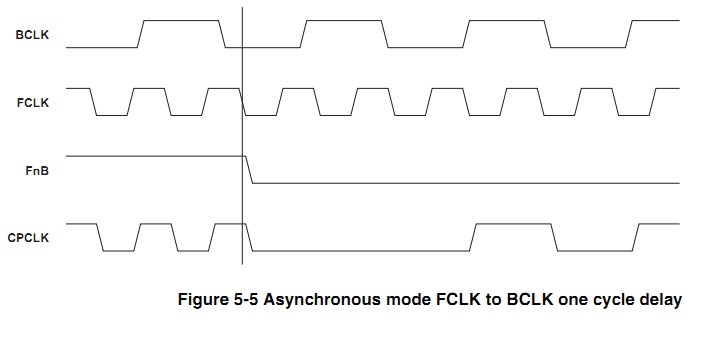

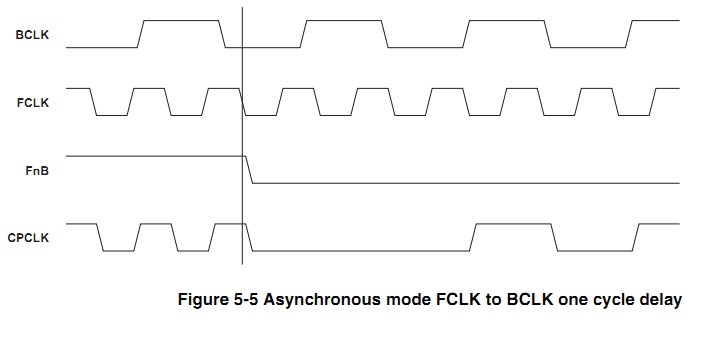

异步模式

在这个操作模式GCLK来自于BCLK或FCLK。FCLK和BCLK之间可以完全异步,只有一个要满足的条件是FCLK的频率要高于BCLK。BCLK被用来控制AMBA ASB总线接口,FCLK用来控制内部的ARM920T处理器核。与同步模式时相同,从FCLK切换到BCLK与BCLK切换到FCLK的代价是相等的。需要耗费0~1个时钟周期使核重新同步。从FCLK切换到BCLK的代价是0~1个BCLK。从BCLK切换到FCLK的代价是0~1个FCLK。

作者:李万鹏

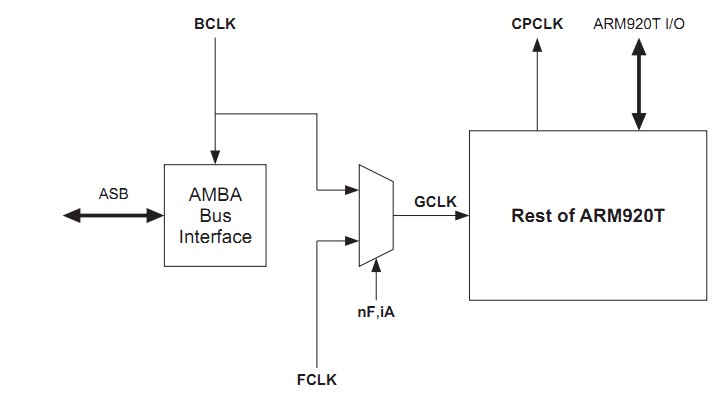

ARM920T有两个功能时钟输入,BCLK和FCLK。内部的,ARM920T用GCLK计时。GCLK可以来自BCLK或FCLK,这需要依靠时钟模式,通过CP15寄存器1的nF位和iA位进行选择。ARM920T的3个时钟模式是快速总线模式,同步模式,异步模式。ARM920T是一个静态设计,你可以无限的停止两个时钟而不丢失状态。

快速总线模式

在快速总线模式,GCLK来自于BCLK,FCLK输入被忽略。这意味着BCLK被用来控制AMBA ASB接口和内部的ARM920T处理器核。复位时,ARM920T进入快速总线模式,操作使用BCLK。一般快速总线模式在启动代码时执行,然后由软件配置PLL产生高频的FCLK。在PLL稳定后可以切换ARM920T到同步或异步时钟,使用FCLK进行操作。

同步模式

在这个操作模式GCLK来自于BCLK或FCLK。但是对于BCLK和FCLK要满足3个条件:

l FCLK必须比BCLK有更高的频率

l FCLK必须是BCLK频率的整数倍数

l 无论BCLK怎么转换,FCLK的频率都要高于BCLK

BCLK被用来控制AMBA ASB总线接口,FCLK用来控制内部的ARM920T处理器核。从FCLK切换到BCLK与BCLK切换到FCLK的代价是相等的。需要耗费0~1个时钟周期使核重新同步。从FCLK切换到BCLK的代价是0~1个BCLK。从BCLK切换到FCLK的代价是0~1个FCLK。

异步模式

在这个操作模式GCLK来自于BCLK或FCLK。FCLK和BCLK之间可以完全异步,只有一个要满足的条件是FCLK的频率要高于BCLK。BCLK被用来控制AMBA ASB总线接口,FCLK用来控制内部的ARM920T处理器核。与同步模式时相同,从FCLK切换到BCLK与BCLK切换到FCLK的代价是相等的。需要耗费0~1个时钟周期使核重新同步。从FCLK切换到BCLK的代价是0~1个BCLK。从BCLK切换到FCLK的代价是0~1个FCLK。

作者:李万鹏

- 基于ARM的除法运算优化策略(01-14)

- 基于ARM的CAN总线智能节点的设计(01-24)

- ARM基础知识教程五 (02-08)

- ARM基础知识教程六(02-08)

- ARM基础知识教程七(02-08)

- ARM基础知识教程八(02-08)