用DSP从模拟视频信号中获取数字图像

时间:11-25

来源:互联网

点击:

本方案选用SAA7111A作为前端视频解码器。SAA71llA视频解码器是双通道模拟预处理电路、自动钳位和增益控制电路、时钟产生电路、数字多标准解码器、亮度/对比度/饱和度控制电路、彩色空间矩阵的组合,是一款功能完善的视频处理器。SAA711lA只需要单一的3.3V电源供电,与C6x11的I/O电压一致。SAA7111A接收CVBS(复合视频)或S-video模拟视频输入,可以将PAL、SECAM、NTSC模式的彩色视频信号解码为CCIR-60l/656兼容的彩色数字分量值,器件功能通过I2C接口控制。

SAA7111A的主要性能特点如下:

◆4路模拟输入一一4路CVBS或2路Y/C或1路Y/C和2路CVBS;

◆主通道静态增益可编程,自动增益控制选择的CVBS或Y/C通道;

◆2个8位视频CMOS模数转换器;

◆片上时钟产生器,只需要24.576 MHz单一时钟输入;

◆自动探测50 Hz和60 Hz场频,自动在PAL和NTSC标准间切换;

◆可以处理PALBGHI、PALN、PAL M、NTSC M、NTSC N、NTSC 4.43、NTSC-Japan和SECAM信号。从以上特点可以看出,SAA7111A功能强大,性能全面,可以满足各种视频转换处理的需要,完全符合本系统的要求。SAA7111A已经在各种视频处理系统中得到广泛的应用,技术性能已得到充分的证明。采用SAA7111A具有很高的性价比。

2.2 DSP与FOFO接口技术

TMS320C6xll的外部存储器接口(EMIF)提供了功能十分强大的外部接口,可以实现与诸多种类的存储器的无缝接口,如SBSRAM、SDRAM、SRAM、ROM等等。但是其对FIFO的接口并不能做到真正的无缝接口,需要增加一些外部逻辑来调整它们之间的时序。

本方案中采用的FIFO一一IDT72V23,是标准的同步FIFO,具有两个独立的读写时钟——RCLK、WCLK;同时还具有读写控制信号WENl、WEN2、REN1和REN2。

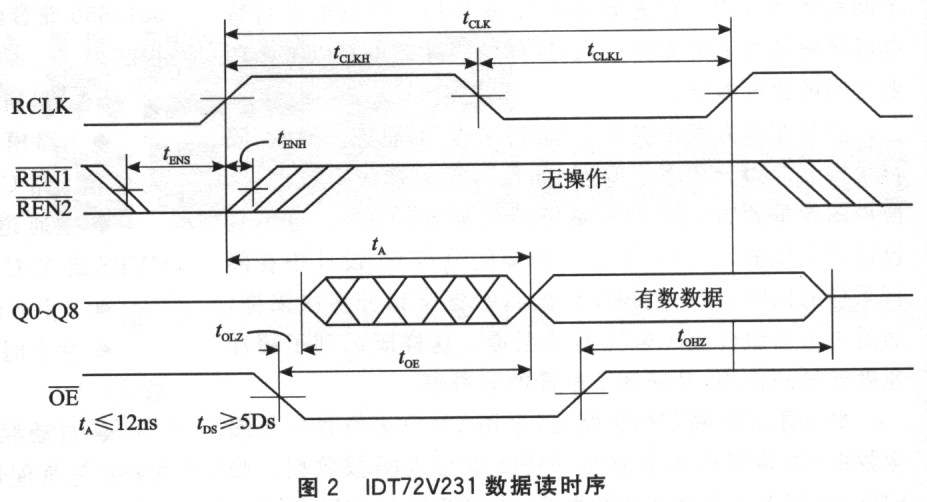

对于本设计而言,要求DSP从FIFO中将数据读出,故关键考虑DSP对IDT72V23l的读时序。图2是IDT72V31数据读出的时序。

图2中,tENS为REN1(REN2)的最短建立时间(SETUP),tDS为数据的最短建立时间(SETUP)。由图2可以看出IDT72V231与一般SRAM读时序的一个很大区别是:当RCLK上升沿到来以后,需要有一个比较长的延时tA才会有有效数据出现在总线上。此前一段时间内总线上的数据是不稳定的,并且该延时最长可达到12ns。

但是对于TMS320C6x11而言,数据的读入是在ARE信号的上升沿完成的,故这里设计的主要问題是FIFO的RCLK时钟怎样提供。本设计中采用的解决办法如下:

RCLK=!(ARE)

REN1&REN2=CEx+AOE+Address

也就是说,RCLK是由DSP的ARE信号取反得到的,而REN1和REN2信号是由DSP的AOE信号经过地址译码后提供。这样设计的TMS320C6xll与FIFO接口为了配合FIFO读出时序的要求,还必须要求DSP的读时序(主要是Setup/Strobe/Hold三个时序段)满足以下要求:

Setup≥(tENS+tSKEW)/tcyc

Strobe≥(tA+tDS)/tcyc

Strobe≥(tCLKH(min)/tcyc

Hold+Setup≥(tCLKL(min)/tcyc

Setup+Strobe+Setup≥(trc(min)/tcyc

从时序图上的数据可以看出,tENS≥5ns,tA≤12 ns,tDS≥5 ns;同时,由于IDT72V23l的要求,RCLK高电平时间(tCLKH(min)大于等于8ns、RCLK低电平时间(tCLKL(min)大于等于8 ns以及读写周期(trc(min)必须大于等于20ns。加上一定的冗余,最后计算可以得到:

Setup≥20ns

Strobe≥30 ns

Hold≥l0ns

在本设计的TMS320C6211的系统板上,EMIF的外部时钟频率是100 MHz,所以tcyc=10ns。这样可以得出DSP中CExCTL寄存器中Setup值设置为2,Strobe值设置为3,Hold值设置为1。

实际系统实现证明。通过这样的硬件接口设计后,TMS320C621l可以很稳定地从FIF0中读出数据。

2.3 隔行采样技术

由于DSP接口与FIFO的接口速度只能达到15MB/s的速度,同时当DSP把图像数据从FIFO中读出来以后还需要将数据存入其外部存储器中,这样DSP与FIFO的接口速度是完全不可能跟上解码器SAA7111A的有效数据输出速度(最低19.8 MB/s)的,所以DSP无法实时地从视频流中抓出一幅完整的图像。 因此,在DSP与SAA711lA的接口之间采用高速FIFO进行缓冲的同时,还采取了“隔行采样”的方法来缓冲速度上的差异。通过计算得出DSP每隔4行有效视频信号采1行视频数据是合理的。(把DSP将获取的数据存人其外部存储器中所需要的时间考虑在内。)

“隔行采样”的结果会导致所获取的图像垂直分辨率下降(对于PAL制式视频信号由原来的576行/幅下降到144行/幅)。为了保证图像的分辨率,本设计中将每幅图像分成连续的4次采样.在连续的4次采样中,分别抓取图像中不同的144行数据,也就是说,现在DSP抓取1幅完整幅面(720×576)大小的图像需要分4次获取,然后对数据重排组合得到完整的图像。PAL制信号是按照50Hz的场频对图像进行输出的,即每秒种可以传输25幅图像,现在由于“隔行采样”的原因,DSP每秒钟可以从PAL制信号中解码出6.25幅完整幅面大小的图像。这个速度完全可以满足很多实时系统的要求,如视频监控系统。

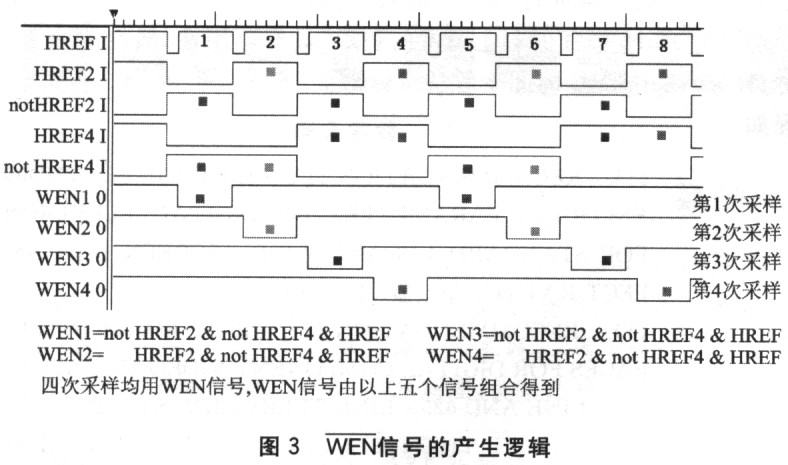

“隔行采样”功能的具体实现是由CPLD配合SAA7111A输出的同步信号(行同步、场同步信号)来完成的。由于IDT72V231(FIFO)的写入控制是通过WEN信号完成的,因此CPLD可以通过控制WEN信号来实现图像的隔四行一采样。具体WEN信号的产生逻辑如图3所示。

由图3可以清晰地看出,通过这种采样方式以后,每次输出的图像行是隔4行输出l行,而连续4次获取的图像则是一整幅图像576行图像数据中互不相同的144行数据,这四部分图像按照一定规律组合便可以得到一幅幅面为720×576像素的完整数宇图像。

另外由图3可以看出,SAA7111A每向FIFO中写入一行图像数据(需要53.3μs),DSP则有相当于4行图像数据输出的时间(约256μs)来读出这一行图像数据。因此“隔行采样”有效地缓冲了数据输出和数据读入速度上的差距。

传感器 CMOS DSP 解码器 视频监控 CPLD IDT 电路 电压 总线 RFID VHDL 仿真 Xilinx FPGA 电子 相关文章:

- 基于单片机的倾角测量系统设计 (06-27)

- 由MSP430和CC1100构成的无线传感器网络(08-01)

- 无线传感器网络自组网协议的实现方法(08-01)

- 基于SOC/IP的智能传感器设计研究(09-08)

- 单开关实现小型微处理器系统的双功能(08-10)

- 六大特点助CMOS图像传感器席卷医疗电子应用(11-13)