DSP和FPGA构成的感应发电机励磁控制系统

时间:11-25

来源:互联网

点击:

介绍了针对3/3相双绕组感应发电机设计的励磁系统,该系统由DSP和FPGA构成。给出了控制系统的接口电路和实验结果。

1 系统简介

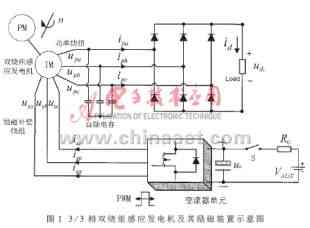

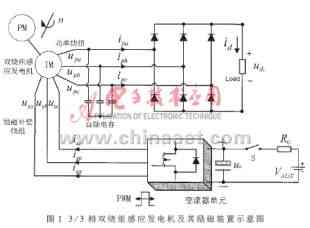

3/3相双绕组感应发电机带有两个绕组:励磁补偿绕组和功率绕组,如图1所示。励磁补偿绕组上接一个电力电子变换装置,用来提供感应发电机需要的无功功率,使功率绕组上输出一个稳定的直流电压。

图1中各参数的含义如下:

isa, isb, isc——补偿绕组中的励磁电流;

usa, usb, usc——补偿绕组相电压;

ipa, ipb, ipc——功率绕组电流;

upa, upb, upc——功率绕组相电压;

udc——二极管整流桥直流侧输出电压;

uc——变流器直流侧电容电压。

电力电子变换装置由功率器件及其驱动电路和控制电路两部分组成。功率器件选用三菱公司的智能功率模块(IPM)PM75CSA120(75A/1200V),驱动电路使用光耦HCPL4502。控制电路由DSP+FPGA构成。

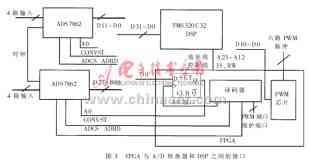

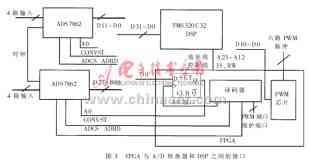

2 EPM7128与TMS320C32同外设之间的接口电路

图2所示为控制电路的接口电路。控制电路使用的DSP是TMS320C32,它是TI公司生产的第三代高性能的CMOS 32位数字信号处理器,其凭借强大的指令系统、高速数据处理能力及创新的结构,已经成为理想的工业控制用DSP器件。其主要特点是:单周期指令执行时间为50ns,具有每秒可执行2200万条指令、进行4000万次浮点运算的能力;提供了一个增强的外部存储器配置接口,具备更加灵活的存储器管理与数据处理方式。控制电路使用的FPGA器件为ALTERA公司的EPM7128,它属于高密度、高性能的CMOS EPLD器件,与ALTERA公司的MAXPLUS II开发系统软件配合,可以100%地模仿高密度的集成有各种逻辑函数和多种可编程逻辑的TTL器件。采用类似器件作为DSP的专用外围集成电路(ASIC)更为经济灵活,可以进一步降低控制系统的成本。

电压检测使用三相变压器,电流检测使用HL电流传感器。电平转换电路用来将检测到的信号转换为0~5V的电平。A/D转换器选用ADS7862。保护电路使用电压比较器311得到过压/过流故障信号。

DSP完成以下四项工作:数据的采集和处理、控制算法的完成、PWM脉冲值的计算和保护中断的处理。

FPGA完成以下三项工作:管理DSP和各种外部设备的接口;脉冲的输出和死区的产生;保护信号的处理。

3 使用FPGA实现DSP和ADS7862之间的高速接口

ADS7862是TI公司专为电机和电力系统控制而设计的A/D转换器。它的主要特点是:4个全差分输入接口,可分成两组,两个通道可同时转换;12bits并行输出;每通道的转换速率为500kHz。控制方法为:由A0线的值决定哪两个通道转换;由Convst线上的脉宽大于250ns的低电平脉冲启动转换;由CS和RD线的低电平控制数据的读出,连续两次读信号可以得到两个通道的数据。

系统中使用了两片ADS7862,它们的控制线使用同样的接口,数据线则分别和DSP的高/低16位数据线中的低12位相连接。这样DSP可以同时控制两片A/D转换器:4通道同时转换;每次读操作可以得到两路数据。

如图3所示,将A/D转换器的控制信号映射为DSP的三个外部端口:A0、ADCS(和ADRD使用一个端口)和CONVST。在FPGA中使用逻辑译码器对端口译码。利用AHDL语言编写的译码程序如下:

TABLE

A[23..12], IS, RW=>A0, ADCS, CONVST, PWM1, PWM2,

PWM3, PWM, PRO, CLEAR;

H″810″, 0, 0=> 0, 1, 1, 1, 1, 1, 1, 1, 1;

H″811″, 0, 1=> 1, 0, 1, 1, 1, 1, 1, 1, 1;

H″812″, 0, 0=> 1, 1, 0, 1, 1, 1, 1, 1, 1;

H″813″, 0, 1=> 1, 1, 1, 0, 1, 1, 1, 1, 1;

H″814″, 0, 0=> 1, 1, 1, 1, 0, 1, 1, 1, 1;

H″815″, 0, 0=> 1, 1, 1, 1, 1, 0, 1, 1, 1;

H″816″, 0, 0=> 1, 1, 1, 1, 1, 1, 0, 1, 1;

H″817″, 0, 1=> 1, 1, 1, 1, 1, 1, 1, 0, 1;

H″817″, 0, 0=> 1, 1, 1, 1, 1, 1, 1, 1, 0;

END TABLE

其中,0表示低电平,1表示高电平。RW=1表示读,RW=0表示写。

DSP对这三个端口进行操作就可以控制A/D转换器:写CONVST端口可以启动A/D转换器;读ADCS端口可以从A/D转换器中读到数据;写数据到A0端口可以设置不同的通道。

使用上述方法可以实现DSP和A/D转换器之间的无缝快速连接。

4 使用FPGA实现PWM脉冲的产生和死区的注入

FPGA除了管理DSP和外设的接口外,还完成PWM脉冲的产生和死区的注入。使用参考文献介绍的方法,将PWM芯片和死区发生器集成在FPGA中,就可以使DSP专注于复杂算法的实现,而将PWM处理交给FPGA系统,使系统运行于准并行处理状态。

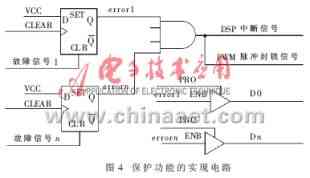

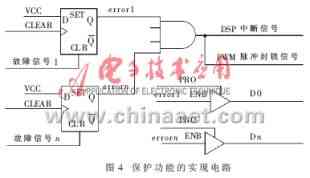

5 使用FPGA实现系统保护

为了保护发电机和IGBT功率器件,励磁控制系统提供了多种保护功能:变流器直流侧过压保护;变流器交流电流过流保护;变流器过温保护;发电机输出过压保护;IPM错误保护。

使用如图4所示的硬件逻辑来实现保护功能。当FPGA检测到相应的故障信号时,D触发器输出一个错误信号,使与门输出一个低电平,此低电平封锁住所有的PWM脉冲,并触发一个DSP的外部中断信号。当DSP响应外部中断时,可以使用PRO端口读到错误的状态位。CLEAR端口用来清除D触发器,系统因此可以重复启动。

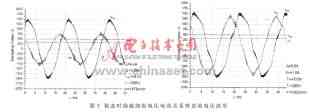

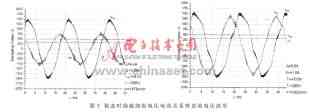

图5给出了本控制系统的实验波形图:变流器的输出电流基本为正弦;变流器侧电容电压稳定在365V;功率绕组侧输出电压稳定在510V。

1 系统简介

3/3相双绕组感应发电机带有两个绕组:励磁补偿绕组和功率绕组,如图1所示。励磁补偿绕组上接一个电力电子变换装置,用来提供感应发电机需要的无功功率,使功率绕组上输出一个稳定的直流电压。

图1中各参数的含义如下:

isa, isb, isc——补偿绕组中的励磁电流;

usa, usb, usc——补偿绕组相电压;

ipa, ipb, ipc——功率绕组电流;

upa, upb, upc——功率绕组相电压;

udc——二极管整流桥直流侧输出电压;

uc——变流器直流侧电容电压。

电力电子变换装置由功率器件及其驱动电路和控制电路两部分组成。功率器件选用三菱公司的智能功率模块(IPM)PM75CSA120(75A/1200V),驱动电路使用光耦HCPL4502。控制电路由DSP+FPGA构成。

2 EPM7128与TMS320C32同外设之间的接口电路

图2所示为控制电路的接口电路。控制电路使用的DSP是TMS320C32,它是TI公司生产的第三代高性能的CMOS 32位数字信号处理器,其凭借强大的指令系统、高速数据处理能力及创新的结构,已经成为理想的工业控制用DSP器件。其主要特点是:单周期指令执行时间为50ns,具有每秒可执行2200万条指令、进行4000万次浮点运算的能力;提供了一个增强的外部存储器配置接口,具备更加灵活的存储器管理与数据处理方式。控制电路使用的FPGA器件为ALTERA公司的EPM7128,它属于高密度、高性能的CMOS EPLD器件,与ALTERA公司的MAXPLUS II开发系统软件配合,可以100%地模仿高密度的集成有各种逻辑函数和多种可编程逻辑的TTL器件。采用类似器件作为DSP的专用外围集成电路(ASIC)更为经济灵活,可以进一步降低控制系统的成本。

电压检测使用三相变压器,电流检测使用HL电流传感器。电平转换电路用来将检测到的信号转换为0~5V的电平。A/D转换器选用ADS7862。保护电路使用电压比较器311得到过压/过流故障信号。

DSP完成以下四项工作:数据的采集和处理、控制算法的完成、PWM脉冲值的计算和保护中断的处理。

FPGA完成以下三项工作:管理DSP和各种外部设备的接口;脉冲的输出和死区的产生;保护信号的处理。

3 使用FPGA实现DSP和ADS7862之间的高速接口

ADS7862是TI公司专为电机和电力系统控制而设计的A/D转换器。它的主要特点是:4个全差分输入接口,可分成两组,两个通道可同时转换;12bits并行输出;每通道的转换速率为500kHz。控制方法为:由A0线的值决定哪两个通道转换;由Convst线上的脉宽大于250ns的低电平脉冲启动转换;由CS和RD线的低电平控制数据的读出,连续两次读信号可以得到两个通道的数据。

系统中使用了两片ADS7862,它们的控制线使用同样的接口,数据线则分别和DSP的高/低16位数据线中的低12位相连接。这样DSP可以同时控制两片A/D转换器:4通道同时转换;每次读操作可以得到两路数据。

如图3所示,将A/D转换器的控制信号映射为DSP的三个外部端口:A0、ADCS(和ADRD使用一个端口)和CONVST。在FPGA中使用逻辑译码器对端口译码。利用AHDL语言编写的译码程序如下:

TABLE

A[23..12], IS, RW=>A0, ADCS, CONVST, PWM1, PWM2,

PWM3, PWM, PRO, CLEAR;

H″810″, 0, 0=> 0, 1, 1, 1, 1, 1, 1, 1, 1;

H″811″, 0, 1=> 1, 0, 1, 1, 1, 1, 1, 1, 1;

H″812″, 0, 0=> 1, 1, 0, 1, 1, 1, 1, 1, 1;

H″813″, 0, 1=> 1, 1, 1, 0, 1, 1, 1, 1, 1;

H″814″, 0, 0=> 1, 1, 1, 1, 0, 1, 1, 1, 1;

H″815″, 0, 0=> 1, 1, 1, 1, 1, 0, 1, 1, 1;

H″816″, 0, 0=> 1, 1, 1, 1, 1, 1, 0, 1, 1;

H″817″, 0, 1=> 1, 1, 1, 1, 1, 1, 1, 0, 1;

H″817″, 0, 0=> 1, 1, 1, 1, 1, 1, 1, 1, 0;

END TABLE

其中,0表示低电平,1表示高电平。RW=1表示读,RW=0表示写。

DSP对这三个端口进行操作就可以控制A/D转换器:写CONVST端口可以启动A/D转换器;读ADCS端口可以从A/D转换器中读到数据;写数据到A0端口可以设置不同的通道。

使用上述方法可以实现DSP和A/D转换器之间的无缝快速连接。

4 使用FPGA实现PWM脉冲的产生和死区的注入

FPGA除了管理DSP和外设的接口外,还完成PWM脉冲的产生和死区的注入。使用参考文献介绍的方法,将PWM芯片和死区发生器集成在FPGA中,就可以使DSP专注于复杂算法的实现,而将PWM处理交给FPGA系统,使系统运行于准并行处理状态。

5 使用FPGA实现系统保护

为了保护发电机和IGBT功率器件,励磁控制系统提供了多种保护功能:变流器直流侧过压保护;变流器交流电流过流保护;变流器过温保护;发电机输出过压保护;IPM错误保护。

使用如图4所示的硬件逻辑来实现保护功能。当FPGA检测到相应的故障信号时,D触发器输出一个错误信号,使与门输出一个低电平,此低电平封锁住所有的PWM脉冲,并触发一个DSP的外部中断信号。当DSP响应外部中断时,可以使用PRO端口读到错误的状态位。CLEAR端口用来清除D触发器,系统因此可以重复启动。

图5给出了本控制系统的实验波形图:变流器的输出电流基本为正弦;变流器侧电容电压稳定在365V;功率绕组侧输出电压稳定在510V。

DSP FPGA 电路 电力电子 电压 电流 二极管 电容 电子 CMOS LTE 集成电路 变压器 传感器 比较器 PWM ADC IGBT 相关文章:

- F1aSh存储器在TMS320C3X系统中的应用(11-11)

- 基于PIC18F系列单片机的嵌入式系统设计(11-19)

- DSP在卫星测控多波束系统中的应用(01-25)

- 基于PCI总线的双DSP系统及WDM驱动程序设计(01-26)

- 利用Virtex-5 FPGA实现更高性能的方法(03-08)

- DSP与单片机通信的多种方案设计(03-08)