MC8051单片机IP核的FPGA实现与应用

时间:11-04

来源:互联网

点击:

2.3.3 存储器接口单元

由于采用优化结构设计,存储器采用同步结构,限制输入、输出的时序,因而存储器输入、输出数据没用寄存器寄存。

2.3.4 可选择指令

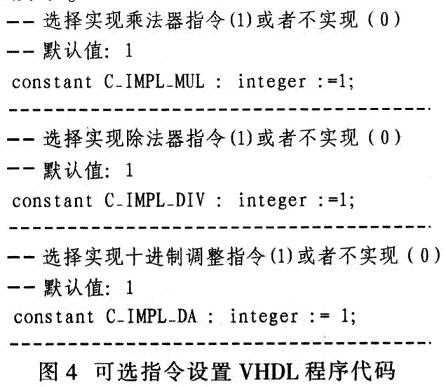

在某些场合,有些指令是用不到的,因此,通过禁用这些指令节省片上资源。这些指令有8位乘法器(MUL)、8位除法器(div)和8位十进制调整器(DA)。禁用时只需要在VHDL源程序文件MC8051_p.vh中将C_IMPL_MUL(乘法指令MUL)、C_IMPL_div(除法指令div)或C_IMPL_DA(十进制调整指令DA)的常量值设置为0即可。如果这3条可选指令没有被执行,器件可节省约10%的资源。相应的VHDL程序代码段如图4所示。

2.3.5 并行I/O端口

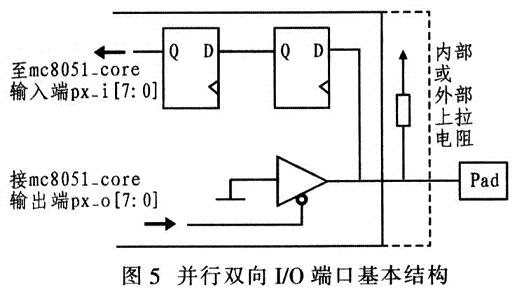

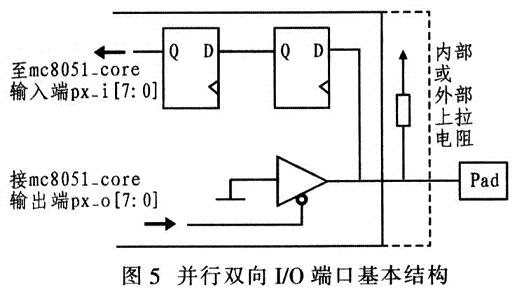

为了便于IC设计,MC805l IP核的I/0口不提供复用功能,包括4个8位输入输出口、串行接口、计数器输入端和扩展存储器接口。如果要想将。MC8051 IP核的并行I/O端口改为双向I/0端口,设计时可以添加一些外围逻辑电路来实现。其基本电路结构如图5所示。图中的2个D触发器起同步输入信号的作用(mc805l_core的输入I/O不做同步处理),也可以不用。上拉电阻是必要的,因为I/0端口输出高电平是靠上拉电阻实现的。

2.4 MC8051其他说明

(1)MC8051 IP核的定时器和串口波特率的计算与标准8051一样,由系统时钟经12倍分频获得计数时钟。

(2)外部中断信号是经两级寄存器做同步处理后输入的。

(3)MC805l_core的输入I/0不做同步处理,必要时可自行添加,如图5所示。

(4)写应用程序时,I/O端口如果没有做成双向端口,而是输入和输出分开的,应特别注意诸如Pl=一P1、P1^O=P1^0这样的I/0取反操作是无效的,因为读回的值不是I/O寄存器的值,而是输入引脚的状态。

3 MC8051的RTL封装

利用综合工具Synplify Pro软件实现对MC8051核的RTL封装,从而生成最终所需的MC8051 IP核(.vqm文件)。

3.1 MC8051存储模块生成

MC8051中所需的存储模块:内部RAM、扩展RAM和ROM。其中内部RAM和ROM是必要的,内部RAM固定为128字节,ROM最大可选64 K字节,鉴于FPGA片上RAM资源有限,这里选用4 K字节(可根据需要修改);扩展RAM是可选,最大也可以达到64 K字节,这里选用2 K字节。

由于采用Altera公司的FPGA来实现,所以可以利用Al—tera公司的集成开发环境Quartus II来创建ROM、RAM模块。在具体的FPGA实现中,可根据不同厂家的器件,用厂家提供的工具来生成ROM和RAM,或者采用HDL描述实现。

3.2 MC8051 IP核RTL封装

由于用的MC8051 IP核源代码顶层设计文件中的存储模块(RAM、ROM)是仿真时使用的,实际应用设计时,必须改成实际应用中用到的RAM、ROM模块(也就是前面生成的RAM、ROM模块)。

(1)打开源代码中的mc805l_p.vhd程序包文件,将原文件中的RAM(包括内部RAM、扩展RAM)、ROM元件例化语句全部替换成实际应用设计的程序代码;

(2)打开源代码中的mc805l_top_stru.vhd文件,将原文件中的RAM(包括内部RAM、扩展RAM)ROM元件端口映射语句全部修改成应用设计的端口映射。因为实际应用中RAM、ROM的容量与MC8051核中存储器容量不一致及控制信号的差异,需要修改实际应用中RAM、ROM的地址线及控制信号线的端口映射。

(3)新建Synplify Pro工程,将修改后的MC8051 IP核的VHDL文件添加到工程中。选择综合的目标FPGA器件,设置相关综合参数,生成MC8051 IP核的RTL封装文件.vqm,其综合后的RTL图如图6所示。

(4)因为VHDL文件编译是有顺序的,所以在向SynplifyPro工程添加VHDL源代码文件时,应注意的是:首先添加MC805l_p.vhd文件,然后添加其他文件,最后添加mc805l_top_.vhd和mc8051_top_strut.vhd文件。注意文件名后为_cfg.vhd的配置文件可以不添加到工程中,前面生成的RAM、ROM源代码文件也不必添加到工程里面。

(5)综合编译成功后,需要检查顶层设计是否正确,这时可通过RTL图来检查。在RTL图中可看到MC8051 IP核的顶层结构图。在RTL图中主要检查ROM、RAM模块的连线是否正确,是否符合实际应用设计。

4 MC8051 IP核应用构建

采用Ahera公司的FPGA实现,可以利用Ahera公司的集成开发环境0uartus II构建实际应用系统。

4.1 MC8051硬件系统构建

在QuartusⅡ中新建应用工程,创建顶层图形设计文件并保存。

(1)将MC8051 IP核进行RTL封装时用Quartus II创建的RAM、ROM模块文件添加到工程中;

(2)在工程中调用FPGA自带的PLL数字锁相环模块,将目标系统板上的时钟调整到MC805l IP核的应用时钟频率。MC805l IP核经Quartus II综合编译后,查看时序分析报告,其最高运行频率为18.96 MHz(每次编译都可能不同,I/0分配不同结果可能不同),因此系统时钟不能超过时序报告的时钟最高频率(即fmax)。可以选择18 MHz,利用PLL对目标系统板上的时钟进行分频;

(3)将Synplifyr Pro综合生成的RTL封装文件.vqm拷贝到Quartus II工程文件目录下,并添加到工程中。然后再将添加.vqm文件生成MC8051_top.bsf图形文件;

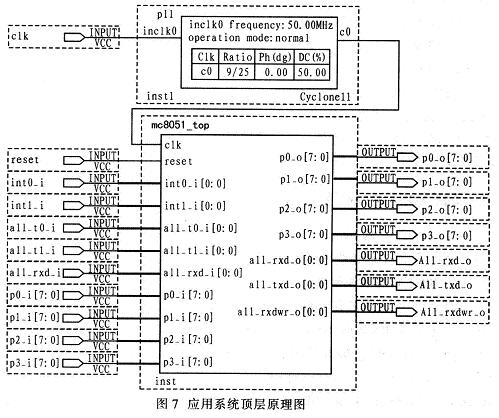

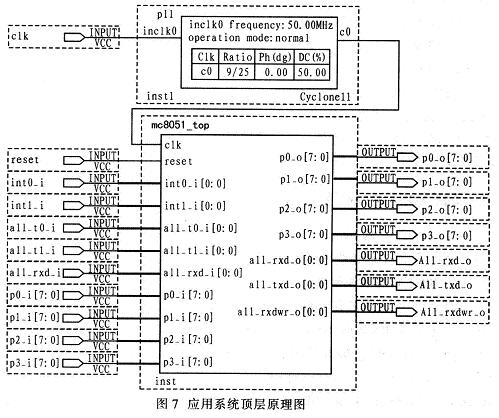

(4)打开创建的应用设计顶层图形设计文件,将前面生成的PLL模块、MC8051_top模块添加到顶层设计文件中。添加输入/输出引脚,并对引脚命名,连接引脚与各模块.设置相关编译参数。生成FPGA的配置文件*.sof。其实际应用系统顶层原理图如图7所示。

可将并行I/O端口设计成双向I/O端口,以节约FPGA的引脚资源,其方法参见图5。根据实际应用的需要,利用FPGA剩余的资源,添加其他逻辑模块,与MC8051 core模块、PLL模块一起构成应用系统。这里只讨论MC8051 IP核的FPGA实现。

由于采用优化结构设计,存储器采用同步结构,限制输入、输出的时序,因而存储器输入、输出数据没用寄存器寄存。

2.3.4 可选择指令

在某些场合,有些指令是用不到的,因此,通过禁用这些指令节省片上资源。这些指令有8位乘法器(MUL)、8位除法器(div)和8位十进制调整器(DA)。禁用时只需要在VHDL源程序文件MC8051_p.vh中将C_IMPL_MUL(乘法指令MUL)、C_IMPL_div(除法指令div)或C_IMPL_DA(十进制调整指令DA)的常量值设置为0即可。如果这3条可选指令没有被执行,器件可节省约10%的资源。相应的VHDL程序代码段如图4所示。

2.3.5 并行I/O端口

为了便于IC设计,MC805l IP核的I/0口不提供复用功能,包括4个8位输入输出口、串行接口、计数器输入端和扩展存储器接口。如果要想将。MC8051 IP核的并行I/O端口改为双向I/0端口,设计时可以添加一些外围逻辑电路来实现。其基本电路结构如图5所示。图中的2个D触发器起同步输入信号的作用(mc805l_core的输入I/O不做同步处理),也可以不用。上拉电阻是必要的,因为I/0端口输出高电平是靠上拉电阻实现的。

2.4 MC8051其他说明

(1)MC8051 IP核的定时器和串口波特率的计算与标准8051一样,由系统时钟经12倍分频获得计数时钟。

(2)外部中断信号是经两级寄存器做同步处理后输入的。

(3)MC805l_core的输入I/0不做同步处理,必要时可自行添加,如图5所示。

(4)写应用程序时,I/O端口如果没有做成双向端口,而是输入和输出分开的,应特别注意诸如Pl=一P1、P1^O=P1^0这样的I/0取反操作是无效的,因为读回的值不是I/O寄存器的值,而是输入引脚的状态。

3 MC8051的RTL封装

利用综合工具Synplify Pro软件实现对MC8051核的RTL封装,从而生成最终所需的MC8051 IP核(.vqm文件)。

3.1 MC8051存储模块生成

MC8051中所需的存储模块:内部RAM、扩展RAM和ROM。其中内部RAM和ROM是必要的,内部RAM固定为128字节,ROM最大可选64 K字节,鉴于FPGA片上RAM资源有限,这里选用4 K字节(可根据需要修改);扩展RAM是可选,最大也可以达到64 K字节,这里选用2 K字节。

由于采用Altera公司的FPGA来实现,所以可以利用Al—tera公司的集成开发环境Quartus II来创建ROM、RAM模块。在具体的FPGA实现中,可根据不同厂家的器件,用厂家提供的工具来生成ROM和RAM,或者采用HDL描述实现。

3.2 MC8051 IP核RTL封装

由于用的MC8051 IP核源代码顶层设计文件中的存储模块(RAM、ROM)是仿真时使用的,实际应用设计时,必须改成实际应用中用到的RAM、ROM模块(也就是前面生成的RAM、ROM模块)。

(1)打开源代码中的mc805l_p.vhd程序包文件,将原文件中的RAM(包括内部RAM、扩展RAM)、ROM元件例化语句全部替换成实际应用设计的程序代码;

(2)打开源代码中的mc805l_top_stru.vhd文件,将原文件中的RAM(包括内部RAM、扩展RAM)ROM元件端口映射语句全部修改成应用设计的端口映射。因为实际应用中RAM、ROM的容量与MC8051核中存储器容量不一致及控制信号的差异,需要修改实际应用中RAM、ROM的地址线及控制信号线的端口映射。

(3)新建Synplify Pro工程,将修改后的MC8051 IP核的VHDL文件添加到工程中。选择综合的目标FPGA器件,设置相关综合参数,生成MC8051 IP核的RTL封装文件.vqm,其综合后的RTL图如图6所示。

(4)因为VHDL文件编译是有顺序的,所以在向SynplifyPro工程添加VHDL源代码文件时,应注意的是:首先添加MC805l_p.vhd文件,然后添加其他文件,最后添加mc805l_top_.vhd和mc8051_top_strut.vhd文件。注意文件名后为_cfg.vhd的配置文件可以不添加到工程中,前面生成的RAM、ROM源代码文件也不必添加到工程里面。

(5)综合编译成功后,需要检查顶层设计是否正确,这时可通过RTL图来检查。在RTL图中可看到MC8051 IP核的顶层结构图。在RTL图中主要检查ROM、RAM模块的连线是否正确,是否符合实际应用设计。

4 MC8051 IP核应用构建

采用Ahera公司的FPGA实现,可以利用Ahera公司的集成开发环境0uartus II构建实际应用系统。

4.1 MC8051硬件系统构建

在QuartusⅡ中新建应用工程,创建顶层图形设计文件并保存。

(1)将MC8051 IP核进行RTL封装时用Quartus II创建的RAM、ROM模块文件添加到工程中;

(2)在工程中调用FPGA自带的PLL数字锁相环模块,将目标系统板上的时钟调整到MC805l IP核的应用时钟频率。MC805l IP核经Quartus II综合编译后,查看时序分析报告,其最高运行频率为18.96 MHz(每次编译都可能不同,I/0分配不同结果可能不同),因此系统时钟不能超过时序报告的时钟最高频率(即fmax)。可以选择18 MHz,利用PLL对目标系统板上的时钟进行分频;

(3)将Synplifyr Pro综合生成的RTL封装文件.vqm拷贝到Quartus II工程文件目录下,并添加到工程中。然后再将添加.vqm文件生成MC8051_top.bsf图形文件;

(4)打开创建的应用设计顶层图形设计文件,将前面生成的PLL模块、MC8051_top模块添加到顶层设计文件中。添加输入/输出引脚,并对引脚命名,连接引脚与各模块.设置相关编译参数。生成FPGA的配置文件*.sof。其实际应用系统顶层原理图如图7所示。

可将并行I/O端口设计成双向I/O端口,以节约FPGA的引脚资源,其方法参见图5。根据实际应用的需要,利用FPGA剩余的资源,添加其他逻辑模块,与MC8051 core模块、PLL模块一起构成应用系统。这里只讨论MC8051 IP核的FPGA实现。

单片机 嵌入式 FPGA EDA MCU 电路 VHDL 51单片机 仿真 电阻 Altera Quartus C语言 相关文章:

- 单片机智能频率信号装置(11-25)

- 单片机在医学信号检测仪中的应用(02-07)

- 单片机应用编程技巧(02-25)

- DSP与单片机通信的多种方案设计(03-08)

- 单片机与PC机串行通信的实现方法 (02-25)

- 单片机与PC通信的简化接口 (05-11)