TMS320C3X串口扩展技术

时间:06-27

来源:互联网

点击:

TMS320C3X是TI公司生产的第三代数字信号处理器,目前已相继推出C30、C31、C32和VC33等四种类型,由于其性价比高而被广泛应用于各个领域中。

TMS320C3X是一种32bit的浮点DSP,其程序、数据和外设地址都映射在同一存储空间,并有丰富的寻址方式和较大的寻址空间,因此对外设的访问非常灵活方便。但在实际应用中往往也要考虑一些不利因素:一是外部总线速度高、地址线宽,因此增加外设时对接口电路的时序要求较高,且电路连接较复杂;二是频繁的外设访问操作易产生流水线冲突而影响整体性能。DSP的串口有较强的设备管理能力,与外设连接也很简单?因此成为DSP与低速外设交换数据的首选。但在TMS320C3X系列中,除TMS320C30提供两个串口外,其它几种芯片都只有一个串口,在很多情况下限制了这些芯片的进一步使用。本文针对C3X串口的特点,以TMS320C3X与TLC3204X连接为例,设计了一种串口扩展方法。

1 TMS320C3X与TLC3204X连接简介

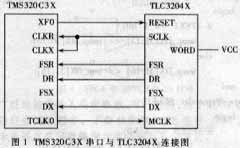

TLC3204X是TI公司生产的话带模数接口芯片(AIC),可与TMS320C3X等多种DSP芯片的串口直接相连,其A/D、D/A转换精度为14bit,按16bit方式传送,其中两位用于芯片控制和启动辅助通信[1]。图1是TLC3204X与TMS320C3X串口的连接图[2]。AIC与DSP通过DX和DR交换数据,AIC的主时钟信号(MCLK) 由DSP的定时器0提供,而AIC的移位脉冲(SCLK)作为串口的发送时钟(CLKX)和接收时钟(CLKR),发送和接收帧同步信号分别由AIC的FSX和FSR提供。DSP串口以16位变速传送方式工作,AIC按字方式传送数据。

2 TMS320C3X串口扩展原理

一般而言,外设数据字长较短,而TMS320C3X串口数据字长可灵活配置。利用这一特点,只要增设少量的外部电路,就能在现有基础上扩展接口。在本例中,TLC3204X数据是16bit字长,因此只要将TMS320C3X串口设定为32bit传送方式,每个TLC3204X各占用16bit,就能将该串口一分为二。图2为TMS320C3X与两片TLC3204X的连接示意图,其接口电路的设计可分为发送和接收两部分的设计。

2.1 发送接口电路

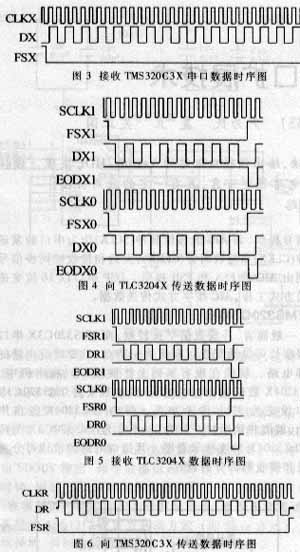

该接口应完成两个任务。一是接收来自TMS320C3X串口的32bit数据,由TMS320C3X提供移位脉冲CLKX,帧同步信号(FSX)由接口电路提供,其时序如图3所示。二是将32bit数据分解为两个16bit数据,然后再传送到两个TLC3204X芯片,由TLC3204X芯片提供发送时钟SCLK和帧同步信号FSX以及完成信号EODX。传送时序如图4所示。

2.2 接收接口电路

该接口电路是发送接口电路的逆过程,其时序如图5和图6所示。

3 接口电路的实现

Verilog HDL 3?描述硬件单元的结构简单且易读,是当前最流行和通用的两种硬件描述语言之一,得到众多EDA工具的支持,因此利用该语言进行电路设计可以节省开发成本并缩短开发周期。

3.1 接口电路的顶层Verilog HDL描述

module DSP_TLC(SCLK1, DX1, FSX1, EODX1, DR1, FSR1,

EODR1,SCLK0, DX0, FSX0, EODX0, DR0, FSR0, EODR0,

CLKX, DX, FSX, DR, FSR, RESET);

input FSX1, EODX1, FSX0, EODX0, DX, CLKX, RESET;

output FSX, DX1, DX0?

input DR1, SCLK1, FSR1, EODR1, DR0, SCLK0, FSR0, EODR0;

output FSR, DR?

Transmit TRA(DX1, SCLK1, FSX1, EODX1, DX0, SCLK0, FSX0, EODX0, DX, CLKX, FSX, RESET);

Receive REC(DR1, SCLK1, FSR1, EODR1, DR0, SCLK0, FSR0, EODR0, DR, CLKX, FSR, RESET);

endmodule

3.2 发送接口电路的Verilog HDL描述

module Transmit(DX1, SCLK1, FSX1, EODX1, DX0, SCLK0,FSX0, EODX0, DX, CLKX, FSX, RESET);

input SCLK1, FSX1, EODX1, SCLK0, FSX0, EODX0;

input DX, CLKX, RESET?

output FSX, DX1, DX0;

reg [31:0] tmp_DX, temp_DX;

reg [1:0] tmp_EODX;

reg [4:0] DX_count;

assign DX1 = temp_DX[31];

assign DX0 = temp_DX[15]?

assign FSX = (tmp_EODX == 2'b11) ? 1'b0 : 1'b1;

always @(negedge CLKX or negedge RESET)

begin

if (RESET == 1′b0)

begin

tmp_DX <= 32'b0?

tmp_EODX <= 2'b0?

DX_count <= 5'b0?

end

else

begin

if (EODX1 == 1'b0) tmp_EODX[1] <= 1'b1;

if (EODX0 == 1'b0) tmp_EODX[0] <= 1'b1?

if (DX_count == 5'b11111) tmp_EODX <= 2'b0?

if (FSX == 1'b0)

begin

tmp_DX[0] <= DX?

tmp_DX[31:1] <= tmp_dx[30:0]?

DX_count <= DX_count + 1?

end

else

DX_count <= 5'b0?

end

end

always @(posedge SCLK1)

begin

if (FSX1 == 1'b0)

temp_DX[31:17] <= temp_DX[30:16]?

else

temp_DX[31:16] <= tmp_DX[31:16]?

end

always @(posedge SCLK0)

begin

if (FSX0 == 1'b0)

temp_DX[15:1] <= temp_DX[14:0];

else

temp_DX[15:0] <= tmp_DX[15:0]?

end

endmodule

3.3 接收接口电路的Verilog HDL描述

module Receive(DR1, SCLK1, FSR1, EODR1, DR0, SCLK0, FSR0, EODR0, DR, CLKR, FSR, RESET);

input DR1, SCLK1, FSR1, EODR1, DR0, SCLK0, FSR0, EODR0;

input CLKR, RESET;

output FSR, DR;

reg [31:0] tmp_DR, temp_DR;

reg [1:0] tmp_EODR;

reg [4:0] DR_count;

assign DR = (FSR == 1'b0) ? tmp_DR[31] : 1'bz;

assign FSR = (tmp_EODR == 2'b11) ? 1'b0 : 1'b1;

always @(posedge CLKR or negedge RESET)

begin

if (RESET == 1'b0)

begin

tmp_DR <= 32'b0;

tmp_EODR <= 2'b0;

DR_count <= 5'b0;

end

else

begin

if (EODR1 == 1'b0) tmp_EODR[1] <= 1'b1;

if (EODR0 == 1'b0) tmp_EODR[0] <= 1'b1;

if (DR_count == 5'b11111) tmp_EODR <= 2'b0;

if (FSR == 1'b0)

begin

tmp_DR[31:1] <= tmp_DR[30:0]?

DR_count <= DR_count + 1;

end

else

begin

DR_count <= 5'b0;

Tmp_DR <= temp_DR;

end

end

end

always @(negedge SCLK1)

begin

if (FSR1 == 1'b0)

begin

temp_DR[16] <= DR1?

temp_DR[31:17] <= temp_DR[30:16];

end

end

always @(negedge SCLK0)

begin

if (FSR0 == 1'b0)

begin

temp_DR[0] <= DR0;

temp_DR[15:1] <= temp_DR[14:0];

end

end

endmodule

本文介绍了一种TMS320C3X串口扩展技术,并用Verilog HDL语言进行了描述,利用中小容量的CPLD或FPGA就能实现该接口功能。该电路已被作者应用到实际系统中,仿真和实践证明该接口稳定可靠,具有一定的应用价值。

TMS320C3X是一种32bit的浮点DSP,其程序、数据和外设地址都映射在同一存储空间,并有丰富的寻址方式和较大的寻址空间,因此对外设的访问非常灵活方便。但在实际应用中往往也要考虑一些不利因素:一是外部总线速度高、地址线宽,因此增加外设时对接口电路的时序要求较高,且电路连接较复杂;二是频繁的外设访问操作易产生流水线冲突而影响整体性能。DSP的串口有较强的设备管理能力,与外设连接也很简单?因此成为DSP与低速外设交换数据的首选。但在TMS320C3X系列中,除TMS320C30提供两个串口外,其它几种芯片都只有一个串口,在很多情况下限制了这些芯片的进一步使用。本文针对C3X串口的特点,以TMS320C3X与TLC3204X连接为例,设计了一种串口扩展方法。

1 TMS320C3X与TLC3204X连接简介

TLC3204X是TI公司生产的话带模数接口芯片(AIC),可与TMS320C3X等多种DSP芯片的串口直接相连,其A/D、D/A转换精度为14bit,按16bit方式传送,其中两位用于芯片控制和启动辅助通信[1]。图1是TLC3204X与TMS320C3X串口的连接图[2]。AIC与DSP通过DX和DR交换数据,AIC的主时钟信号(MCLK) 由DSP的定时器0提供,而AIC的移位脉冲(SCLK)作为串口的发送时钟(CLKX)和接收时钟(CLKR),发送和接收帧同步信号分别由AIC的FSX和FSR提供。DSP串口以16位变速传送方式工作,AIC按字方式传送数据。

2 TMS320C3X串口扩展原理

一般而言,外设数据字长较短,而TMS320C3X串口数据字长可灵活配置。利用这一特点,只要增设少量的外部电路,就能在现有基础上扩展接口。在本例中,TLC3204X数据是16bit字长,因此只要将TMS320C3X串口设定为32bit传送方式,每个TLC3204X各占用16bit,就能将该串口一分为二。图2为TMS320C3X与两片TLC3204X的连接示意图,其接口电路的设计可分为发送和接收两部分的设计。

2.1 发送接口电路

该接口应完成两个任务。一是接收来自TMS320C3X串口的32bit数据,由TMS320C3X提供移位脉冲CLKX,帧同步信号(FSX)由接口电路提供,其时序如图3所示。二是将32bit数据分解为两个16bit数据,然后再传送到两个TLC3204X芯片,由TLC3204X芯片提供发送时钟SCLK和帧同步信号FSX以及完成信号EODX。传送时序如图4所示。

2.2 接收接口电路

该接口电路是发送接口电路的逆过程,其时序如图5和图6所示。

3 接口电路的实现

Verilog HDL 3?描述硬件单元的结构简单且易读,是当前最流行和通用的两种硬件描述语言之一,得到众多EDA工具的支持,因此利用该语言进行电路设计可以节省开发成本并缩短开发周期。

3.1 接口电路的顶层Verilog HDL描述

module DSP_TLC(SCLK1, DX1, FSX1, EODX1, DR1, FSR1,

EODR1,SCLK0, DX0, FSX0, EODX0, DR0, FSR0, EODR0,

CLKX, DX, FSX, DR, FSR, RESET);

input FSX1, EODX1, FSX0, EODX0, DX, CLKX, RESET;

output FSX, DX1, DX0?

input DR1, SCLK1, FSR1, EODR1, DR0, SCLK0, FSR0, EODR0;

output FSR, DR?

Transmit TRA(DX1, SCLK1, FSX1, EODX1, DX0, SCLK0, FSX0, EODX0, DX, CLKX, FSX, RESET);

Receive REC(DR1, SCLK1, FSR1, EODR1, DR0, SCLK0, FSR0, EODR0, DR, CLKX, FSR, RESET);

endmodule

3.2 发送接口电路的Verilog HDL描述

module Transmit(DX1, SCLK1, FSX1, EODX1, DX0, SCLK0,FSX0, EODX0, DX, CLKX, FSX, RESET);

input SCLK1, FSX1, EODX1, SCLK0, FSX0, EODX0;

input DX, CLKX, RESET?

output FSX, DX1, DX0;

reg [31:0] tmp_DX, temp_DX;

reg [1:0] tmp_EODX;

reg [4:0] DX_count;

assign DX1 = temp_DX[31];

assign DX0 = temp_DX[15]?

assign FSX = (tmp_EODX == 2'b11) ? 1'b0 : 1'b1;

always @(negedge CLKX or negedge RESET)

begin

if (RESET == 1′b0)

begin

tmp_DX <= 32'b0?

tmp_EODX <= 2'b0?

DX_count <= 5'b0?

end

else

begin

if (EODX1 == 1'b0) tmp_EODX[1] <= 1'b1;

if (EODX0 == 1'b0) tmp_EODX[0] <= 1'b1?

if (DX_count == 5'b11111) tmp_EODX <= 2'b0?

if (FSX == 1'b0)

begin

tmp_DX[0] <= DX?

tmp_DX[31:1] <= tmp_dx[30:0]?

DX_count <= DX_count + 1?

end

else

DX_count <= 5'b0?

end

end

always @(posedge SCLK1)

begin

if (FSX1 == 1'b0)

temp_DX[31:17] <= temp_DX[30:16]?

else

temp_DX[31:16] <= tmp_DX[31:16]?

end

always @(posedge SCLK0)

begin

if (FSX0 == 1'b0)

temp_DX[15:1] <= temp_DX[14:0];

else

temp_DX[15:0] <= tmp_DX[15:0]?

end

endmodule

3.3 接收接口电路的Verilog HDL描述

module Receive(DR1, SCLK1, FSR1, EODR1, DR0, SCLK0, FSR0, EODR0, DR, CLKR, FSR, RESET);

input DR1, SCLK1, FSR1, EODR1, DR0, SCLK0, FSR0, EODR0;

input CLKR, RESET;

output FSR, DR;

reg [31:0] tmp_DR, temp_DR;

reg [1:0] tmp_EODR;

reg [4:0] DR_count;

assign DR = (FSR == 1'b0) ? tmp_DR[31] : 1'bz;

assign FSR = (tmp_EODR == 2'b11) ? 1'b0 : 1'b1;

always @(posedge CLKR or negedge RESET)

begin

if (RESET == 1'b0)

begin

tmp_DR <= 32'b0;

tmp_EODR <= 2'b0;

DR_count <= 5'b0;

end

else

begin

if (EODR1 == 1'b0) tmp_EODR[1] <= 1'b1;

if (EODR0 == 1'b0) tmp_EODR[0] <= 1'b1;

if (DR_count == 5'b11111) tmp_EODR <= 2'b0;

if (FSR == 1'b0)

begin

tmp_DR[31:1] <= tmp_DR[30:0]?

DR_count <= DR_count + 1;

end

else

begin

DR_count <= 5'b0;

Tmp_DR <= temp_DR;

end

end

end

always @(negedge SCLK1)

begin

if (FSR1 == 1'b0)

begin

temp_DR[16] <= DR1?

temp_DR[31:17] <= temp_DR[30:16];

end

end

always @(negedge SCLK0)

begin

if (FSR0 == 1'b0)

begin

temp_DR[0] <= DR0;

temp_DR[15:1] <= temp_DR[14:0];

end

end

endmodule

本文介绍了一种TMS320C3X串口扩展技术,并用Verilog HDL语言进行了描述,利用中小容量的CPLD或FPGA就能实现该接口功能。该电路已被作者应用到实际系统中,仿真和实践证明该接口稳定可靠,具有一定的应用价值。

DSP 总线 电路 Verilog EDA CPLD FPGA 仿真 相关文章:

- F1aSh存储器在TMS320C3X系统中的应用(11-11)

- 基于PIC18F系列单片机的嵌入式系统设计(11-19)

- DSP在卫星测控多波束系统中的应用(01-25)

- 基于PCI总线的双DSP系统及WDM驱动程序设计(01-26)

- 利用Virtex-5 FPGA实现更高性能的方法(03-08)

- DSP与单片机通信的多种方案设计(03-08)