基于Nios II的LED显示屏控制器设计

时间:08-19

来源:互联网

点击:

目前,LED大屏幕显示系统按数据传输方式分为两类:一是同步实时显示,即计算机显示系统的内容同时在LED视频显示屏上显示;二是异步通信更新数据显示,计算机通过USB、通用串行接口、以太网等通信方式将数据传送给独立视频源显示屏。通常,异步通信控制方式只能将屏幕作为一个完整的区域显示,对于较大屏幕的显示系统,有时需要将整屏分为若干个窗口分别显示不同的内容,且内容的更新只是某一个或几个窗口。针对这种情况,本文提出了一种基于Nios II 32位处理器的设计方案,能有效地实现单屏幕多窗口的任意位置显示,使得显示方式更加灵活方便。

1 系统总体设计

1.1 系统硬件结构

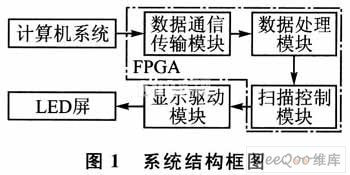

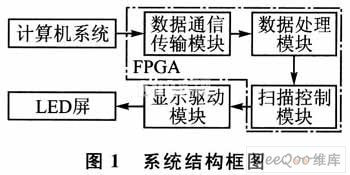

LED显示系统主要由计算机系统、数据通信传输模块、数据处理模块、扫描控制模块、显示驱动模块和LED屏构成,如图1所示。

计算机系统将要显示的点阵信息通过RS485串行接口送往存储设备,数据处理模块读取存储设备的数据并进行各种特技显示处理,将处理好的数据送往扫描控制模块,显示驱动模块接收到扫描控制模块的数据后送往LED屏上显示。数据通信传输模块、数据处理模块、扫描控制模块3部分均在FPGA上实现,即构成LED异步控制器。

1.2 系统软件方案

软件基于Nios II IDE开发完成,应用程序基于μC/OS-II实时操作系统实现。软件程序主要由2个任务和1个定时器中断服务程序组成,任务问采用信号量的方式进行通信。任务1将上位机传送到CF卡存储设备的数据写入内存中;任务2从内存中读取数据并进行分析处理,把分析处理完的数据送往扫描控制模块。为了充分利用μC/OS-II的实时性和多任务的特点,采用嵌入式文件系统进行数据管理。

2 控制系统硬件部分设计

数据处理模块由Nios II软核CPU、1片SDRAM和1片Flash存储器组成。Nios II软核CPU是整个控制器的核心,负责数据的处理;sDRAM作为CPU处理数据时的缓存使用;Flash存储器用于存储点阵信息数据和LED屏显示控制参数。

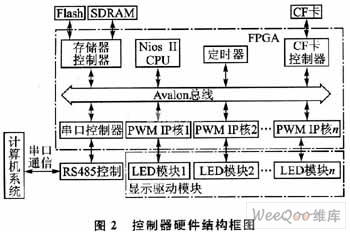

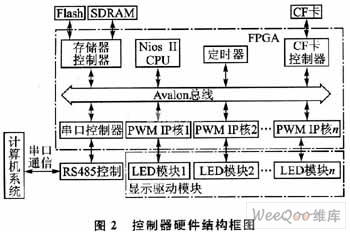

扫描控制模块由用户自定义的PWM IP核和显存组成。显存采用1片SRAM实现,用来保存当前显示的一帧点阵信息数据。PWM模块通过Aval-on总线和Nios IICPU连接,将从CPU接收到的数据按指定地址写入显存,然后再按一定的寻址方式从显存中读取点阵信息数据进行扫描。串口控制器、定时器、存储器控制器、CF卡控制器通过SOPC Builder软件定制集成IP核自动生成。本控制器的硬件结构如图2所示。

3 控制系统软件部分设计

控制系统软件是基于实时操作系统μC/OS-II进行设计的。该操作系统利用高效任务调度算法调度每个任务,而每个窗口的显示由单个任务完成。主函数创建了2个任务:一个用于读取CF卡数据;另一个用于接收来自不同显示模块的场景数据和播放显示文件。

3.1 数据结构

数据在存储器中的存储形式直接影响数据的存取速度和控制的复杂度。本系统对显存中的数据和缓存中的数据均重新组织,降低了数据处理和扫描控制的复杂度。

3.1.1 显存数据的组织

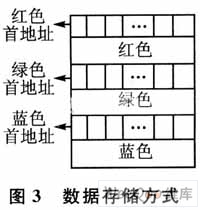

LED显示屏的每个像素点都包括红、绿、蓝3种基色,每种颜色的灰度级均为256级(即由8位数据对像素点灰度级进行编码),故每个像素点需要占用3字节的存储空间。显示时,每个像素的红管、绿管、蓝管是同时点亮的,也就是说,3种颜色的数据是并行上屏的。可将红、绿、蓝3种颜色对应的数据分开存储,以方便操作。数据存储方式如图3所示。同一种颜色的数据集中存放在某个区域中,区域的首地址作为该颜色的基址。在进行数据存放时,每个像素点只需给出相对变化地址(变址),加上不同颜色的基址就可以在3个区域中找到对应点的视频数据。

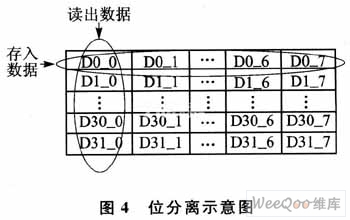

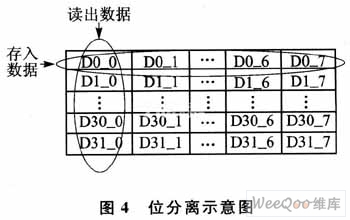

LED显示屏灰度的实现方法是分权重扫描的。这样就需要对颜色数据进行位分离,然后同权重的位重新组合。为了方便操作,存储时把图3所示的每个区再分为8个权重区,所有同权重的数值集中放于对应的权重区中。所谓位分离,就是把数据的高低位按权重分开,然后重新组织。位分离在可编程逻辑器件中比较容易实现,可以划出一块逻辑矩阵,操作时横向存入,纵向读出即可。位分离示意图如图4所示。

3.1.2 缓存数据的组织

若要进行特技效果显示,则当前显示的数据帧和下一个数据帧存在着某种变换关系。由于CPU只能对显存进行写操作,所以需在缓存中划分出一块大小和显存相等、地址一一对应的区域screen,用于存储当前显示的数据帧信息。如果各窗口之间存在重叠现象,且特技数据处理运算直接在screen区域进行,则窗口重叠部分信息可能发生混乱。故在缓存中再为每一个窗口划分出一块存取空间(part 1,part 2,…,part n),用于存储本窗口显示的前一帧数据信息。在特技数据处理运算时,先在part区域处理各窗口的数据信息,将转换完的数据送往各窗口在screen区域中所对应地址的存取空间,最后将screen中的数据写入地址对应的显存。

3.2 读取CF卡软件设计

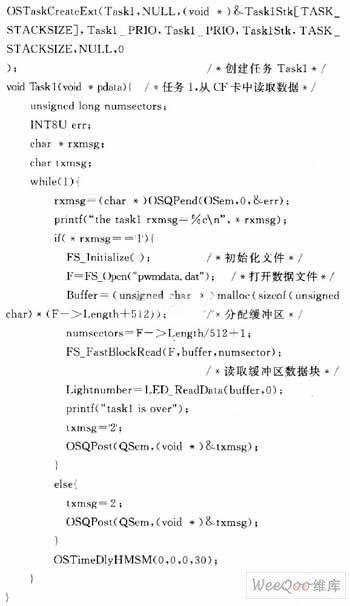

任务1负责将CF卡上的数据读取到SDRAM中,供其他任务使用。在程序中使用了1个指针(*pwmdata),为数据文件在SDRAM中分配空间。在文件系统初始化时,首先调用CF卡初始化函数IDE_initialize()判断CF卡是否存在。若存在,则读取文件系统的基本信息。通过调用函数FS_SearchFile(char*FName,FS_TFile*R,unsigned char dir)来查找需要读取的文件是否存在,若存在,则通过指针(*pwmdata)为数据文件在SDRAM中分配一个缓冲区。读取时,每次读取一个扇区,直到将数据全部读取到sDRAM中。

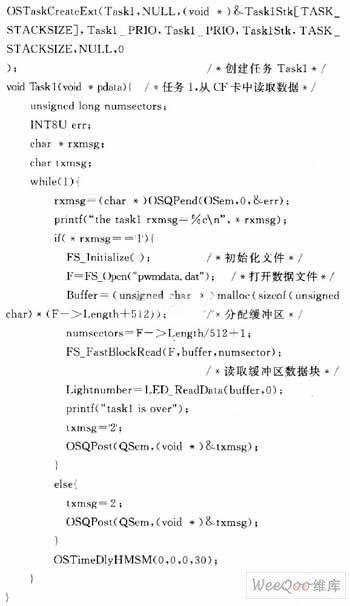

部分程序源码如下:

3.3软件总体设计

基于以上数据结构,软件设计的流程如图5所示。系统首先进行初始化操作,然后从Flash中读取显示屏参数,进行参数初始化。接着建立任务TaskControt(),其优先级比各窗口显示任务都要高,主要用于实时管理各窗口显示任务,每个窗口的显示由单个窗口显示任务来控制。窗口显示任务根据各窗口显示方式的不同,在其对应的part存储区域进行下一帧数据的处理运算,然后调用窗口显示子任务进行显示。在完成一帧数据的显示后,调用一次OSTimeDlyHMSM()使当前任务进入等待状态,下一个优先级最高并进入了就绪态的任务,立刻被赋予了CPU的控制权,由此完成窗口显示任务之间的切换。任务TaskControl()定期查询Reset是否有效,若有效则删除原来建立的任务,重新读取窗口数,建立新任务,启用各个窗口显示任务Task_i。

任务TaskControl的伪程序段描述如下:

结语

本设计充分利用了Nios II 32位处理器的高性能和μC/OS-II实时操作系统高效的任务调度算法,实现了单屏幕多窗口显示,且显示屏控制变得更加灵活。整个控制系统在1片FPGA芯片上完成,有效地降低了系统的成本。

1 系统总体设计

1.1 系统硬件结构

LED显示系统主要由计算机系统、数据通信传输模块、数据处理模块、扫描控制模块、显示驱动模块和LED屏构成,如图1所示。

计算机系统将要显示的点阵信息通过RS485串行接口送往存储设备,数据处理模块读取存储设备的数据并进行各种特技显示处理,将处理好的数据送往扫描控制模块,显示驱动模块接收到扫描控制模块的数据后送往LED屏上显示。数据通信传输模块、数据处理模块、扫描控制模块3部分均在FPGA上实现,即构成LED异步控制器。

1.2 系统软件方案

软件基于Nios II IDE开发完成,应用程序基于μC/OS-II实时操作系统实现。软件程序主要由2个任务和1个定时器中断服务程序组成,任务问采用信号量的方式进行通信。任务1将上位机传送到CF卡存储设备的数据写入内存中;任务2从内存中读取数据并进行分析处理,把分析处理完的数据送往扫描控制模块。为了充分利用μC/OS-II的实时性和多任务的特点,采用嵌入式文件系统进行数据管理。

2 控制系统硬件部分设计

数据处理模块由Nios II软核CPU、1片SDRAM和1片Flash存储器组成。Nios II软核CPU是整个控制器的核心,负责数据的处理;sDRAM作为CPU处理数据时的缓存使用;Flash存储器用于存储点阵信息数据和LED屏显示控制参数。

扫描控制模块由用户自定义的PWM IP核和显存组成。显存采用1片SRAM实现,用来保存当前显示的一帧点阵信息数据。PWM模块通过Aval-on总线和Nios IICPU连接,将从CPU接收到的数据按指定地址写入显存,然后再按一定的寻址方式从显存中读取点阵信息数据进行扫描。串口控制器、定时器、存储器控制器、CF卡控制器通过SOPC Builder软件定制集成IP核自动生成。本控制器的硬件结构如图2所示。

3 控制系统软件部分设计

控制系统软件是基于实时操作系统μC/OS-II进行设计的。该操作系统利用高效任务调度算法调度每个任务,而每个窗口的显示由单个任务完成。主函数创建了2个任务:一个用于读取CF卡数据;另一个用于接收来自不同显示模块的场景数据和播放显示文件。

3.1 数据结构

数据在存储器中的存储形式直接影响数据的存取速度和控制的复杂度。本系统对显存中的数据和缓存中的数据均重新组织,降低了数据处理和扫描控制的复杂度。

3.1.1 显存数据的组织

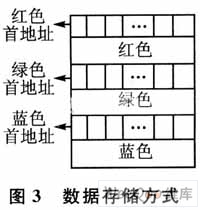

LED显示屏的每个像素点都包括红、绿、蓝3种基色,每种颜色的灰度级均为256级(即由8位数据对像素点灰度级进行编码),故每个像素点需要占用3字节的存储空间。显示时,每个像素的红管、绿管、蓝管是同时点亮的,也就是说,3种颜色的数据是并行上屏的。可将红、绿、蓝3种颜色对应的数据分开存储,以方便操作。数据存储方式如图3所示。同一种颜色的数据集中存放在某个区域中,区域的首地址作为该颜色的基址。在进行数据存放时,每个像素点只需给出相对变化地址(变址),加上不同颜色的基址就可以在3个区域中找到对应点的视频数据。

LED显示屏灰度的实现方法是分权重扫描的。这样就需要对颜色数据进行位分离,然后同权重的位重新组合。为了方便操作,存储时把图3所示的每个区再分为8个权重区,所有同权重的数值集中放于对应的权重区中。所谓位分离,就是把数据的高低位按权重分开,然后重新组织。位分离在可编程逻辑器件中比较容易实现,可以划出一块逻辑矩阵,操作时横向存入,纵向读出即可。位分离示意图如图4所示。

3.1.2 缓存数据的组织

若要进行特技效果显示,则当前显示的数据帧和下一个数据帧存在着某种变换关系。由于CPU只能对显存进行写操作,所以需在缓存中划分出一块大小和显存相等、地址一一对应的区域screen,用于存储当前显示的数据帧信息。如果各窗口之间存在重叠现象,且特技数据处理运算直接在screen区域进行,则窗口重叠部分信息可能发生混乱。故在缓存中再为每一个窗口划分出一块存取空间(part 1,part 2,…,part n),用于存储本窗口显示的前一帧数据信息。在特技数据处理运算时,先在part区域处理各窗口的数据信息,将转换完的数据送往各窗口在screen区域中所对应地址的存取空间,最后将screen中的数据写入地址对应的显存。

3.2 读取CF卡软件设计

任务1负责将CF卡上的数据读取到SDRAM中,供其他任务使用。在程序中使用了1个指针(*pwmdata),为数据文件在SDRAM中分配空间。在文件系统初始化时,首先调用CF卡初始化函数IDE_initialize()判断CF卡是否存在。若存在,则读取文件系统的基本信息。通过调用函数FS_SearchFile(char*FName,FS_TFile*R,unsigned char dir)来查找需要读取的文件是否存在,若存在,则通过指针(*pwmdata)为数据文件在SDRAM中分配一个缓冲区。读取时,每次读取一个扇区,直到将数据全部读取到sDRAM中。

部分程序源码如下:

3.3软件总体设计

基于以上数据结构,软件设计的流程如图5所示。系统首先进行初始化操作,然后从Flash中读取显示屏参数,进行参数初始化。接着建立任务TaskControt(),其优先级比各窗口显示任务都要高,主要用于实时管理各窗口显示任务,每个窗口的显示由单个窗口显示任务来控制。窗口显示任务根据各窗口显示方式的不同,在其对应的part存储区域进行下一帧数据的处理运算,然后调用窗口显示子任务进行显示。在完成一帧数据的显示后,调用一次OSTimeDlyHMSM()使当前任务进入等待状态,下一个优先级最高并进入了就绪态的任务,立刻被赋予了CPU的控制权,由此完成窗口显示任务之间的切换。任务TaskControl()定期查询Reset是否有效,若有效则删除原来建立的任务,重新读取窗口数,建立新任务,启用各个窗口显示任务Task_i。

任务TaskControl的伪程序段描述如下:

结语

本设计充分利用了Nios II 32位处理器的高性能和μC/OS-II实时操作系统高效的任务调度算法,实现了单屏幕多窗口显示,且显示屏控制变得更加灵活。整个控制系统在1片FPGA芯片上完成,有效地降低了系统的成本。

- OLED显示器及其馈电技术(08-13)

- 基于S3C44B0X的大型LED显示系统设计(08-14)

- 利用EL7516制作高效、高电流的白光LED驱动器(08-14)

- OLED显示模块与C8051F单片机的接口设计(08-14)

- 白光型发光二极管(WLED)之背光设计兵法(08-26)

- LCD和OLED在车载显示的应用 (08-26)