高速大容量存储系统设计

时间:08-19

来源:互联网

点击:

在测量技术中,高速数字摄像机所拍摄到的大量数字图像需要高速、大容量的图像存储设备来实时快速地存储。用传统的磁带方式来记录数据,其效率和安全性不高;静态存储器读写方便,但是存储的数据会因断电而丢失,所以不利于数据的长时间保存。而近几年问世的闪存以其存储容量大、体积小、可靠性高等优点,逐步向存储系统进军。

1 设计原理

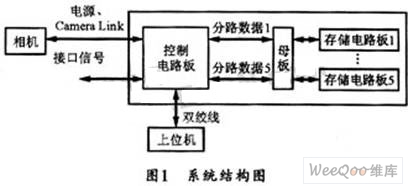

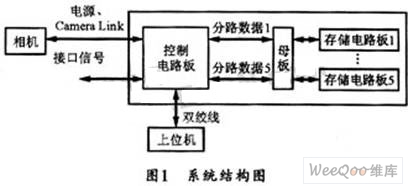

设计中相机输出LVDS串行数据通过接收电平转换和串并转换后得到10路×8 bit的并行数据流,其数据流速率最大为66 MHz。之后根据相机MC1311的性能指标可计算出Camera Link高速接口与数据存储系统的存储容量要求与存储速度要求,即:单帧数据量为1280×1024×8 bit;每秒最大数据量为500×1280×1024×8 bit;Camera Link高速接口单路数据速率为65.536 MByte,如果需要连续存储60秒的视频数据,则需要40 G Byte存储器容量。100 GByte的存储容量最多大约可存储2.5分钟视频数据。图1为系统结构图。

2 核心器件选择

设计中的存储芯片采用SAMSUNG公司的NAND FLASH芯片K9 K8G08UOI,它的外部接口最高速度为40 MHz,接口宽度8位。每个芯片有8192块,每块有64页,每页大小为(2K+64)Bytes,其中64 Bytes为空闲区,存储容量为8Gbit。它以页为单位进行读写,以块为单位进行擦除。控制核心FPGA采用ALTERA公司STRATIXⅡ系列的EP2S30F672I4,它有着丰富的触发器和LUT,非常适合复杂时序逻辑的设计,具有1.3Mbit的内置存储RAM,可以缓存一定量的数据。

3 系统设计

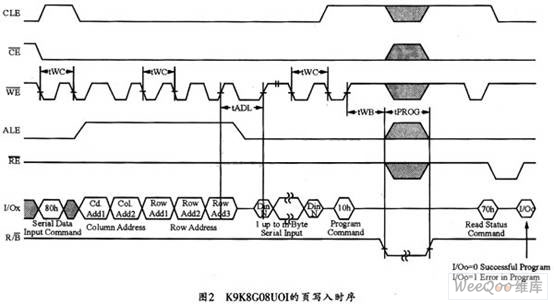

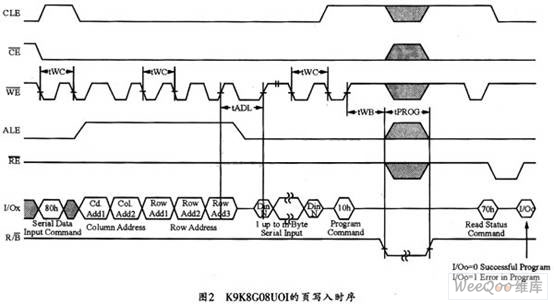

NAND Flash的数据存储采用页编程方式写入,K9K8G08UOI的页写入时序如图2所示。

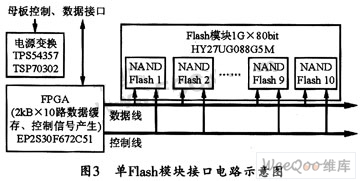

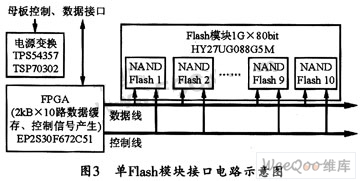

根据图2的时序可以估算出单片K9K8G08UOI的数据存储速率,其中tWC最小为25 ns,tADL为75ns,tWB为100 ns,tPROG为200μs。因此,写入一页所需时间大约为:200μs+100 ns+(2048+64) ×25ns+75 ns=252.975μs,由于一页数据为(2K+64)B,所以单片K9K8G08UOI每Byte的数据存储速率为:1/(252.975μs/(2048+64)B)=8.4152 MHz。可见单片K9K8G08UOI的写入速度不能满足Camera,Link的接口要求,故需用多片进行数据位扩展。为了解决NAND Hash存取数据速度较慢向题,可将相邻10个8 bit视频数据在FPGA内展宽为80 bit进行存取。而NAND Flash每Byte的存储速率要求可降为6.6 MHz,故可满足单片K9K8G08UOI的存储速度要求。系统中每10片K9K8G08UOI组成一个1 G×80 bit的Flash模块,共10个Flash模块。每个Hash模块共用一套控制线,数据线分别与FPGA相连。单Flash模块的组成原理如图3所示。

电路中Flash1~10的连接一致,即数据总线独立连接到FPGA共用控制总线(带驱动)。由图3可见,若需要进一步降低单片Flash存储速率,可进一步扩展Flash存储器芯片数量。由于单片FPGA的I/O数有限,可将10个Flash模块安排到5块扩展存储器板上,分别对应Camera Link串并转换得到的一路数据(66 MHz×8 bit)。每个存储器板与1片FPGA和2个Flash模块相连后再分别与控制电路板上的FPGA相连来进行数据传输。其中的5块扩展存储器板采用相同结构。

4 FPGA逻辑设计

FLASH的基本操作分为两个阶段:加载时间和编程时间,写入的时间瓶颈并不在加载时间,而是FLASH的编程时间。为了解决高速数据与低速FLASH之间的矛盾,可采用数据流串并转换、多个模块并行处理的方法。可在FPGA内部构建10个双口RAM用来缓存数据,每个双口RAM对应一个FLASH,相机过来的数据先缓存到RAM里,然后再写到FLASH。数据写到RAM可采用流水操作,数据写满第一个双口RAM,接着写第二个RAM,依次进行,当写满第十个RAM时,将十个RAM缓存的数据写到对应的FLASH里。FLASH操作按最高速度40MB进行,加载时间为51.2μs,之后进入编程时间,再来的数据继续缓存在第一个RAM里。相机的时钟是66 MHz,每个RAM的深度为2048 Bytes,那么写10个RAM的时间是310μs,即FALSH编程时间可以达到310-51.2=258.8μs,可以满足FLASH的典型编程时间200μs。其FLASH流水操作见图4。

5 FLASH坏区管理

对FLASH的坏区实行动态管理,在每个存储电路板的FPGA内开辟1 K×8 bit的坏区地址存储。所有存储电路板的坏区地址一致。在FLASH进行写操作前比对当前区是否为坏区,如果是坏区则跳过此区进入下一区。

可采用写入特定数后读出校验的方式来检测坏区。存储电路板根据命令全区写入8 bit数据。写入时序按系统设计的最高速率进行。然后将它们顺序读出并进行校验,如果出现数据错误则登记该压为坏区。图5为坏区检测管理的工作流程。

6 结束语

本文采用多级流水线与并行处理相结合的方式,同时利用FPGA内部的缓存来使多个FLASH存储器并行工作,从而极大地提高了存储速率。100片FLASH存储器同时工作可满足660 MB/S的速度要求。经过测试,本系统可以可靠地存储数字图像,并可屏蔽坏区。(西安电子科技大学 作者:李华,王文英)

1 设计原理

设计中相机输出LVDS串行数据通过接收电平转换和串并转换后得到10路×8 bit的并行数据流,其数据流速率最大为66 MHz。之后根据相机MC1311的性能指标可计算出Camera Link高速接口与数据存储系统的存储容量要求与存储速度要求,即:单帧数据量为1280×1024×8 bit;每秒最大数据量为500×1280×1024×8 bit;Camera Link高速接口单路数据速率为65.536 MByte,如果需要连续存储60秒的视频数据,则需要40 G Byte存储器容量。100 GByte的存储容量最多大约可存储2.5分钟视频数据。图1为系统结构图。

2 核心器件选择

设计中的存储芯片采用SAMSUNG公司的NAND FLASH芯片K9 K8G08UOI,它的外部接口最高速度为40 MHz,接口宽度8位。每个芯片有8192块,每块有64页,每页大小为(2K+64)Bytes,其中64 Bytes为空闲区,存储容量为8Gbit。它以页为单位进行读写,以块为单位进行擦除。控制核心FPGA采用ALTERA公司STRATIXⅡ系列的EP2S30F672I4,它有着丰富的触发器和LUT,非常适合复杂时序逻辑的设计,具有1.3Mbit的内置存储RAM,可以缓存一定量的数据。

3 系统设计

NAND Flash的数据存储采用页编程方式写入,K9K8G08UOI的页写入时序如图2所示。

根据图2的时序可以估算出单片K9K8G08UOI的数据存储速率,其中tWC最小为25 ns,tADL为75ns,tWB为100 ns,tPROG为200μs。因此,写入一页所需时间大约为:200μs+100 ns+(2048+64) ×25ns+75 ns=252.975μs,由于一页数据为(2K+64)B,所以单片K9K8G08UOI每Byte的数据存储速率为:1/(252.975μs/(2048+64)B)=8.4152 MHz。可见单片K9K8G08UOI的写入速度不能满足Camera,Link的接口要求,故需用多片进行数据位扩展。为了解决NAND Hash存取数据速度较慢向题,可将相邻10个8 bit视频数据在FPGA内展宽为80 bit进行存取。而NAND Flash每Byte的存储速率要求可降为6.6 MHz,故可满足单片K9K8G08UOI的存储速度要求。系统中每10片K9K8G08UOI组成一个1 G×80 bit的Flash模块,共10个Flash模块。每个Hash模块共用一套控制线,数据线分别与FPGA相连。单Flash模块的组成原理如图3所示。

电路中Flash1~10的连接一致,即数据总线独立连接到FPGA共用控制总线(带驱动)。由图3可见,若需要进一步降低单片Flash存储速率,可进一步扩展Flash存储器芯片数量。由于单片FPGA的I/O数有限,可将10个Flash模块安排到5块扩展存储器板上,分别对应Camera Link串并转换得到的一路数据(66 MHz×8 bit)。每个存储器板与1片FPGA和2个Flash模块相连后再分别与控制电路板上的FPGA相连来进行数据传输。其中的5块扩展存储器板采用相同结构。

4 FPGA逻辑设计

FLASH的基本操作分为两个阶段:加载时间和编程时间,写入的时间瓶颈并不在加载时间,而是FLASH的编程时间。为了解决高速数据与低速FLASH之间的矛盾,可采用数据流串并转换、多个模块并行处理的方法。可在FPGA内部构建10个双口RAM用来缓存数据,每个双口RAM对应一个FLASH,相机过来的数据先缓存到RAM里,然后再写到FLASH。数据写到RAM可采用流水操作,数据写满第一个双口RAM,接着写第二个RAM,依次进行,当写满第十个RAM时,将十个RAM缓存的数据写到对应的FLASH里。FLASH操作按最高速度40MB进行,加载时间为51.2μs,之后进入编程时间,再来的数据继续缓存在第一个RAM里。相机的时钟是66 MHz,每个RAM的深度为2048 Bytes,那么写10个RAM的时间是310μs,即FALSH编程时间可以达到310-51.2=258.8μs,可以满足FLASH的典型编程时间200μs。其FLASH流水操作见图4。

5 FLASH坏区管理

对FLASH的坏区实行动态管理,在每个存储电路板的FPGA内开辟1 K×8 bit的坏区地址存储。所有存储电路板的坏区地址一致。在FLASH进行写操作前比对当前区是否为坏区,如果是坏区则跳过此区进入下一区。

可采用写入特定数后读出校验的方式来检测坏区。存储电路板根据命令全区写入8 bit数据。写入时序按系统设计的最高速率进行。然后将它们顺序读出并进行校验,如果出现数据错误则登记该压为坏区。图5为坏区检测管理的工作流程。

6 结束语

本文采用多级流水线与并行处理相结合的方式,同时利用FPGA内部的缓存来使多个FLASH存储器并行工作,从而极大地提高了存储速率。100片FLASH存储器同时工作可满足660 MB/S的速度要求。经过测试,本系统可以可靠地存储数字图像,并可屏蔽坏区。(西安电子科技大学 作者:李华,王文英)

- 利用FPGA和新技术,使LCD进入HDTV市场(08-27)

- 基于DSP和FPGA的电视观瞄系统设计(09-02)

- FPGA与SRAM相结合完成大容量数据存储(09-03)

- HDTV接收机中Viterbi译码器的FPGA实现(09-09)

- 基于FPGA的液晶显示接口设计 (09-26)

- 解决硬盘驱动器能耗难题(10-13)