ECC技术在大容量智能Smart Media卡上的应用

时间:08-12

来源:互联网

点击:

1 引言

SM卡是一种nash Memory存储卡,轻薄短小是其未来产品的发展趋势。SM卡具有体积小(45 mm×37 mm x0.76mm),质量轻(仅1.8克),结构简单,携带方便,且具有较高的擦写性能,功耗低,易于升级,带有便于数据传输的PCMCIA界面等优点,但存在兼容性差和容量小的缺点。

采用大容量的SM卡作为存储介质用于存储采集的数据具有突破性发展。但其最关键技术问题是要保证各种大量的数据能够在计算机中正确地回放和分析,保证计算机正确无误地识别出SM卡中的数据,因此要求SM卡的存储数据格式应与DOS文件系统相兼容。错误检查与纠正编码简称ECC,是一种实现计算机错误检查和纠正的技术,可使整个计算机系统工作时安全稳定。而ECC技术应用于大容量SM卡,使其数据采集、储存更安全稳定,并给出了ECC编码算法,程序设计及查错校正的实现。

2 ECC与SM的地址转换

按照DOS文件操作系统存储数据的方法,SM卡除存储数据功能外,还具有以下5个区域:卡信息结构(Card Information Structure,简称CIS)、主引导记录(Master Boot Record简称,MBR)、分区引导记录(Partition Boot Record,简称PBR)、分件分配表(File A11ocation Table,简称FAT)、根目录(Root Directory,简称DIR)。CPU采用逻辑地址操作存储介质,由于逻辑地址与物理地址不同,物理地址是存储介质的实际地址,如果按照物理地址顺序存储数据,则不便于文件增加或删减的操作,因此,其DOS逻辑地址与物理地址必须按照转换表进行转换。而SM卡的转换表处于每页存储区的冗余区内。

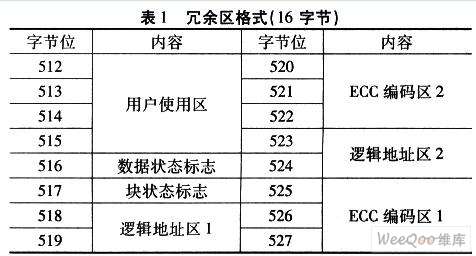

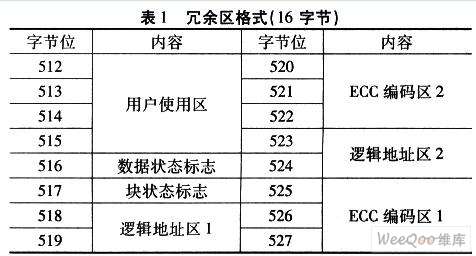

SM卡每页包括528字节,分为512字节数据区和16字节的冗余区。冗余区的格式如表l所示,其中ECC编码区和逻辑、物理转换区是最为重要部分。

由表1可以看出:逻辑地址区1和逻辑地址区2完全一致,ECC编码区2是指256"512字节的ECC编码,ECC编码区l是指0"255字节的ECC编码,数据状态标志和块状态标志为FFH时正常,否则异常。逻辑地址区是针对DOS文件系统的逻辑地址和物理地址的转换表,格式如表2所示,其中BA9~BA0为逻辑地址,P为奇偶区标志。

所谓逻辑地址是相对于DOS文件系统而言,DOS文件系统在存储文件时,并不是完全按照物理地址的顺序存储的,而是将物理地址按一定的算法分配成逻辑地址,文件存储是按照FAT表中标注的逻辑地址,再根据冗余区中的逻辑地址的内容找到相应的物理地址区实现的。整个SM卡的逻辑地址分布如表3所示。

3 ECC编码

ECC与奇偶校验(Parity)相类似,然而Parity只能检测错误,而ECC则可纠正每页的l位错误。经过内存纠错,计算机的操作指令才能继续。

由于SM卡存在“写入干扰”,易引起数据错误,而且该错误不能利用写入Flash状态进行检查。根据SM卡实验结果推断,写入干扰引发的错误在l页中(512字节)只有1位出现错误。因此认为这类错误可利用ECC码检查并纠正,而不视为坏块。这样将大大提高SM卡的可靠性和寿命。在设计中以512字节为一组数据,加上ECC码(3字节),这样可以使ECC码的比例达到最低。

4 ECC编码算法和程序设计

4.1 ECC码的普通算法

以64字节一组数据为例说明ECC码的普通算法,前52字节为输入数据,后面12字节补零或64字节参加运算。先将64字节数据排成一列,即最高地址数据bit7,bit 6…bit O,然后为次高地址数据bit 7,bit 6…bit O,依次根据地址由高到低,直至最低地址数据bit 7,bit 6…bit 0,总共512位。

首先将512位分成前256位和后256位。计算前256位中“1”的个数k,如果k为奇数,令P(256)=l;若k为偶数,则令P(256)=O。然后计算后面256位中“1”的个数为j,如果j为奇数,则令Q(256)=1;若j为偶数,则Q(256)=0。

然后,再把512位等分4块,每一块均为128位。把第一块、第三块合在一起,计算其中“1”的个数l,如果l为奇数,令P(128)=l;若f为偶数,令P(128)=0;把第二块和第四块合在一起,计算其中“1”的个数m,如果m为奇数,则令Q(128)=1,若m为偶数,令Q(128)=0。

第三步,把512位等分为8块,每块为64位,把奇数次块合并在一起,计算“l”的个数,决定P(64)是“1”还是“0”,再把偶数次块合并在一起,计算“1”的个数,决定Q(64)是“1',还是“0”。

依次类推,每次块数增加一倍,其块的位数减少一半,直到每块中只有1位为止。将奇数次块合并在一起,然后决定P(16)、P(8)、P(4)、P(2)、P(1)分别是“1”还是“0”;把偶数次块合在一起,决定Q(16)、Q(8)、Q(4)、Q(2)、Q(1)分别是“1”,还是“0”。

最后,把上述P(i)、Q(i)排成一列得P(256)Q(256)P(128)Q(128)P(64)Q(64)…P(1)Q(1)总共18位就构成ECC码,ECC码为3字节,多余位全为零。

4.2 简化ECC码算法

计算ECC码是一个子程序,要求程序要短,ECC子程序的长度为120字节,F015的程序空间可以容纳;执行要快,ECC子程序的执行时间约为2 ms。由于F015的程序空间不大,而子程序是在记录过程中经数据采集,运算再加上ECC码,然后存入Flash。运算时间过长会干扰下一点数据采集,破坏数据完整性。数据采集周期为1/8 s(125 ms),ECC运行时间应小于12.5 ms。

程序采用数据平行处理,巧妙重复利用F015指令,从而达到系统要求。

5 查错和校正

5.1 错误类型

常见内存错误为:单位、多位、列、行等错误。其中单位错误大多在读取一个完整比特时有一位出错;而多位错误是读相同比特时总是同一位数据出错;如果单位错误发生在很多词中,则视为列或行错误。

5.2 查错和校正算法

无错误时,ECC码全为0;当主区有1位错误,每一个相似组(eg:P8&P8’)有l&0或0&1,可以纠错;如果Flash有多于2位以上的错误,则没办法修正。

在数据存入前产生的ECC码为PQ先,在读出数据后计算得的ECC码为PQ后,具体算法如下:

(1)若PQ先^PQ后(^为异或),

(2)若异或后000 000 000 000 000 000,则表示数据无错。PQ先^PQ后,R=RF(256)RQ(256)RP(128)RQ(128)…RP(1)RQ(1),其中RP(256)=P(256)先^P(256)后,RQ(256)=Q(256)先^Q(256)后。

若RP(i)^RQ(i)为l,对所有i(i=1,2,4…256)都成立,则

存在1位错码,其出错的位置:由RP(256)RP(128)RP(64)RP(32)RP(16)RP(8)地址决定的这一字节中地址(范围0—63)在RP(4)RP(2)RP(1)的位上(O"7位)。将上述参数决定的该字节的位数据取非,就可校正数据中的错误。

(3)RP(i)^RQ(i)=1,只对一个i(i=1,2,4…256)成立。则ECC码PO先出错,数据正确。

(4)若出现其他情况,则无法校正数据错误。

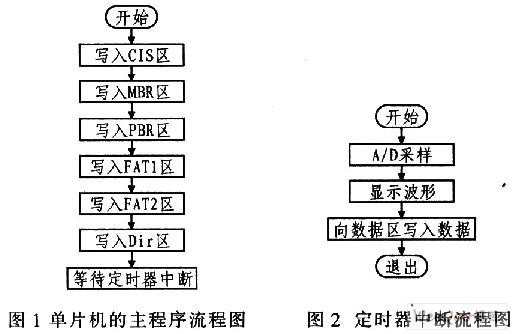

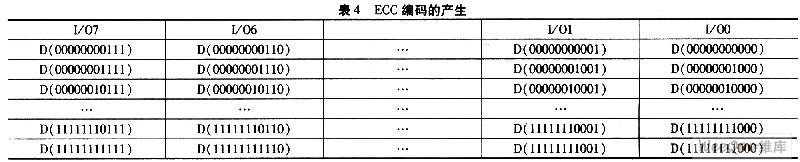

6 ECC编码的实现

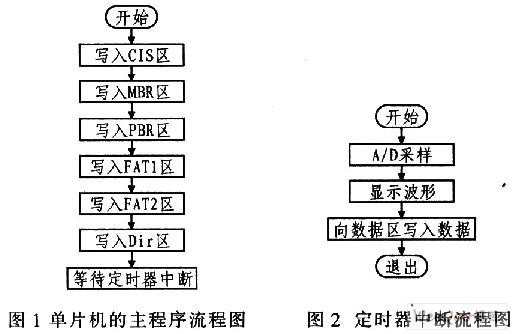

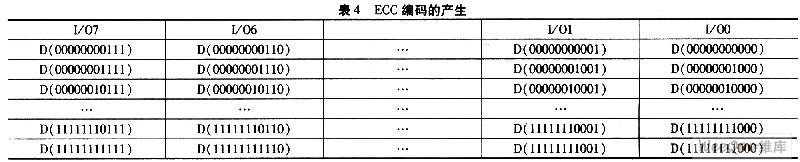

256字节数据的ECC码是3个字节,其中22个字节是有用的。ECC编码的产生、计算方法及错码检测方法框图分别如表4、图1和图2所示。

由图1和图2可看出,写入DOS文件系统所需的各功能区的内容,在实际编程中要严格按照其结构编写,否则计算机将无法识别。

7 结语

通过讨论和分析可见,SM卡的存储结构、DOS存储格式以及ECC代码的编写所构成SM卡数据存储系统的软件部分,说明了将ECC技术应用于大容量的SM卡是可行的。

SM卡是一种nash Memory存储卡,轻薄短小是其未来产品的发展趋势。SM卡具有体积小(45 mm×37 mm x0.76mm),质量轻(仅1.8克),结构简单,携带方便,且具有较高的擦写性能,功耗低,易于升级,带有便于数据传输的PCMCIA界面等优点,但存在兼容性差和容量小的缺点。

采用大容量的SM卡作为存储介质用于存储采集的数据具有突破性发展。但其最关键技术问题是要保证各种大量的数据能够在计算机中正确地回放和分析,保证计算机正确无误地识别出SM卡中的数据,因此要求SM卡的存储数据格式应与DOS文件系统相兼容。错误检查与纠正编码简称ECC,是一种实现计算机错误检查和纠正的技术,可使整个计算机系统工作时安全稳定。而ECC技术应用于大容量SM卡,使其数据采集、储存更安全稳定,并给出了ECC编码算法,程序设计及查错校正的实现。

2 ECC与SM的地址转换

按照DOS文件操作系统存储数据的方法,SM卡除存储数据功能外,还具有以下5个区域:卡信息结构(Card Information Structure,简称CIS)、主引导记录(Master Boot Record简称,MBR)、分区引导记录(Partition Boot Record,简称PBR)、分件分配表(File A11ocation Table,简称FAT)、根目录(Root Directory,简称DIR)。CPU采用逻辑地址操作存储介质,由于逻辑地址与物理地址不同,物理地址是存储介质的实际地址,如果按照物理地址顺序存储数据,则不便于文件增加或删减的操作,因此,其DOS逻辑地址与物理地址必须按照转换表进行转换。而SM卡的转换表处于每页存储区的冗余区内。

SM卡每页包括528字节,分为512字节数据区和16字节的冗余区。冗余区的格式如表l所示,其中ECC编码区和逻辑、物理转换区是最为重要部分。

由表1可以看出:逻辑地址区1和逻辑地址区2完全一致,ECC编码区2是指256"512字节的ECC编码,ECC编码区l是指0"255字节的ECC编码,数据状态标志和块状态标志为FFH时正常,否则异常。逻辑地址区是针对DOS文件系统的逻辑地址和物理地址的转换表,格式如表2所示,其中BA9~BA0为逻辑地址,P为奇偶区标志。

所谓逻辑地址是相对于DOS文件系统而言,DOS文件系统在存储文件时,并不是完全按照物理地址的顺序存储的,而是将物理地址按一定的算法分配成逻辑地址,文件存储是按照FAT表中标注的逻辑地址,再根据冗余区中的逻辑地址的内容找到相应的物理地址区实现的。整个SM卡的逻辑地址分布如表3所示。

3 ECC编码

ECC与奇偶校验(Parity)相类似,然而Parity只能检测错误,而ECC则可纠正每页的l位错误。经过内存纠错,计算机的操作指令才能继续。

由于SM卡存在“写入干扰”,易引起数据错误,而且该错误不能利用写入Flash状态进行检查。根据SM卡实验结果推断,写入干扰引发的错误在l页中(512字节)只有1位出现错误。因此认为这类错误可利用ECC码检查并纠正,而不视为坏块。这样将大大提高SM卡的可靠性和寿命。在设计中以512字节为一组数据,加上ECC码(3字节),这样可以使ECC码的比例达到最低。

4 ECC编码算法和程序设计

4.1 ECC码的普通算法

以64字节一组数据为例说明ECC码的普通算法,前52字节为输入数据,后面12字节补零或64字节参加运算。先将64字节数据排成一列,即最高地址数据bit7,bit 6…bit O,然后为次高地址数据bit 7,bit 6…bit O,依次根据地址由高到低,直至最低地址数据bit 7,bit 6…bit 0,总共512位。

首先将512位分成前256位和后256位。计算前256位中“1”的个数k,如果k为奇数,令P(256)=l;若k为偶数,则令P(256)=O。然后计算后面256位中“1”的个数为j,如果j为奇数,则令Q(256)=1;若j为偶数,则Q(256)=0。

然后,再把512位等分4块,每一块均为128位。把第一块、第三块合在一起,计算其中“1”的个数l,如果l为奇数,令P(128)=l;若f为偶数,令P(128)=0;把第二块和第四块合在一起,计算其中“1”的个数m,如果m为奇数,则令Q(128)=1,若m为偶数,令Q(128)=0。

第三步,把512位等分为8块,每块为64位,把奇数次块合并在一起,计算“l”的个数,决定P(64)是“1”还是“0”,再把偶数次块合并在一起,计算“1”的个数,决定Q(64)是“1',还是“0”。

依次类推,每次块数增加一倍,其块的位数减少一半,直到每块中只有1位为止。将奇数次块合并在一起,然后决定P(16)、P(8)、P(4)、P(2)、P(1)分别是“1”还是“0”;把偶数次块合在一起,决定Q(16)、Q(8)、Q(4)、Q(2)、Q(1)分别是“1”,还是“0”。

最后,把上述P(i)、Q(i)排成一列得P(256)Q(256)P(128)Q(128)P(64)Q(64)…P(1)Q(1)总共18位就构成ECC码,ECC码为3字节,多余位全为零。

4.2 简化ECC码算法

计算ECC码是一个子程序,要求程序要短,ECC子程序的长度为120字节,F015的程序空间可以容纳;执行要快,ECC子程序的执行时间约为2 ms。由于F015的程序空间不大,而子程序是在记录过程中经数据采集,运算再加上ECC码,然后存入Flash。运算时间过长会干扰下一点数据采集,破坏数据完整性。数据采集周期为1/8 s(125 ms),ECC运行时间应小于12.5 ms。

程序采用数据平行处理,巧妙重复利用F015指令,从而达到系统要求。

5 查错和校正

5.1 错误类型

常见内存错误为:单位、多位、列、行等错误。其中单位错误大多在读取一个完整比特时有一位出错;而多位错误是读相同比特时总是同一位数据出错;如果单位错误发生在很多词中,则视为列或行错误。

5.2 查错和校正算法

无错误时,ECC码全为0;当主区有1位错误,每一个相似组(eg:P8&P8’)有l&0或0&1,可以纠错;如果Flash有多于2位以上的错误,则没办法修正。

在数据存入前产生的ECC码为PQ先,在读出数据后计算得的ECC码为PQ后,具体算法如下:

(1)若PQ先^PQ后(^为异或),

(2)若异或后000 000 000 000 000 000,则表示数据无错。PQ先^PQ后,R=RF(256)RQ(256)RP(128)RQ(128)…RP(1)RQ(1),其中RP(256)=P(256)先^P(256)后,RQ(256)=Q(256)先^Q(256)后。

若RP(i)^RQ(i)为l,对所有i(i=1,2,4…256)都成立,则

存在1位错码,其出错的位置:由RP(256)RP(128)RP(64)RP(32)RP(16)RP(8)地址决定的这一字节中地址(范围0—63)在RP(4)RP(2)RP(1)的位上(O"7位)。将上述参数决定的该字节的位数据取非,就可校正数据中的错误。

(3)RP(i)^RQ(i)=1,只对一个i(i=1,2,4…256)成立。则ECC码PO先出错,数据正确。

(4)若出现其他情况,则无法校正数据错误。

6 ECC编码的实现

256字节数据的ECC码是3个字节,其中22个字节是有用的。ECC编码的产生、计算方法及错码检测方法框图分别如表4、图1和图2所示。

由图1和图2可看出,写入DOS文件系统所需的各功能区的内容,在实际编程中要严格按照其结构编写,否则计算机将无法识别。

7 结语

通过讨论和分析可见,SM卡的存储结构、DOS存储格式以及ECC代码的编写所构成SM卡数据存储系统的软件部分,说明了将ECC技术应用于大容量的SM卡是可行的。

- DVI与HDMI:视频传输的数字化革命(08-15)

- 数字机顶盒技术综述 (08-08)

- 大规模IPTV点播系统解决方案(08-18)

- T-DMB推动手机电视市场崛起(08-15)

- 全球液晶显示器Q2增3.1%超预期(08-11)

- 全面解读 嵌入式DSP上的视频编解码(08-19)