信号完整性与电源完整性的仿真分析与设计

时间:08-31

来源:互联网

点击:

电路完整性设计与分析

从TTL、GTL 到HSTL、SSTL以及 LVDS,目前芯片接口物理标准的演变反映了集成电路工艺的不断进步,同时也反映了高速信号传输要求的不断提高。从版图完整性的分析过程可知,只有结合了互联结构两端负载特性的仿真结果才具有实际意义,而负载特性是由其连接的电路特性所决定的,因此,在完整性设计中,了解这些接口标准是非常必要的。随着传输速率的不断增加,翻转速率控制电路、驱动负载控制电路被广泛使用,它们为完整性设计者提供了更多的优化空间。在具体的完整性分析中,电路设计者需要考虑这些控制的实际实现方式,因为它们会影响到电路的负载特性以及波形性能。另外,还需考虑芯片上解耦电容的实现。

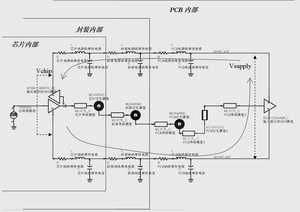

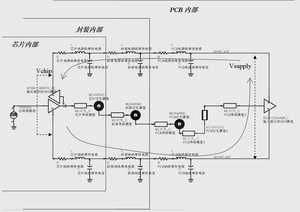

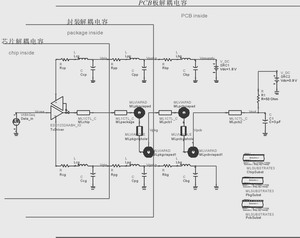

如图3所示的电路仿真图中包括了芯片、封装及PCB板信号线互联及电源互联的等效模型。驱动电路和接收电路采用了IBIS模型(也可以用SPICE模型来替代)。利用该仿真电路,可以观察到一个虚拟系统工作时任一点的信号波形或电源波动状况。信号完整性通常关心的是时钟信号的抖动以及信号波形的上升/下降/保持时间。将电路进行瞬态仿真后利用ADS2005A中内含的眼图工具可自动统计出各抖动分量的值。

电源完整性通常关心的是工作器件所承受的实际电源电压波动,即图3中的Vchip。在实际分析中,系统集成设计的验证者无法测到芯片内部的电源端口,所以无法观测到芯片端口的电源波动和地弹噪声,只能发现封装外引脚处测得的电源与地是相当稳定的。但是,最终决定器件正常工作的电源应该是定义在芯片端口的,封装端口的测量结果并不能反映出此时的电源完整性状况。因此,需要芯片厂商提供封装模型用来对芯片端口处的电源波动及地弹噪声进行仿真。

图3 简化电路完整性仿真示意图

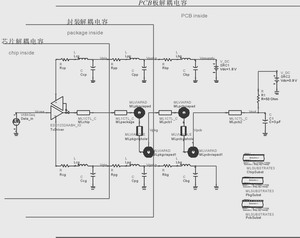

针对上述例子,进一步分别考虑在芯片内部、封装内部以及PCB板加解耦电容,如图4所示。用分别扫描解耦电容值的仿真方法来观察解耦电容对电源完整性的影响。

图4 仿真解耦电容效用的简化原理图

仿真结果表明,加在PCB板上以及封装内的解耦电容并没有明显的作用,在芯片电路设计时增大I/O端口处的电容是最有效的方法。另外,还可以观察到信号完整性与电源完整性的关联性,改变不同解耦电容值后,不仅影响电源波动及地弹噪声状况,信号波形也发生了变化。对于对控制信号通路抖动要求较高的设计来说,还需要同时考虑电源完整性对抖动的影响。

系统完整性设计与分析

系统完整性设计与分析的必要性可以用一个简单的例子来说明。图2中的简单电源传递网络的仿真结果显示,并不是在所有的频点上都呈现出高阻抗。此时电源完整性与激励信号的频谱直接相关,如果在进行系统测试时的激励信号避开3个谐振区,就不会呈现出高阻抗特性。因此,确定激励信号的频谱分布是分析与设计的前提。而激励信号的频谱分布根本上是由其数据内容所决定的,最终将归结于协议的设计。

另一个更加实际的例子是目前电脑硬件接口由并行总线到串行总线的发展趋势,如从PCI-X到PCI-E以及从ATA到SATA等。其中采用的信源及信道编码技术,如时钟扩频、预加重技术等可以改善信号在特定环境中的传输性能。

结合信号完整性与电源完整性的定义,对参考端口的选取需要满足可测性原则,这对于工程实现或调试有着直接的意义。但对于设计链中不同位置上的设计者,可测性的含义并不相同。对于芯片设计者来说,芯片之间的互联结构可以设计特定测试芯片然后利用探针台进行测试;但对于板级设计者来说,无法对手中的成品芯片甚至封装中的互联结构特性进行测试。当信号完整性的参考端口是定义在信道解码器输出处时,误码率的测试是非常重要的。比如,对扩频时钟的分析,只有在相关解调器的输出处才能比较信号传输的质量,测量将会用到误码仪,而在无法测试的环境下只能依赖于误码率仿真等方法。

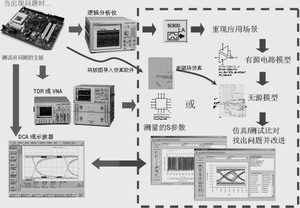

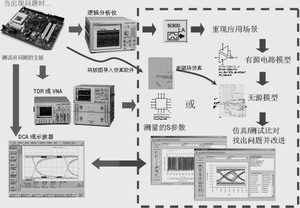

上述的几种情况都要求在仿真分析中能够集成考虑协议算法、电路结构以及互联结构的影响,目前的仿真工具已经可以满足该需求。在针对已有系统的分析中,由于系统完整性分析所包含的因素非常多,再加上协议建模需要相当大的工作量,因此,比较实用的方法是直接测量协议码流(利用逻辑分析仪等仪器),并将之转入到仿真平台中作为电路的激励。这种方法可以准确再现故障时的系统应用场景,有助于现场调试故障系统。解决方案如图5所示。

图5 结合测试建模的分析流程

该分析流程同样也可以用在设计流程中,用测试的方法直接获取待分析接口的协议数据,用于电路设计与版图设计的前期验证,但是,在硬件尚未实现时,将会用规范或之前的经验值来与仿真结果比较。

从TTL、GTL 到HSTL、SSTL以及 LVDS,目前芯片接口物理标准的演变反映了集成电路工艺的不断进步,同时也反映了高速信号传输要求的不断提高。从版图完整性的分析过程可知,只有结合了互联结构两端负载特性的仿真结果才具有实际意义,而负载特性是由其连接的电路特性所决定的,因此,在完整性设计中,了解这些接口标准是非常必要的。随着传输速率的不断增加,翻转速率控制电路、驱动负载控制电路被广泛使用,它们为完整性设计者提供了更多的优化空间。在具体的完整性分析中,电路设计者需要考虑这些控制的实际实现方式,因为它们会影响到电路的负载特性以及波形性能。另外,还需考虑芯片上解耦电容的实现。

如图3所示的电路仿真图中包括了芯片、封装及PCB板信号线互联及电源互联的等效模型。驱动电路和接收电路采用了IBIS模型(也可以用SPICE模型来替代)。利用该仿真电路,可以观察到一个虚拟系统工作时任一点的信号波形或电源波动状况。信号完整性通常关心的是时钟信号的抖动以及信号波形的上升/下降/保持时间。将电路进行瞬态仿真后利用ADS2005A中内含的眼图工具可自动统计出各抖动分量的值。

电源完整性通常关心的是工作器件所承受的实际电源电压波动,即图3中的Vchip。在实际分析中,系统集成设计的验证者无法测到芯片内部的电源端口,所以无法观测到芯片端口的电源波动和地弹噪声,只能发现封装外引脚处测得的电源与地是相当稳定的。但是,最终决定器件正常工作的电源应该是定义在芯片端口的,封装端口的测量结果并不能反映出此时的电源完整性状况。因此,需要芯片厂商提供封装模型用来对芯片端口处的电源波动及地弹噪声进行仿真。

图3 简化电路完整性仿真示意图

针对上述例子,进一步分别考虑在芯片内部、封装内部以及PCB板加解耦电容,如图4所示。用分别扫描解耦电容值的仿真方法来观察解耦电容对电源完整性的影响。

图4 仿真解耦电容效用的简化原理图

仿真结果表明,加在PCB板上以及封装内的解耦电容并没有明显的作用,在芯片电路设计时增大I/O端口处的电容是最有效的方法。另外,还可以观察到信号完整性与电源完整性的关联性,改变不同解耦电容值后,不仅影响电源波动及地弹噪声状况,信号波形也发生了变化。对于对控制信号通路抖动要求较高的设计来说,还需要同时考虑电源完整性对抖动的影响。

系统完整性设计与分析

系统完整性设计与分析的必要性可以用一个简单的例子来说明。图2中的简单电源传递网络的仿真结果显示,并不是在所有的频点上都呈现出高阻抗。此时电源完整性与激励信号的频谱直接相关,如果在进行系统测试时的激励信号避开3个谐振区,就不会呈现出高阻抗特性。因此,确定激励信号的频谱分布是分析与设计的前提。而激励信号的频谱分布根本上是由其数据内容所决定的,最终将归结于协议的设计。

另一个更加实际的例子是目前电脑硬件接口由并行总线到串行总线的发展趋势,如从PCI-X到PCI-E以及从ATA到SATA等。其中采用的信源及信道编码技术,如时钟扩频、预加重技术等可以改善信号在特定环境中的传输性能。

结合信号完整性与电源完整性的定义,对参考端口的选取需要满足可测性原则,这对于工程实现或调试有着直接的意义。但对于设计链中不同位置上的设计者,可测性的含义并不相同。对于芯片设计者来说,芯片之间的互联结构可以设计特定测试芯片然后利用探针台进行测试;但对于板级设计者来说,无法对手中的成品芯片甚至封装中的互联结构特性进行测试。当信号完整性的参考端口是定义在信道解码器输出处时,误码率的测试是非常重要的。比如,对扩频时钟的分析,只有在相关解调器的输出处才能比较信号传输的质量,测量将会用到误码仪,而在无法测试的环境下只能依赖于误码率仿真等方法。

上述的几种情况都要求在仿真分析中能够集成考虑协议算法、电路结构以及互联结构的影响,目前的仿真工具已经可以满足该需求。在针对已有系统的分析中,由于系统完整性分析所包含的因素非常多,再加上协议建模需要相当大的工作量,因此,比较实用的方法是直接测量协议码流(利用逻辑分析仪等仪器),并将之转入到仿真平台中作为电路的激励。这种方法可以准确再现故障时的系统应用场景,有助于现场调试故障系统。解决方案如图5所示。

图5 结合测试建模的分析流程

该分析流程同样也可以用在设计流程中,用测试的方法直接获取待分析接口的协议数据,用于电路设计与版图设计的前期验证,但是,在硬件尚未实现时,将会用规范或之前的经验值来与仿真结果比较。

编码器 解码器 电压 PCB 电路 电流 仿真 电容 CMOS 集成电路 PIC 总线 相关文章:

- 机械测量中旋转编码器与单片机的通用接口(02-13)

- 旋转变压器在转子位置测量中的应用(07-03)

- 基于LabVIEW的气体微流量测量虚拟仪器的开发(07-23)

- 基于通信技术在三坐标测量系统中的应用(08-16)

- LabVIEW计数滤波器在信号降噪中的应用(08-18)

- 光电轴角编码器的细分误差快速测量系统(10-13)