基于TI KeyStone SoC的多标准无线基站设计

基站目前的现场服务年限超过10年,从而显著相应优化了运营商的固定资产投入。部署那些具有线卡可配置且标准可扩展特性的通用基站平台不仅能够减少技术服务及维护成本,而且还能进一步降低配件与库存成本。现场技术人员可为重要的成套设备建立专家团队。就此而言,运行及维护成本也会大幅降低,从而既能优化运营管理成本又可节省固定资本的投入。

3 OEM厂商的回应

OEM厂商面临着严峻的挑战,他们需要提供可支持各种无线标准的产品才能在上述应用方面为运营商提供支持。他们需要提供可支持现有技术的基站,并拥有升级至未来标准的能力。他们必须为运营商提供可高度扩展的远程配置解决方案,同时相关的成本和功耗还需要全面满足运营商在成本支出和运营支出方面设定的目标,这是个相当艰巨的挑战。为了获得成功,OEM厂商需要以低成本提供基站,且其研发和支持费用又需要满足其各自的商业目标。

那么,OEM厂商将如何全面实现平衡呢?为各个标准和现场配置构建专有平台并非解决之道。像大多数企业一样,基站厂商也有商业盈利目标,那就是限制研发和产品支持费用并从资源的优化配置中获利。理想情况下,他们应拥有一套能从中生成多种配置以满足不同运营商需求的基站平台设计。由于软件是一项重要的投资,并占据基站设计中的很大一部分,因而拥有一套软件可移植性和可重用性的解决方案至关重要。OEM厂商需要的通用硬件平台能以极少的重复设计支持多种无线配置,从而能够优化研发成本、加速产品上市进程。为了应对这一挑战,我们需要能大幅优化软件开发及重用性的通用基站片上系统(SoC)平台。

TI提供理想的解决方案

TI提供的通用SoC平台使基站OEM厂商不仅能够设计多标准平台,而且还能创建特定于标准的平台。TI在此方面拥有独特的优势。TI功能强大的创新型KeyStone架构可为基于通用软件/硬件平台之上的多种器件,从而可支持各种通用的无线标准,非常适用于从微小型单元到宏单元配置的各种解决方案。 KeyStone平台使OEM厂商能通过以下详述的两种方案实现运营商的多标准目标。

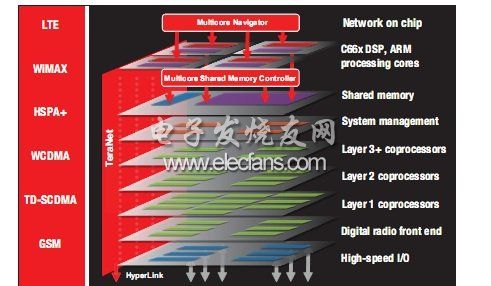

KeyStone架构多标准支持的第一步即在于TI的KeyStone架构。该KeyStone架构采用可同时提供具有定点和浮点处理能力的高级 DSP内核(C66x),从而使OEM厂商和运营商无论在现在当前的部署中还是在将来的高级天线和算法配置中都能实现差异化功能。该款拥有通用I/O接口及SoC基础架构的内核使软件的重复使用和移植变得简单便捷。此平台包含一套可优化研发工作的通用工具,而且在通过单个解决方案平台开发多个产品时能够显著加快上市进程。KeyStone架构见图1。

KeyStone多内核SoC架构在业界率先提供了完整的多核性能。KeyStone可为所有的处理内核、外设、协处理器和I/O接口提供非阻塞接入。部分能充分发挥多内核性能的创新功能包括:多内核导航器、TeraNet、多内核共享存储器控制器(MSMC)和超连结。

4

TIKeyStone多内核SoC架构

图1–-TIKeyStone多内核SoC架构:理想适用于多标准实施

多内核导航器-TI多内核导航器是一款基于分组的创新型管理器,能够控制8,192个队列且能在各种子系统之间提取连接。多内核导航器拥有可实现通信、数据传输以及任务管理的统一接口以及"一次性零拷贝复制"范式,能够以更少的中断数和更低的软件复杂度实现更高的系统性能。

我们以多内核导航器的运行原理为例,多内核导航器不仅能够进行任务调度,面且还能在无需外部管理的情况下指示下一个空闲的DSP内核读取任务并进行处理。其可从如下几个方面简化软件架构并提高基站的性能。

•动态资源/负载共享

•跨子系统通信时可减轻CPU的开销/延迟

•基于硬件的任务优先级排序

•动态负载平衡

•适用于所有IP模块(软件、I/O和加速器)的通用通信方法

多内核导航器可在无需CPU干预的情况下控制数据流,从而释放移动数据所需的CPU周期,并能将片上通信速率提高达每秒20亿条消息。此外,其还能大幅简化软件架构,以使开发周期更短、资源利用更合理。

5

TeraNet-TeraNet采用层级交换结构,能够在SoC内组合交付超过2Tb的数据传输带宽。这从本质上确保了内核或协处理器再也不会缺少数据,并能够交付名符其实的处理能力。由于交换结构属于层级式而非常平坦的纵横式,因而整体功耗能够在空闲状态下大幅降低,并能以最小的时延提供非常高的性能,这也是新一代基站的关键要求。

多核共享存储控制器(MSMC)–MSMC是一种可用于增强性能的独特存储器架构。MSMC允许内核在不使用任何TeraNet带宽的条件下直接访问共享存储器。MSMC可在各内核和其他IP模块之间

KeyStone TI SoC 无线基站 多标准 相关文章:

- TI TRF2443宽带无线IF收发方案(07-07)

- Hittite HMC792LP4E DC-6 GHz数字衰减方案(07-26)

- Hittite HMC713LP3E 50MHz-8GHz 功率检测方案(07-26)

- 高精度宽带锁相环HMC830LP6GE(10-06)

- Multisim 10在差动放大电路分析中的应用(02-15)

- 5G--下一波人物互联的新浪潮(07-07)