阻抗偏高到60~65欧姆有什么危害(中)

时间:02-08

来源:互联网

点击:

作者:袁波(微信公众号:高速先生)

紧接着上期文章的话题,为什么在没有端接措施的情况下,主线段阻抗较高会导致过冲很厉害呢?大家应该都知道,过冲厉害的原因肯定是信号反射比较厉害,造成信号反射的原因无非就是阻抗不匹配了。上期的仿真实例中,造成反射比较厉害的原因就是驱动器的输出阻抗和与之相连的传输线阻抗不匹配。高速先生带大家来扫描一下驱动器的输出阻抗,搭建如下拓扑结构:

图1

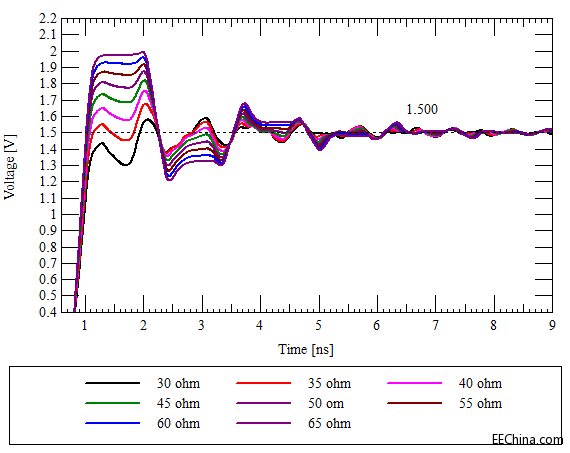

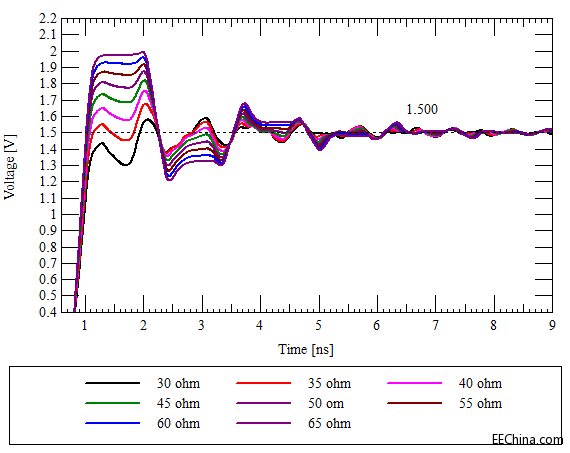

驱动模型和上期选用的一样,这次我们在驱动端加载一个上升沿,扫描中间一段传输线,得到的波形如下图2所示:

图2

由上图2知,当传输线阻抗取35欧姆的时候,电压幅值一开始就达到1.5V左右,反射很小,说明此时传输线的阻抗与驱动器的输出阻抗是近似匹配的。当我们的主线段阻抗偏高到60至65欧姆时,几乎与驱动器的输出阻抗相差一倍,阻抗匹配相差这么多,信号的反射比较严重也就不足为怪了。

2、 从损耗角度分析

在PCB的叠层确定之后,我们控阻抗的主要手段就是调节线宽了。布线时,有时往往会出现布线空间不足的问题,很多工程师会选择走细线。走细线会使得阻抗偏高,且生产制造难度加大,我想很少有工程师从损耗的角度考虑走细线对信号的影响吧,下面我们就来分析一下,线宽变窄对信号的损耗到底有什么影响。

我们分别看看微带线和带状线在线宽变细的情况下,损耗的情况。叠层如下:

图3

我们还是研究阻抗是40,50,60,65欧姆的时候传输线所对应的损耗差异。在以上叠层下,这四种阻抗下,微带线对应的线宽分别是9.5mil,6.2mil,4mil,3.2mil。

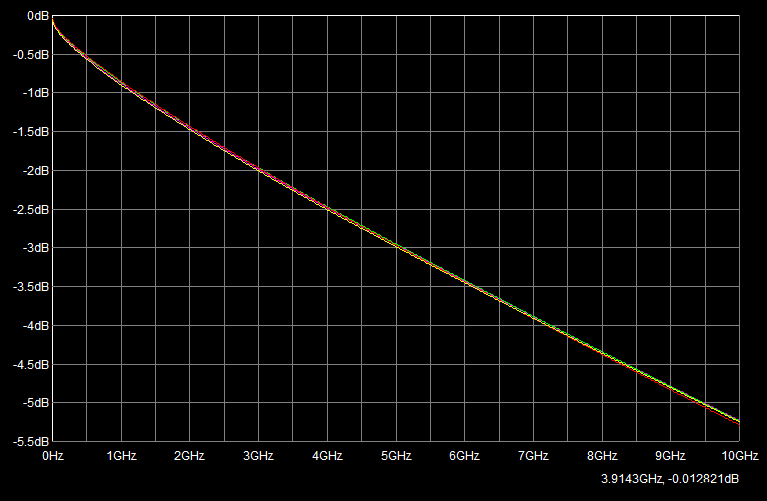

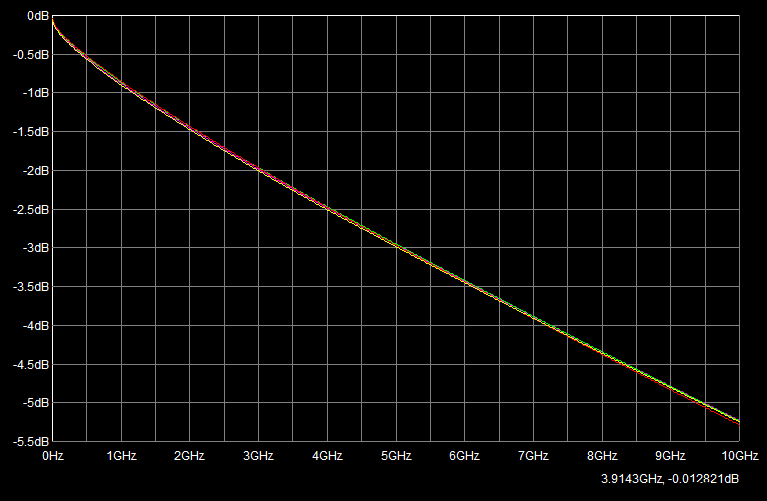

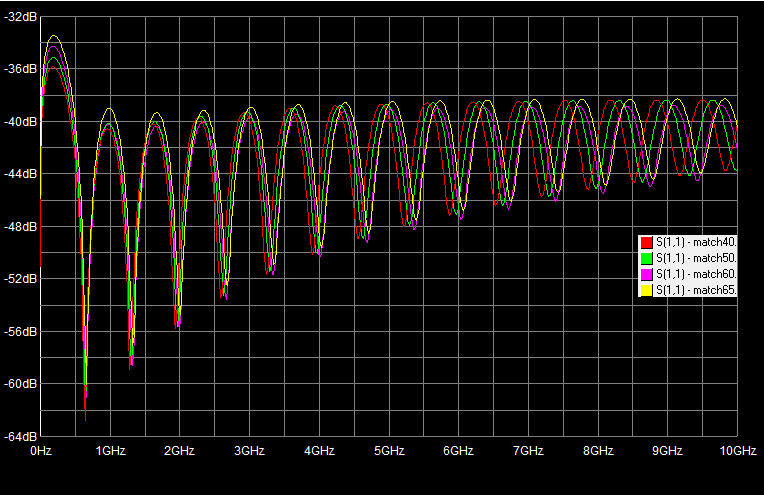

在端口阻抗都是50欧姆的条件下,扫描这四种线宽所对应传输线在线长为5inch条件下的S参数。得到传输线的插损与回损如下图4所示:

图4

图3所对应的叠层下,阻抗是40,50,60,65欧姆的时候,带状线所对应的线宽分别是10mil,7mil,4.5mil,3.4mil。同样,我们默认传输线端口阻抗是50欧姆,扫描通道S参数,得到的插损与回损曲线分别如图5示:

图5

和我们预想的一样,四种线宽对应插损和回损都是有差异的,线宽越细,对应的插损越小,回损越大。插损反映的是传输到终端能量与总输入能量之比,回损反映的是反射能量和输入能量之比,那么,导致能量没有被完全传输过去的原因,是因为能量被反射到源端,还是能量被通道消耗掉了呢?

原来,上图中的S参数在扫描的时候都做了端口归一化处理,就是在扫描的时候默认端口阻抗都是50欧姆,现在我们扫描的时候改变一下端口的阻抗,使其与被扫描传输线阻抗一致,我们再来看看通道插损与回损的情况,微带线损耗如下图6示:

图6

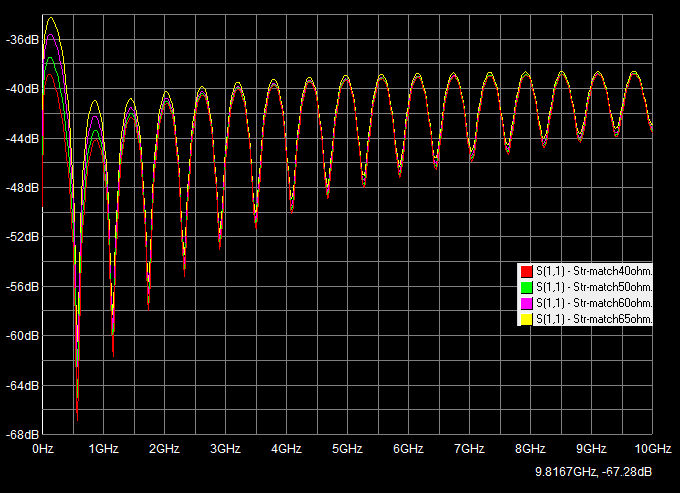

带状线在端口阻抗与传输线阻抗一致的时候,插损与回损曲线如下图7示:

图7

由上图可知,在端口阻抗匹配的情况下,通道的插损与回损曲线差异没有那么大。对于插损来说,带状线与我们想象的一样,线宽越细,损耗越大,但是微带线就没有那么明显。作者认为出现这一现象也是正常的,因为传输线损耗是导体损耗与介质损耗的综合作用,一般情况下是介质损耗占主导作用。微带线和带状线结构不一样,带状线电磁场分布在两个参考层之间,相对较稳定。微带线电磁场有部分分布在空气中,电磁场分布与导体形状也有一定关系,情况比较复杂,由于篇幅关系,这里就不再做深入的分析。

本文简单分析了线宽发生变化时,传输线的损耗情况,可以发现:线宽变化对阻抗的影响比对损耗的影响要大得多,我们应重点关注阻抗不匹配对信号所带来的损害,至于损耗,一般在传输通道很长,速率很高的串行通道中才考虑。解决信号的损耗问题,我们的着眼点也通常在使用DF值更小的板材。

文章没有结束,篇幅关系,敬请期待下期内容…

紧接着上期文章的话题,为什么在没有端接措施的情况下,主线段阻抗较高会导致过冲很厉害呢?大家应该都知道,过冲厉害的原因肯定是信号反射比较厉害,造成信号反射的原因无非就是阻抗不匹配了。上期的仿真实例中,造成反射比较厉害的原因就是驱动器的输出阻抗和与之相连的传输线阻抗不匹配。高速先生带大家来扫描一下驱动器的输出阻抗,搭建如下拓扑结构:

图1

驱动模型和上期选用的一样,这次我们在驱动端加载一个上升沿,扫描中间一段传输线,得到的波形如下图2所示:

图2

由上图2知,当传输线阻抗取35欧姆的时候,电压幅值一开始就达到1.5V左右,反射很小,说明此时传输线的阻抗与驱动器的输出阻抗是近似匹配的。当我们的主线段阻抗偏高到60至65欧姆时,几乎与驱动器的输出阻抗相差一倍,阻抗匹配相差这么多,信号的反射比较严重也就不足为怪了。

2、 从损耗角度分析

在PCB的叠层确定之后,我们控阻抗的主要手段就是调节线宽了。布线时,有时往往会出现布线空间不足的问题,很多工程师会选择走细线。走细线会使得阻抗偏高,且生产制造难度加大,我想很少有工程师从损耗的角度考虑走细线对信号的影响吧,下面我们就来分析一下,线宽变窄对信号的损耗到底有什么影响。

我们分别看看微带线和带状线在线宽变细的情况下,损耗的情况。叠层如下:

图3

我们还是研究阻抗是40,50,60,65欧姆的时候传输线所对应的损耗差异。在以上叠层下,这四种阻抗下,微带线对应的线宽分别是9.5mil,6.2mil,4mil,3.2mil。

在端口阻抗都是50欧姆的条件下,扫描这四种线宽所对应传输线在线长为5inch条件下的S参数。得到传输线的插损与回损如下图4所示:

图4

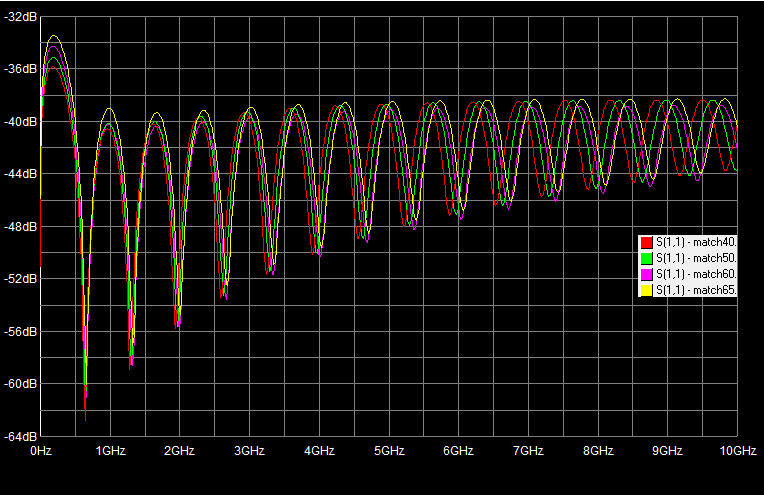

图3所对应的叠层下,阻抗是40,50,60,65欧姆的时候,带状线所对应的线宽分别是10mil,7mil,4.5mil,3.4mil。同样,我们默认传输线端口阻抗是50欧姆,扫描通道S参数,得到的插损与回损曲线分别如图5示:

图5

和我们预想的一样,四种线宽对应插损和回损都是有差异的,线宽越细,对应的插损越小,回损越大。插损反映的是传输到终端能量与总输入能量之比,回损反映的是反射能量和输入能量之比,那么,导致能量没有被完全传输过去的原因,是因为能量被反射到源端,还是能量被通道消耗掉了呢?

原来,上图中的S参数在扫描的时候都做了端口归一化处理,就是在扫描的时候默认端口阻抗都是50欧姆,现在我们扫描的时候改变一下端口的阻抗,使其与被扫描传输线阻抗一致,我们再来看看通道插损与回损的情况,微带线损耗如下图6示:

图6

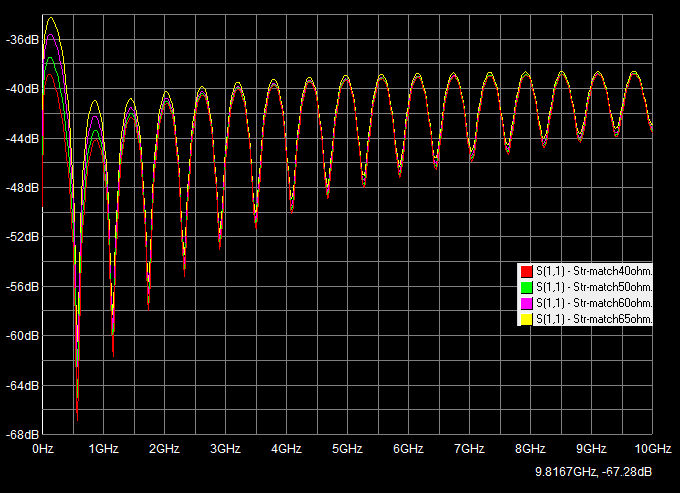

带状线在端口阻抗与传输线阻抗一致的时候,插损与回损曲线如下图7示:

图7

由上图可知,在端口阻抗匹配的情况下,通道的插损与回损曲线差异没有那么大。对于插损来说,带状线与我们想象的一样,线宽越细,损耗越大,但是微带线就没有那么明显。作者认为出现这一现象也是正常的,因为传输线损耗是导体损耗与介质损耗的综合作用,一般情况下是介质损耗占主导作用。微带线和带状线结构不一样,带状线电磁场分布在两个参考层之间,相对较稳定。微带线电磁场有部分分布在空气中,电磁场分布与导体形状也有一定关系,情况比较复杂,由于篇幅关系,这里就不再做深入的分析。

本文简单分析了线宽发生变化时,传输线的损耗情况,可以发现:线宽变化对阻抗的影响比对损耗的影响要大得多,我们应重点关注阻抗不匹配对信号所带来的损害,至于损耗,一般在传输通道很长,速率很高的串行通道中才考虑。解决信号的损耗问题,我们的着眼点也通常在使用DF值更小的板材。

文章没有结束,篇幅关系,敬请期待下期内容…

- 如何设计射频电路及其PCB Layout(06-15)

- 小工具蕴藏大智慧,WEBENCH让设计更轻松(05-20)

- 高速互连SPICE仿真模型(06-29)

- 结合MDA-EDA电子散热仿真解决方案(07-20)

- 软件仿真提高PCB设计效率(09-21)

- saber仿真中的问题处理方法(01-16)