阻抗偏高到60~65欧姆有什么危害(上)

时间:02-08

来源:互联网

点击:

作者:袁波(微信公众号:高速先生)

下面就让我们通过仿真实例来看看,阻抗偏高到60~65欧姆对信号到底有什么危害。

1、 从反射角度分析

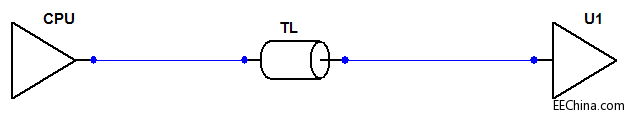

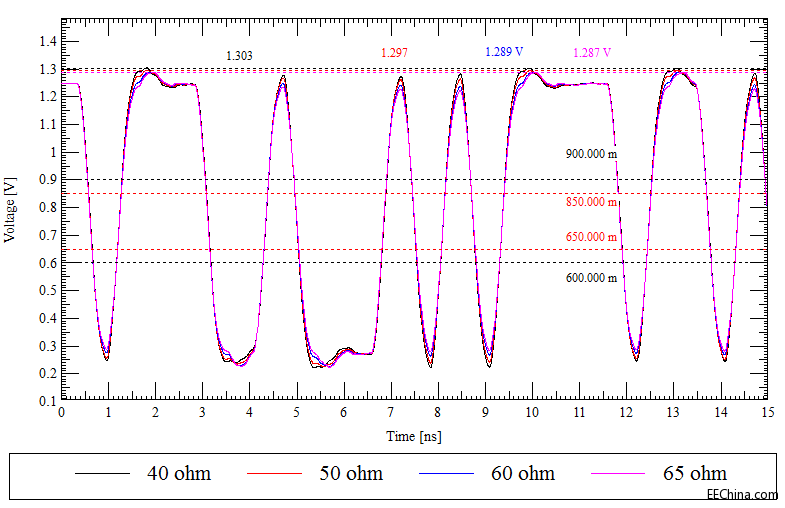

一般情况下,板子上的DDR信号较多,且DDR信号传输速率也不低,我们就以DDR主控芯片为例来仿真验证一下。首先搭建如下拓扑结构:

图1

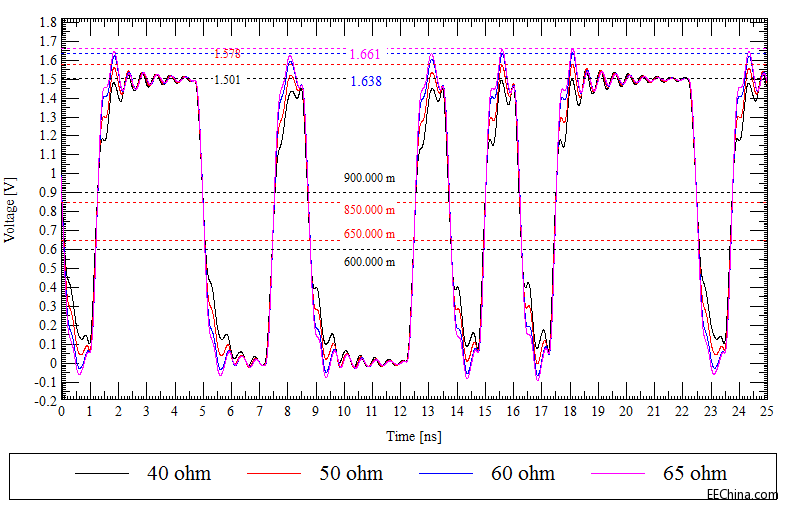

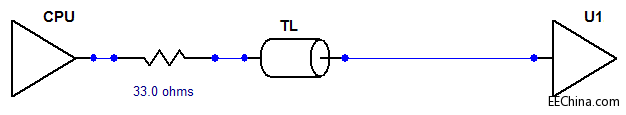

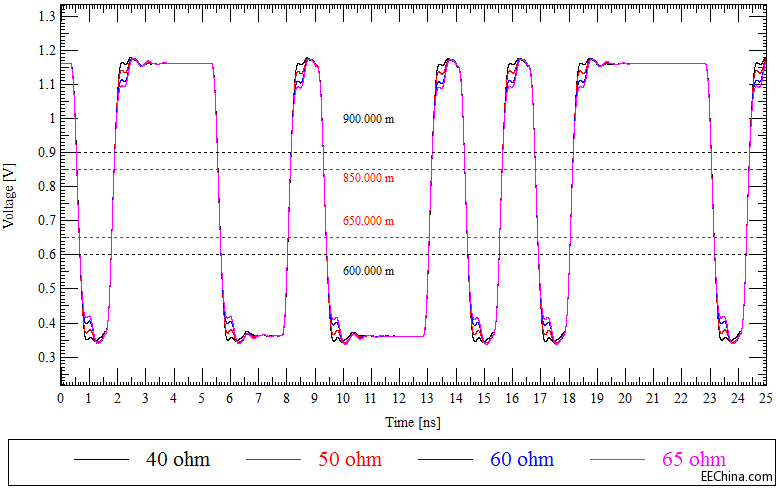

主控芯片是飞思卡尔的P1020,接收端选用的是美光DDR3颗粒。信号速率为800Mbps。中间传输线的阻抗分别取40,50,60,65欧姆,对比U1端接收到的波形,如图2所示:

图2

由图2可知,在传输线阻抗为65欧姆的时候,信号波形的过冲很大,已经超出了芯片的耐压值,像这种情况,作为SI工程师就必须采取一定的措施了,通常是给通道加上端接电阻。那么在有串联电阻端接的情况下,信号波形又是什么样的呢?我们来验证一下。

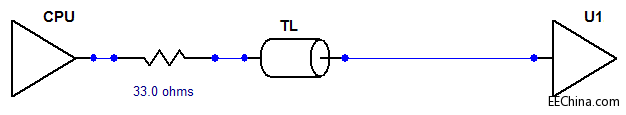

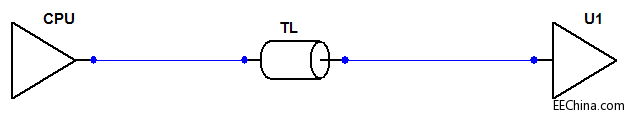

在图1的拓扑结构中加入串联电阻,如下图3所示:

图3

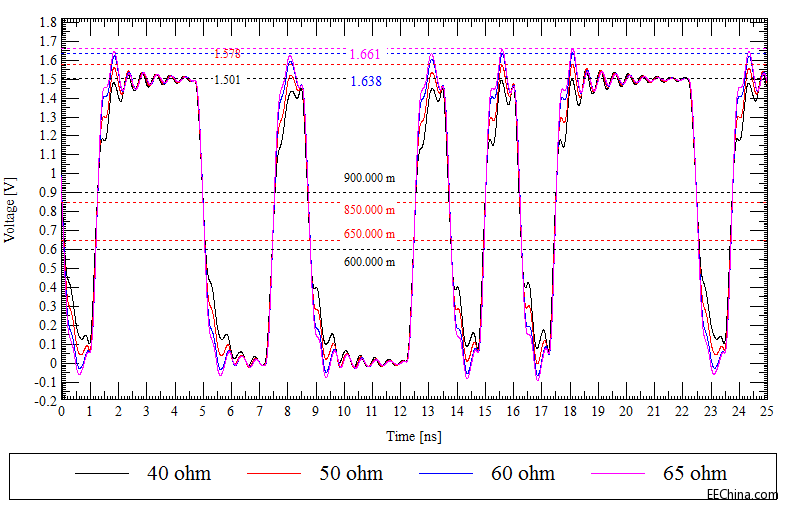

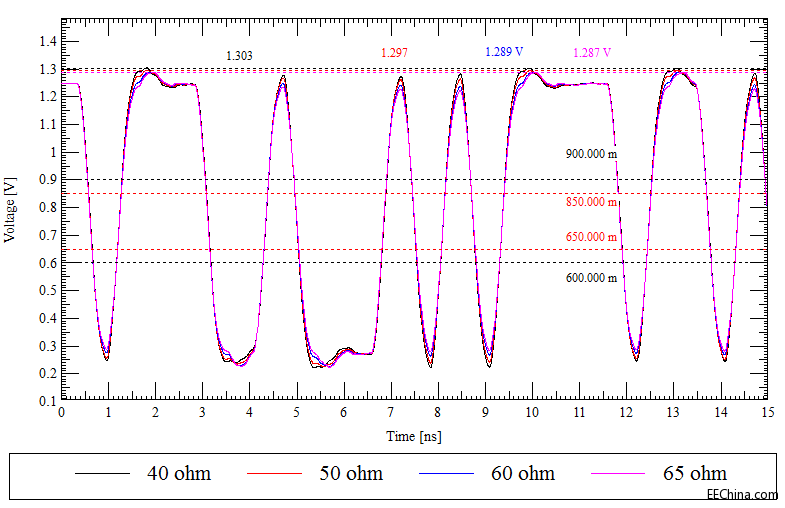

与上面的例子一样,扫描中间传输线阻抗,得到的波形如下图4所示:

图4

由图4可知,和没有加串阻时候的趋势一样,传输线阻抗较高时,信号的过冲大一些。在添加串联电阻之后,信号的过冲被降了下来,可见串阻的作用是很明显的。

加串阻只是其中的一种改善措施,像DDR地址信号一般会加上拉电阻,加上上拉电阻后又会怎样呢?还是来仿真一下,拓扑结构如下图5所示:

图5

同样,扫描中间一段传输线阻抗,波形如下图6:

图6

由图6可知,在有上拉电阻的时候,主线段阻抗变化对波形的影响也是较小的。

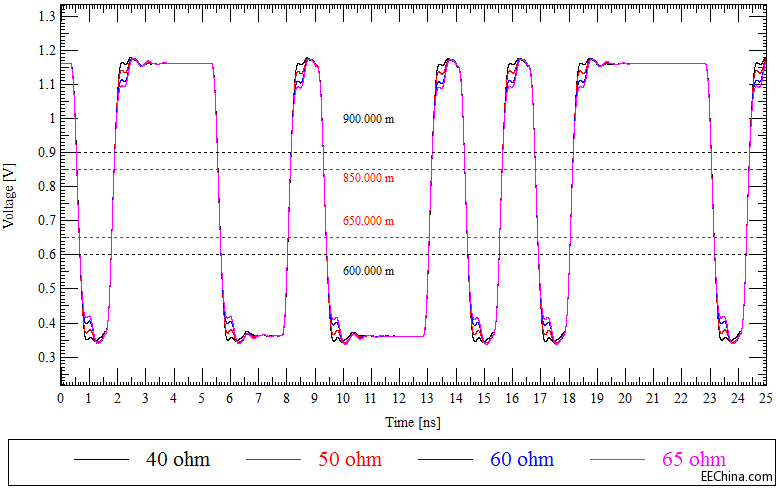

数据信号一般都有终端ODT端接电阻,我们再来看一下在打开ODT状态下,信号线阻抗变化对信号的影响。信号速率为1.6Gbps,接收端使用60欧姆ODT(其实从反射的原理中,我们可以知道ODT取值的大小会影响反射的幅值,这里我们主要比较主线段阻抗变化对信号质量的影响,所以接收端选取了一个固定的ODT阻值)。

仿真波形如下图7所示:

图7

由上图7可知,在打开ODT情况下,过冲很小,且四种阻抗对应的波形差异很小,这样主线段阻抗偏离对信号的影响几乎可以忽略了。

上面仿真实例简单分析了传输通道的四种情况,当然现实的拓扑结构可能要比这个复杂一些,但是上面的这四种情况也是能够说明一些问题的,相信网友们已经发现了一些规律。

由于篇幅限制,从其它角度分析阻抗偏高对信号带来的影响将在下篇文章中呈现,敬请期待…

下面就让我们通过仿真实例来看看,阻抗偏高到60~65欧姆对信号到底有什么危害。

1、 从反射角度分析

一般情况下,板子上的DDR信号较多,且DDR信号传输速率也不低,我们就以DDR主控芯片为例来仿真验证一下。首先搭建如下拓扑结构:

图1

主控芯片是飞思卡尔的P1020,接收端选用的是美光DDR3颗粒。信号速率为800Mbps。中间传输线的阻抗分别取40,50,60,65欧姆,对比U1端接收到的波形,如图2所示:

图2

由图2可知,在传输线阻抗为65欧姆的时候,信号波形的过冲很大,已经超出了芯片的耐压值,像这种情况,作为SI工程师就必须采取一定的措施了,通常是给通道加上端接电阻。那么在有串联电阻端接的情况下,信号波形又是什么样的呢?我们来验证一下。

在图1的拓扑结构中加入串联电阻,如下图3所示:

图3

与上面的例子一样,扫描中间传输线阻抗,得到的波形如下图4所示:

图4

由图4可知,和没有加串阻时候的趋势一样,传输线阻抗较高时,信号的过冲大一些。在添加串联电阻之后,信号的过冲被降了下来,可见串阻的作用是很明显的。

加串阻只是其中的一种改善措施,像DDR地址信号一般会加上拉电阻,加上上拉电阻后又会怎样呢?还是来仿真一下,拓扑结构如下图5所示:

图5

同样,扫描中间一段传输线阻抗,波形如下图6:

图6

由图6可知,在有上拉电阻的时候,主线段阻抗变化对波形的影响也是较小的。

数据信号一般都有终端ODT端接电阻,我们再来看一下在打开ODT状态下,信号线阻抗变化对信号的影响。信号速率为1.6Gbps,接收端使用60欧姆ODT(其实从反射的原理中,我们可以知道ODT取值的大小会影响反射的幅值,这里我们主要比较主线段阻抗变化对信号质量的影响,所以接收端选取了一个固定的ODT阻值)。

仿真波形如下图7所示:

图7

由上图7可知,在打开ODT情况下,过冲很小,且四种阻抗对应的波形差异很小,这样主线段阻抗偏离对信号的影响几乎可以忽略了。

上面仿真实例简单分析了传输通道的四种情况,当然现实的拓扑结构可能要比这个复杂一些,但是上面的这四种情况也是能够说明一些问题的,相信网友们已经发现了一些规律。

由于篇幅限制,从其它角度分析阻抗偏高对信号带来的影响将在下篇文章中呈现,敬请期待…

- 如何设计射频电路及其PCB Layout(06-15)

- 小工具蕴藏大智慧,WEBENCH让设计更轻松(05-20)

- 高速互连SPICE仿真模型(06-29)

- 结合MDA-EDA电子散热仿真解决方案(07-20)

- 软件仿真提高PCB设计效率(09-21)

- saber仿真中的问题处理方法(01-16)