你会做夹具吗?

时间:02-16

来源:互联网

点击:

作者:陈德恒(微信公众号:高速先生)

“你们会做测试夹具吗?”

听到客户在电话那头说的这句话,小陈愣了一下,不禁想起了发生在不久之前的另一段对话:

“你会做层叠吗?”

“会”

“嗯”

••••••

聊天聊到这突然就聊不下去了,这样的问题确实不好回答,到底怎么样才叫是会呢?

有一天,小明新接到一个项目,要求是性能优先不计成本,主芯片是1.0mm pitch、45*45的BGA,有许多高速串行信号,通过板边的连接器连接至背板。

他数了数,BGA大概需要8个走线层才可以把所有走线扇出;信号需要规避串扰,嗯,每一个走线层旁边都双边地平面;

芯片电源较多,至少需要两个电源层,core电源的电流也较大,载流也是需要考虑的对象,那电源那儿就是用2OZ的铜箔吧;

高速信号损耗是一个问题,咱上高速板材;

考虑了介质损耗之后还需要考虑导体损耗,走线不能太细,可是两边都有地,又要保证阻抗,那只能让两边的地远一些了,都使用两张1078的PP/core,让两边都做到6mil左右,这样就可以保证走线的宽度有5-6mil了,同时还避免了单张布造成的玻纤效应,简直一举两得。

高速走线还怕stub的影响,听说当前工艺可以将背钻的stub控制在8mil以内,所有高速走线都背钻就行了。

这样一算,差不多是22层板,板厚在3.8mm左右。

当小明辛辛苦苦的将PCB设计完成,发现了这样一个问题,板边连接器的保护长度是1.2mm,意味着3/5层的走线背钻后连接器无法连接,如果背钻至保护长度之外,第三层走线又可能会留下40mil左右的stub。

小明一咬牙,不是不计成本吗?那我再加4层,高速走线从第7层开始走,这样stub问题就解决了,只是板厚变成了4.5mm。

此时PCB板厂跑出来了说:“小明啊,这个4.5mm的板厚,你看你打的都是10mil孔径的过孔,厚径比都达到18了啊,量产的成品率很低,咱做不到啊,你看是不是能换成14mil的过孔?这样厚径比13,成本也低点是不?”

小明正准备将所有的过孔change一下,仿真组的同事又跑出来了:“明工,咱们不能换啊,用14mil的过孔的话差分阻抗就只有70多了啊,孔又这么长,信号跑不通啊!”

而当小明还在烦恼的时候,材料厂家讪讪地笑了一下:“明兄,咱们材料的可加工性其实还是不错的,不过4.5mm的板厚,BGA的fanout区域容易爆板啊”

小明,卒••••••

看似系统地一条一条教真的能让人真正理解吸收吗?还是要在不断的试错中不断思考,才能慢慢积累经验,直到“会”呢?

“喂,听得到吗?”

小陈的思绪从胡思乱想中被拉了回来。

“嗯嗯,会的。”

“那你帮我看一下,我这里有个用测试夹具测试的项目出了问题。”

小陈看了一下相关的测试报告,大概是一个这样的项目:

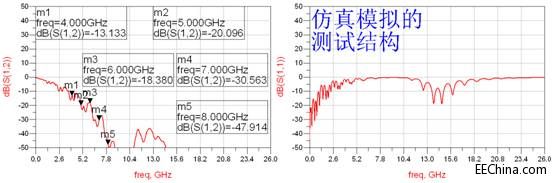

中间绿色的板子为需要测试的DUT,只是很简单几段3-4inch的延时线外加上两个连接器而已。这样子封装的连接器性能通常也不错,板子比较薄,全是表底层走线,过孔做的再差也不应该有太大影响,板上也没有stub,按理来说,DUT的损耗应该挺线性的,不存在太多阻抗不连续点,在小陈的想象中,应该是一个这样子的测试结果:

可是接着往下看测试报告,客户那边的测试结果却吓了我一大跳:

WTF?5GHz处损耗达到21dB?!换算成走线的话这差不多得是30inch的FR4啊!

小陈赶紧往上翻看了一下测试结构,不对啊,测试夹具只有巴掌大,却做出了半米长的效果,这是什么魔法?

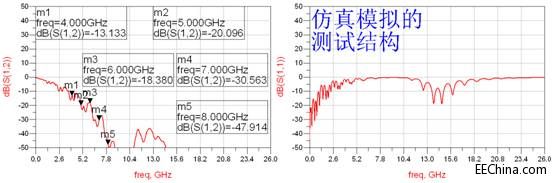

转念一想,小陈释然了,在仿真软件中搭出了推测的拓扑,果不其然:

原来,该夹具使用的是焊接式SMA,并且焊接时将SMA头的针脚全部没入了PCB中,如果走线与SMA头同一面的话,整个SMA头的信号针将成为一个stub,加上底部的锡球,这个stub将超过4mm。并且要保证能将SMA头插进去并且焊上,这里的金属化孔会做的比较大,导致这里阻抗较低,stub将会吸走更多的能量,造成更大的反射。

问题找了出来,客户也放心了。看来测试夹具不仅仅是简单的把被测物延伸出来连上仪器。你还需要根据被测物的结构考虑可测试性;需要去减少夹具本身对测试结果的影响;需要根据信号协议考虑是否要去除夹具本身的影响;需要考虑什么样的测试方案是成本最低,效率最高的;需要考虑如何能覆盖所有的测试需求••••这些东西跟层叠一样,是需要进行取舍的。

“你们会做测试夹具吗?”

听到客户在电话那头说的这句话,小陈愣了一下,不禁想起了发生在不久之前的另一段对话:

“你会做层叠吗?”

“会”

“嗯”

••••••

聊天聊到这突然就聊不下去了,这样的问题确实不好回答,到底怎么样才叫是会呢?

有一天,小明新接到一个项目,要求是性能优先不计成本,主芯片是1.0mm pitch、45*45的BGA,有许多高速串行信号,通过板边的连接器连接至背板。

他数了数,BGA大概需要8个走线层才可以把所有走线扇出;信号需要规避串扰,嗯,每一个走线层旁边都双边地平面;

芯片电源较多,至少需要两个电源层,core电源的电流也较大,载流也是需要考虑的对象,那电源那儿就是用2OZ的铜箔吧;

高速信号损耗是一个问题,咱上高速板材;

考虑了介质损耗之后还需要考虑导体损耗,走线不能太细,可是两边都有地,又要保证阻抗,那只能让两边的地远一些了,都使用两张1078的PP/core,让两边都做到6mil左右,这样就可以保证走线的宽度有5-6mil了,同时还避免了单张布造成的玻纤效应,简直一举两得。

高速走线还怕stub的影响,听说当前工艺可以将背钻的stub控制在8mil以内,所有高速走线都背钻就行了。

这样一算,差不多是22层板,板厚在3.8mm左右。

当小明辛辛苦苦的将PCB设计完成,发现了这样一个问题,板边连接器的保护长度是1.2mm,意味着3/5层的走线背钻后连接器无法连接,如果背钻至保护长度之外,第三层走线又可能会留下40mil左右的stub。

小明一咬牙,不是不计成本吗?那我再加4层,高速走线从第7层开始走,这样stub问题就解决了,只是板厚变成了4.5mm。

此时PCB板厂跑出来了说:“小明啊,这个4.5mm的板厚,你看你打的都是10mil孔径的过孔,厚径比都达到18了啊,量产的成品率很低,咱做不到啊,你看是不是能换成14mil的过孔?这样厚径比13,成本也低点是不?”

小明正准备将所有的过孔change一下,仿真组的同事又跑出来了:“明工,咱们不能换啊,用14mil的过孔的话差分阻抗就只有70多了啊,孔又这么长,信号跑不通啊!”

而当小明还在烦恼的时候,材料厂家讪讪地笑了一下:“明兄,咱们材料的可加工性其实还是不错的,不过4.5mm的板厚,BGA的fanout区域容易爆板啊”

小明,卒••••••

看似系统地一条一条教真的能让人真正理解吸收吗?还是要在不断的试错中不断思考,才能慢慢积累经验,直到“会”呢?

“喂,听得到吗?”

小陈的思绪从胡思乱想中被拉了回来。

“嗯嗯,会的。”

“那你帮我看一下,我这里有个用测试夹具测试的项目出了问题。”

小陈看了一下相关的测试报告,大概是一个这样的项目:

中间绿色的板子为需要测试的DUT,只是很简单几段3-4inch的延时线外加上两个连接器而已。这样子封装的连接器性能通常也不错,板子比较薄,全是表底层走线,过孔做的再差也不应该有太大影响,板上也没有stub,按理来说,DUT的损耗应该挺线性的,不存在太多阻抗不连续点,在小陈的想象中,应该是一个这样子的测试结果:

可是接着往下看测试报告,客户那边的测试结果却吓了我一大跳:

WTF?5GHz处损耗达到21dB?!换算成走线的话这差不多得是30inch的FR4啊!

小陈赶紧往上翻看了一下测试结构,不对啊,测试夹具只有巴掌大,却做出了半米长的效果,这是什么魔法?

转念一想,小陈释然了,在仿真软件中搭出了推测的拓扑,果不其然:

原来,该夹具使用的是焊接式SMA,并且焊接时将SMA头的针脚全部没入了PCB中,如果走线与SMA头同一面的话,整个SMA头的信号针将成为一个stub,加上底部的锡球,这个stub将超过4mm。并且要保证能将SMA头插进去并且焊上,这里的金属化孔会做的比较大,导致这里阻抗较低,stub将会吸走更多的能量,造成更大的反射。

问题找了出来,客户也放心了。看来测试夹具不仅仅是简单的把被测物延伸出来连上仪器。你还需要根据被测物的结构考虑可测试性;需要去减少夹具本身对测试结果的影响;需要根据信号协议考虑是否要去除夹具本身的影响;需要考虑什么样的测试方案是成本最低,效率最高的;需要考虑如何能覆盖所有的测试需求••••这些东西跟层叠一样,是需要进行取舍的。

- 高密度印刷线路板的功能测试(01-22)

- 优化数字视频设备的BNC连接器PCB占位设计(01-16)

- 对设计PCB时的抗静电放电方法简单介绍(03-14)

- 电路板电镀中4种特殊的电镀方法(08-04)

- PCB电路设计中磁珠的选用(09-05)

- 手工贴片,手工焊接过程(08-04)