一博科技 | DDR线长匹配与时序(下)

时间:12-23

来源:互联网

点击:

上篇文章我们用仿真实例向大家展示了DDR中地址相对于时钟的建立时间与保持时间。那么数据信号相对于DQS又是什么样的关系呢?我们知道,DDR和普通的SDRAM相比起来,读取速率为普通SDRAM的两倍,这个要怎么理解?原来SDRAM在写入或者读取数据的时候是靠上升沿或者下降沿来触发的,请注意,这里仅仅是上升沿或者下降沿,并不是上升沿和下降沿同时有效。如果时钟频率是800MHz,那么对应的数据率就为800Mbps。但是DDR的数据信号却是双倍速率的,如果DQS频率为800MHz,那么数据信号的速率就应该为1600Mbps。

下面通过具体的仿真实例来看一下。

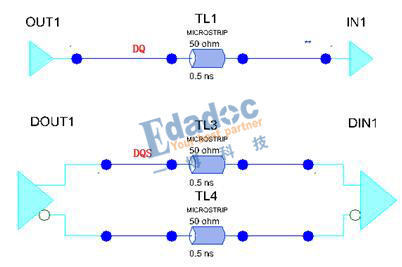

仿真通道如上图所示,驱动端和接收端为某芯片公司的IBIS模型,仿真波形如下:

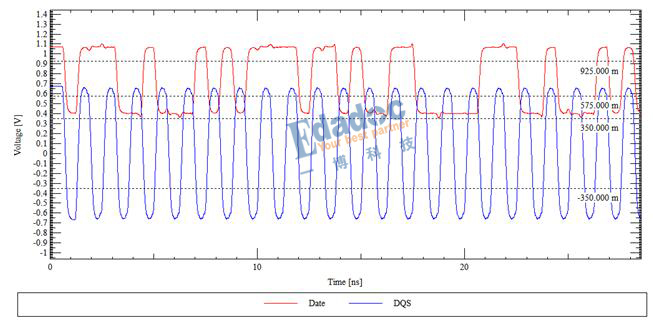

我们将DQS和DQ信号同时生成眼图,在一个窗口观测,结果如下:

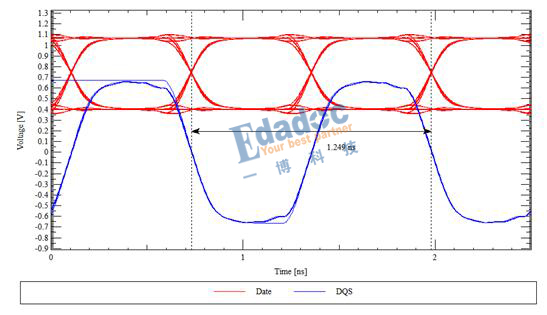

这里,作者本来是想仿真DDR在写操作的时候DQS和DQ之间的时序对应关系。在之前的文章中,我们知道,在写操作的时候,是以高低电平的中点为触发点的,上面眼图中的波形对应关系显然不能完成数据的写入,因为DQS的边沿和数据信号翻转的边沿基本是对齐的。

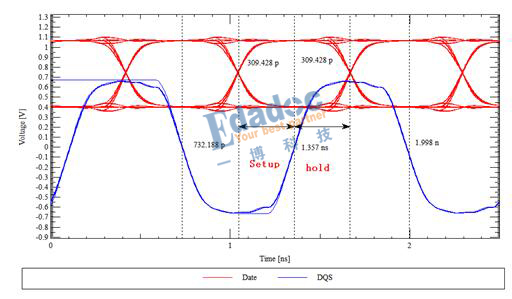

在仿真的时候只是简单的将两波形放在了一起,因为DQ和DQS的传输通道长度是一样的,所以他们的边沿是对齐的。实际工作的时候,主控芯片会有一个调节机制。一般数据信号会比DQS提前四分之一周期被释放出来,实际上,在颗粒端接收到的波形对应关系应该是这样的:

通过主控芯片的调节之后,DQS的边沿就和DQ信号位的中心对齐了,这样就能保证数据在传输到接收端有足够的建立时间与保持时间,就算DQS与DQ之间的线长匹配的不是那么严格,也会有一些时序裕量。

说了这么多,其实我们要解决的根本问题还是长度匹配的范围问题。在理解了这些基础问题之后,我们需要做的就是将这些时间参数转化为延时。线长匹配范围怎么计算?下面通过具体实例来看看时序裕量是怎么计算的。先简单的来看一张图

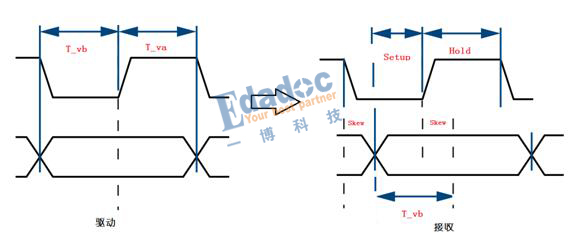

上图中,T_vb与T_va表示的是主控芯片在输出数据时时钟与数据之间的时序参数。在理想情况下,时钟边沿和数据电平的中心是对齐的,由于时钟和数据传输通道不等长,使得时钟边沿没有和数据脉冲的中间位置对其,使得建立时间的裕量变小。

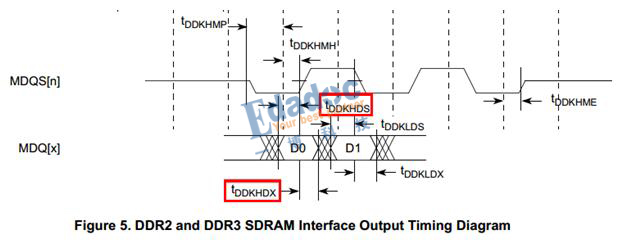

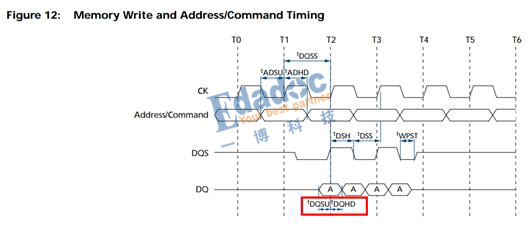

下面我们通过具体实例来看看时序的计算,下图是Freescale MPC8572 DDR主控芯片手册,这张图片定义了从芯片出来的时候,DQS与DQ之间的相位关系。

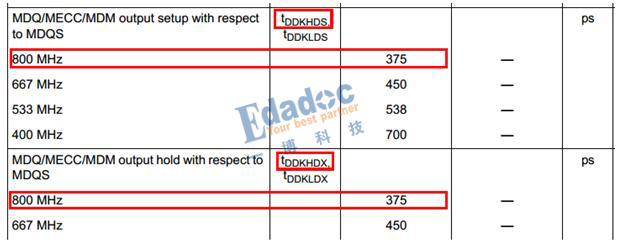

颗粒端为美光DDR,该芯片的时序图以及时序参数如下图所示,这张图片则定义了颗粒端芯片识别信号所需要的建立时间与保持时间。

我们用T_pcbskew来表示DQ与DQS之间的延时偏差,如果想要得到足够的时序裕量,则延时偏差要满足以下关系:

代入数据,有:

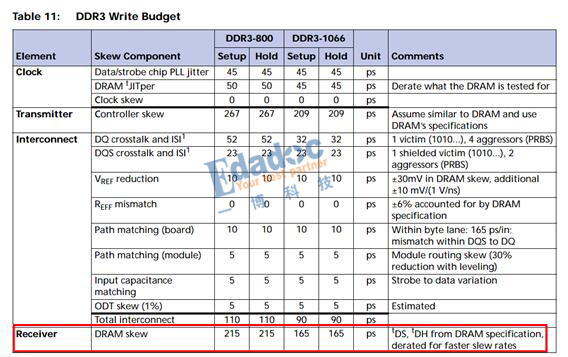

这样,如果传输线的速度按照6mil/ps来计算,T_pcbskew为+/-960mil。大家会发现裕量很大,当然这只是最理想情况,没有考虑时钟抖动以及数据信号的抖动,以及串扰、码间干扰带来的影响,如果把这些因素都考虑进来,留给我们布线偏差的裕量就比较小了。

下面通过具体的仿真实例来看一下。

图1 DQ 与 DQS仿真示意

仿真通道如上图所示,驱动端和接收端为某芯片公司的IBIS模型,仿真波形如下:

图2 DQ与DQS仿真波形

我们将DQS和DQ信号同时生成眼图,在一个窗口观测,结果如下:

图3 DQ 与 DQS眼图

这里,作者本来是想仿真DDR在写操作的时候DQS和DQ之间的时序对应关系。在之前的文章中,我们知道,在写操作的时候,是以高低电平的中点为触发点的,上面眼图中的波形对应关系显然不能完成数据的写入,因为DQS的边沿和数据信号翻转的边沿基本是对齐的。

在仿真的时候只是简单的将两波形放在了一起,因为DQ和DQS的传输通道长度是一样的,所以他们的边沿是对齐的。实际工作的时候,主控芯片会有一个调节机制。一般数据信号会比DQS提前四分之一周期被释放出来,实际上,在颗粒端接收到的波形对应关系应该是这样的:

图4 平移后的眼图

通过主控芯片的调节之后,DQS的边沿就和DQ信号位的中心对齐了,这样就能保证数据在传输到接收端有足够的建立时间与保持时间,就算DQS与DQ之间的线长匹配的不是那么严格,也会有一些时序裕量。

说了这么多,其实我们要解决的根本问题还是长度匹配的范围问题。在理解了这些基础问题之后,我们需要做的就是将这些时间参数转化为延时。线长匹配范围怎么计算?下面通过具体实例来看看时序裕量是怎么计算的。先简单的来看一张图

图5 延时偏差对时序的影响

上图中,T_vb与T_va表示的是主控芯片在输出数据时时钟与数据之间的时序参数。在理想情况下,时钟边沿和数据电平的中心是对齐的,由于时钟和数据传输通道不等长,使得时钟边沿没有和数据脉冲的中间位置对其,使得建立时间的裕量变小。

下面我们通过具体实例来看看时序的计算,下图是Freescale MPC8572 DDR主控芯片手册,这张图片定义了从芯片出来的时候,DQS与DQ之间的相位关系。

图6 MPC8572时序图

图7 MPC8572时序参数

颗粒端为美光DDR,该芯片的时序图以及时序参数如下图所示,这张图片则定义了颗粒端芯片识别信号所需要的建立时间与保持时间。

图8 DDR颗粒时序图以及时序参数

我们用T_pcbskew来表示DQ与DQS之间的延时偏差,如果想要得到足够的时序裕量,则延时偏差要满足以下关系:

T_pcbskew<T_vb-T_setup

T_pcbskew>T_hold-T_va

代入数据,有:

T_vb-T_setup=375-215=160ps

T_hold-T_va=-160ps

这样,如果传输线的速度按照6mil/ps来计算,T_pcbskew为+/-960mil。大家会发现裕量很大,当然这只是最理想情况,没有考虑时钟抖动以及数据信号的抖动,以及串扰、码间干扰带来的影响,如果把这些因素都考虑进来,留给我们布线偏差的裕量就比较小了。

- 如何设计射频电路及其PCB Layout(06-15)

- 小工具蕴藏大智慧,WEBENCH让设计更轻松(05-20)

- 高速互连SPICE仿真模型(06-29)

- 结合MDA-EDA电子散热仿真解决方案(07-20)

- 软件仿真提高PCB设计效率(09-21)

- saber仿真中的问题处理方法(01-16)