一博科技 | DDR3布局的那些事儿(二)

时间:12-09

来源:互联网

点击:

DDR3的设计有着严格等长要求,归结起来分为两类(以64位的DDR3为例): 数据 (DQ,DQS,DQM):组内等长,误差控制在20MIL以内,组间不需要考虑等长;地址、控制、时钟信号:地址、控制信号以时钟作参考,误差控制在100MIL以内,Address、Control与CLK归为一组,因为Address、Control是以CLK的下降沿触发的由DDR控制器输出,DDR颗粒由CLK的上升沿锁存Address、Control总线上的状态,所以需要严格控制CLK与Address/Command、Control之间的时序关系,确保DDR颗粒能够获得足够的建立和保持时间。

关注等长的目的就是为了等时,绕等长时需要注意以下几点:

1.确认芯片是否有Pin-delay,绕线时要确保Pin-delay开关已经打开;

2.同组信号走在同层,保证不会因换层影响实际的等时;同样的换层结构,换层前后的等长要匹配,即时等长;不同层的传播延时需要考虑,如走在表层与走在内层,其传播速度是不一样的,所以在走线的时候需要考虑,表层走线尽量短,让其差别尽量小(这也是为什么Intel的很多GUIDE上面要求,表层的走线长度不超过250MIL等要求的原因);

3. Z轴的延时:在严格要求的情况下,需要把Z轴的延时开关也打开,做等长时需要考虑(ALLEGRO中层叠需要设置好,Z轴延时才是对的)。

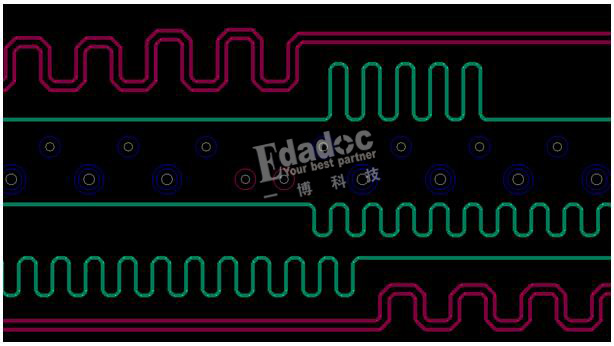

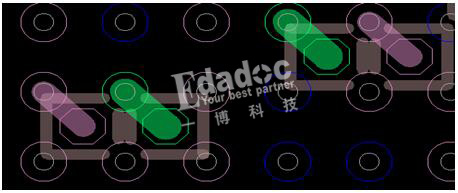

4.蛇形绕线时单线按3W,差分按5W绕线(W为线宽)。且保证各BUS信号组内间距按3H, 不同组组间间距为5H (H为到主参考平面间距),DQS和CLK 距离其他信号间距做到5H以上。单线和差分绕线方式如下图1所示:

而另一个核心重点便是电源处理。DDR3中有三类电源,它们是VDD(1.5V)、VTT(0.75V)、VREF(0.75V,包括VREFCA和VREFDQ)。

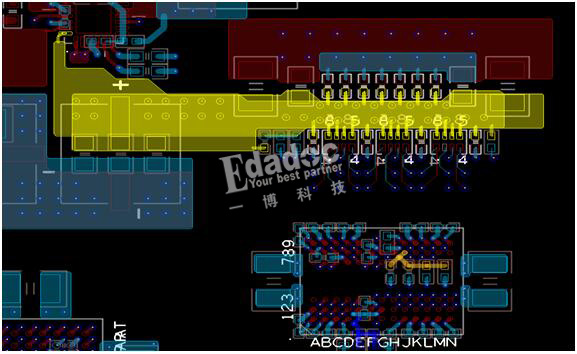

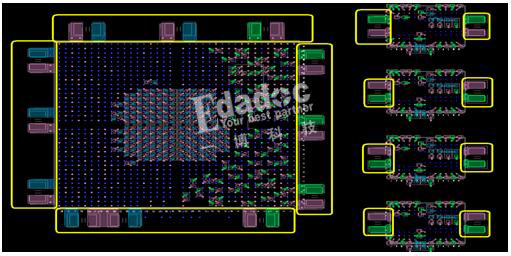

1. VDD(1.5V)电源是DDR3的核心电源,其引脚分布比较散,且电流相对会比较大,需要在电源平面分配一个区域给VDD(1.5V);VDD的容差要求是5%,详细在JEDEC里有叙述。通过电源层的平面电容和专用的一定数量的去耦电容,可以做到电源完整性。VDD电源平面处理如下图2所示:

2. VTT电源,它不仅有严格的容差性,而且还有很大的瞬间电流;可以通过增加去耦电容来实现它的目标阻抗匹配;由于VTT是集中在终端的上拉电阻处,不是很分散,且对电流有一定的要求,在处理VTT电源时,一般是在元件面同层通过铺铜直接连接,铜皮要有一定宽度(120MIl)。VTT电源处理如图3所示:

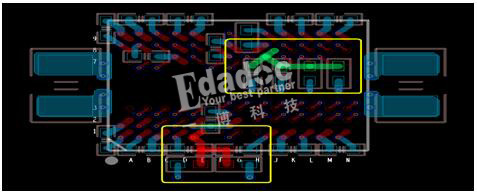

3.VREF电源 。 VREF要求更加严格的容差性,但是它承载的电流比较小。它不需要非常宽的走线,且通过一两个去耦电容就可以达到目标阻抗的要求。DDR3的VERF电源已经分为VREFCA和VREFDQ两部分,且每个DDR3颗粒都有单独的VREFCA和VREFDQ,因其相对比较独立,电流也不大,布线处理时也建议用与器件同层的铜皮或走线直接连接,无须在电源平面层为其分配电源。注意铺铜或走线时,要先经过电容再接到芯片的电源引脚,不要从分压电阻那里直接接到芯片的电源引脚。VREF电源处理如图4所示:

滤波电容的FANOUT 小电容尽量靠近相应的电源引脚,电容的引线也要尽量短,并减少电源或地共用过孔;

Bulk电容的FANOUT

电源的Bulk电容一般在设计中起到的是储能滤波的作用,在做Fanout时要多打孔,建议2个孔以上,电容越大需要过孔越多,也可以用铺铜的形式来做。电容的电源孔和地孔尽量靠近打,如图6所示。

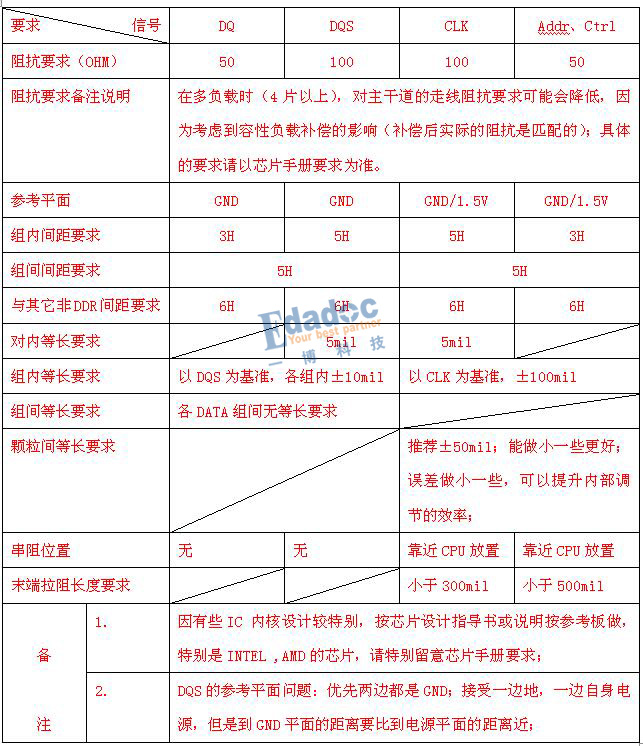

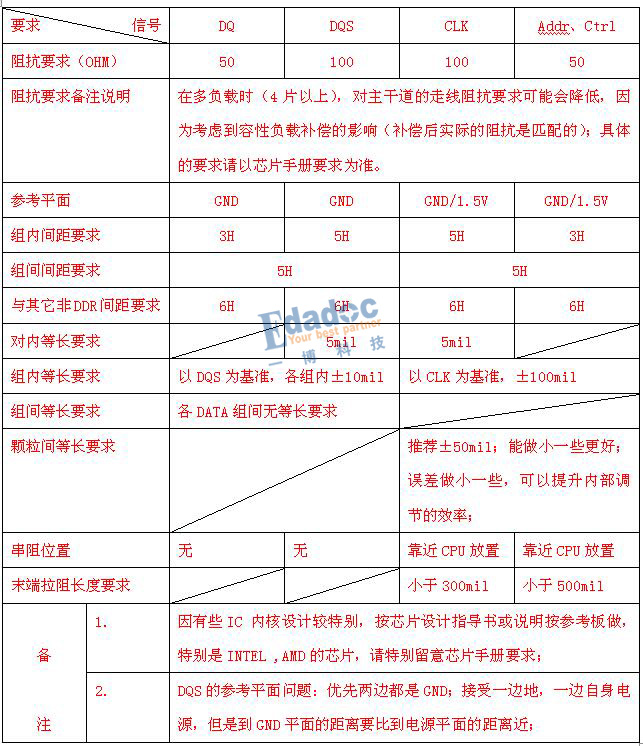

综上所述,我们常规DDR3的走线设计总结如下表:

关注等长的目的就是为了等时,绕等长时需要注意以下几点:

1.确认芯片是否有Pin-delay,绕线时要确保Pin-delay开关已经打开;

2.同组信号走在同层,保证不会因换层影响实际的等时;同样的换层结构,换层前后的等长要匹配,即时等长;不同层的传播延时需要考虑,如走在表层与走在内层,其传播速度是不一样的,所以在走线的时候需要考虑,表层走线尽量短,让其差别尽量小(这也是为什么Intel的很多GUIDE上面要求,表层的走线长度不超过250MIL等要求的原因);

3. Z轴的延时:在严格要求的情况下,需要把Z轴的延时开关也打开,做等长时需要考虑(ALLEGRO中层叠需要设置好,Z轴延时才是对的)。

4.蛇形绕线时单线按3W,差分按5W绕线(W为线宽)。且保证各BUS信号组内间距按3H, 不同组组间间距为5H (H为到主参考平面间距),DQS和CLK 距离其他信号间距做到5H以上。单线和差分绕线方式如下图1所示:

图1.单线和差分绕线方式示例

而另一个核心重点便是电源处理。DDR3中有三类电源,它们是VDD(1.5V)、VTT(0.75V)、VREF(0.75V,包括VREFCA和VREFDQ)。

1. VDD(1.5V)电源是DDR3的核心电源,其引脚分布比较散,且电流相对会比较大,需要在电源平面分配一个区域给VDD(1.5V);VDD的容差要求是5%,详细在JEDEC里有叙述。通过电源层的平面电容和专用的一定数量的去耦电容,可以做到电源完整性。VDD电源平面处理如下图2所示:

图2:VDD电源处理

2. VTT电源,它不仅有严格的容差性,而且还有很大的瞬间电流;可以通过增加去耦电容来实现它的目标阻抗匹配;由于VTT是集中在终端的上拉电阻处,不是很分散,且对电流有一定的要求,在处理VTT电源时,一般是在元件面同层通过铺铜直接连接,铜皮要有一定宽度(120MIl)。VTT电源处理如图3所示:

图3:VTT电源

3.VREF电源 。 VREF要求更加严格的容差性,但是它承载的电流比较小。它不需要非常宽的走线,且通过一两个去耦电容就可以达到目标阻抗的要求。DDR3的VERF电源已经分为VREFCA和VREFDQ两部分,且每个DDR3颗粒都有单独的VREFCA和VREFDQ,因其相对比较独立,电流也不大,布线处理时也建议用与器件同层的铜皮或走线直接连接,无须在电源平面层为其分配电源。注意铺铜或走线时,要先经过电容再接到芯片的电源引脚,不要从分压电阻那里直接接到芯片的电源引脚。VREF电源处理如图4所示:

图4:VREF电源

滤波电容的FANOUT 小电容尽量靠近相应的电源引脚,电容的引线也要尽量短,并减少电源或地共用过孔;

图5 : 小滤波电容的Fanout

Bulk电容的FANOUT

电源的Bulk电容一般在设计中起到的是储能滤波的作用,在做Fanout时要多打孔,建议2个孔以上,电容越大需要过孔越多,也可以用铺铜的形式来做。电容的电源孔和地孔尽量靠近打,如图6所示。

图6:储能电容的Fanout

综上所述,我们常规DDR3的走线设计总结如下表:

- 射频开关模块功能电路PCB板的设计(10-25)

- protel99快捷键大全(10-26)

- 78%的硬件失效罪魁祸首——焊接问题(03-06)

- 2012让工作更智能的六大PCB设计技术策略(04-12)

- Altium Designer学习笔记(09-07)

- 78%的硬件失效是由于焊接问题导致(09-08)