DDRx的关键技术介绍(中)

时间:10-27

来源:互联网

点击:

作者:一博科技

在DDRx里面经常会被一些缩写误扰,如OCD、OCT和ODT,我想有同样困扰的大有人在,今天还是继续上一篇的关键技术来介绍一下大家的这些困扰吧。

片外驱动调校OCD(Off-Chip Driver)

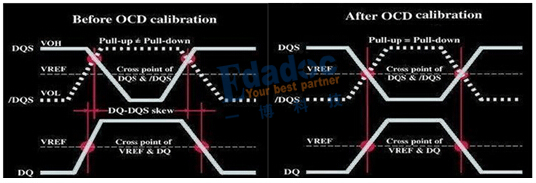

OCD是在DDR-II开始加入的新功能,而且这个功能是可选的,有的资料上面又叫离线驱动调整。OCD的主要作用在于调整I/O接口端的电压,来补偿上拉与下拉电阻值,从而调整DQS与DQ之间的同步确保信号的完整与可靠性。调校期间,分别测试DQS高电平和DQ高电平,以及DQS低电平和DQ高电平的同步情况。如果不满足要求,则通过设定突发长度的地址线来传送上拉/下拉电阻等级(加一档或减一档),直到测试合格才退出OCD操作,通过OCD操作来减少DQ、DQS的倾斜从而提高信号的完整性及控制电压来提高信号品质。具体调校如下图一所示。

ODT(On-Die Termination,片内终结)

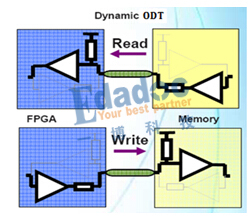

ODT也是DDR2相对于DDR1的关键技术突破,所谓的终结(端接),就是让信号被电路的终端吸收掉,而不会在电路上形成反射,造成对后面信号的影响。顾名思义,ODT就是将端接电阻移植到了芯片内部,主板上不再有端接电路。在进入DDR时代,DDR内存对工作环境提出更高的要求,如果先前发出的信号不能被电路终端完全吸收掉而在电路上形成反射现象,就会对后面信号的影响造成运算出错。因此目前支持DDR主板都是通过采用终结电阻来解决这个问题。由于每根数据线至少需要一个终结电阻,这意味着每块DDR主板需要大量的终结电阻,这也无形中增加了主板的生产成本,而且由于不同的内存模组对终结电阻的要求不可能完全一样,也造成了所谓的“内存兼容性问题”。 而在DDR-II中加入了ODT功能,当在DRAM模组工作时把终结电阻器关掉,而对于不工作的DRAM模组则进行终结操作,起到减少信号反射的作用,如下图二所示。

ODT的功能与禁止由主控芯片控制,在开机进行EMRS时进行设置,ODT所终结的信号包括DQS、DQS#、DQ、DM等。这样可以产生更干净的信号品质,从而产生更高的内存时钟频率速度。而将终结电阻设计在内存芯片之上还可以简化主板的设计,降低了主板的成本,而且终结电阻器可以和内存颗粒的“特性”相符,从而减少内存与主板的兼容问题的出现。

重置(Reset)

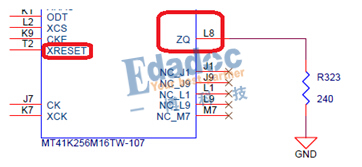

重置是DDR3新增的一项重要功能,并为此专门准备了一个引脚。这一引脚将使DDR3的初始化处理变得简单。当Reset命令有效时,DDR3 内存将停止所有的操作,并切换至最少量活动的状态,以节约电力。在Reset期间,DDR3内存将关闭内在的大部分功能,所有数据接收与发送器都将关闭,且所有内部的程序装置将复位,DLL(延迟锁相环路)与时钟电路将停止工作,甚至不理睬数据总线上的任何动静。这样一来,该功能将使DDR3达到最节省电力的目的,新增的引脚如下图三所示。

如上图三所示,ZQ也是一个新增的引脚,在这个引脚上接有一个240欧姆的低公差参考电阻。这个引脚通过一个命令集,通过片上校准引擎(ODCE,On-Die Calibration Engine)来自动校验数据输出驱动器导通电阻与ODT的终结电阻值。当系统发出这一指令之后,将用相应的时钟周期(在加电与初始化之后用512个时钟周期,在退出自刷新操作后用256时钟周期、在其他情况下用64个时钟周期)对导通电阻和ODT电阻进行重新校准。

VREFCA & VREFDQ

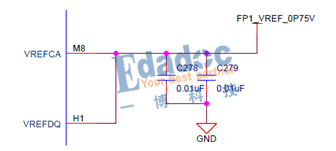

对于内存系统工作非常重要的参考电压信号VREF,在DDR3系统中将VREF分为两个信号。一个是为命令与地址信号服务的VREFCA,另一个是为数据总线服务的VREFDQ,它将有效的提高系统数据总线的信噪等级,如下图四所示。

在DDRx里面经常会被一些缩写误扰,如OCD、OCT和ODT,我想有同样困扰的大有人在,今天还是继续上一篇的关键技术来介绍一下大家的这些困扰吧。

片外驱动调校OCD(Off-Chip Driver)

OCD是在DDR-II开始加入的新功能,而且这个功能是可选的,有的资料上面又叫离线驱动调整。OCD的主要作用在于调整I/O接口端的电压,来补偿上拉与下拉电阻值,从而调整DQS与DQ之间的同步确保信号的完整与可靠性。调校期间,分别测试DQS高电平和DQ高电平,以及DQS低电平和DQ高电平的同步情况。如果不满足要求,则通过设定突发长度的地址线来传送上拉/下拉电阻等级(加一档或减一档),直到测试合格才退出OCD操作,通过OCD操作来减少DQ、DQS的倾斜从而提高信号的完整性及控制电压来提高信号品质。具体调校如下图一所示。

图一 OCD

ODT(On-Die Termination,片内终结)

ODT也是DDR2相对于DDR1的关键技术突破,所谓的终结(端接),就是让信号被电路的终端吸收掉,而不会在电路上形成反射,造成对后面信号的影响。顾名思义,ODT就是将端接电阻移植到了芯片内部,主板上不再有端接电路。在进入DDR时代,DDR内存对工作环境提出更高的要求,如果先前发出的信号不能被电路终端完全吸收掉而在电路上形成反射现象,就会对后面信号的影响造成运算出错。因此目前支持DDR主板都是通过采用终结电阻来解决这个问题。由于每根数据线至少需要一个终结电阻,这意味着每块DDR主板需要大量的终结电阻,这也无形中增加了主板的生产成本,而且由于不同的内存模组对终结电阻的要求不可能完全一样,也造成了所谓的“内存兼容性问题”。 而在DDR-II中加入了ODT功能,当在DRAM模组工作时把终结电阻器关掉,而对于不工作的DRAM模组则进行终结操作,起到减少信号反射的作用,如下图二所示。

图二 ODT端接示意图

ODT的功能与禁止由主控芯片控制,在开机进行EMRS时进行设置,ODT所终结的信号包括DQS、DQS#、DQ、DM等。这样可以产生更干净的信号品质,从而产生更高的内存时钟频率速度。而将终结电阻设计在内存芯片之上还可以简化主板的设计,降低了主板的成本,而且终结电阻器可以和内存颗粒的“特性”相符,从而减少内存与主板的兼容问题的出现。

重置(Reset)

重置是DDR3新增的一项重要功能,并为此专门准备了一个引脚。这一引脚将使DDR3的初始化处理变得简单。当Reset命令有效时,DDR3 内存将停止所有的操作,并切换至最少量活动的状态,以节约电力。在Reset期间,DDR3内存将关闭内在的大部分功能,所有数据接收与发送器都将关闭,且所有内部的程序装置将复位,DLL(延迟锁相环路)与时钟电路将停止工作,甚至不理睬数据总线上的任何动静。这样一来,该功能将使DDR3达到最节省电力的目的,新增的引脚如下图三所示。

图三 Reset及ZQ引脚

如上图三所示,ZQ也是一个新增的引脚,在这个引脚上接有一个240欧姆的低公差参考电阻。这个引脚通过一个命令集,通过片上校准引擎(ODCE,On-Die Calibration Engine)来自动校验数据输出驱动器导通电阻与ODT的终结电阻值。当系统发出这一指令之后,将用相应的时钟周期(在加电与初始化之后用512个时钟周期,在退出自刷新操作后用256时钟周期、在其他情况下用64个时钟周期)对导通电阻和ODT电阻进行重新校准。

VREFCA & VREFDQ

对于内存系统工作非常重要的参考电压信号VREF,在DDR3系统中将VREF分为两个信号。一个是为命令与地址信号服务的VREFCA,另一个是为数据总线服务的VREFDQ,它将有效的提高系统数据总线的信噪等级,如下图四所示。

- 如何调试新设计的电路板(08-26)

- 怎样去调试一个新设计的电路板(09-25)

- 浅谈集成电路对EMI设计的影响(09-10)

- 印制电路板制作的基础知识(08-04)

- 线路板调试方法(08-12)

- 印制电路板设计经验(08-04)