如何计算阻抗(下)

时间:03-01

来源:互联网

点击:

作者:刘为霞 一博科技高速先生团队队员

上次讲到了阻抗计算和工艺制程之间的一些"权衡的艺术",主要是为了达到我们阻抗管控目的的同时,也能保证工艺加工的方便,以及尽量降低加工成本。接下来,就具体说说,利用SI9000计算阻抗的具体过程。

如何计算阻抗

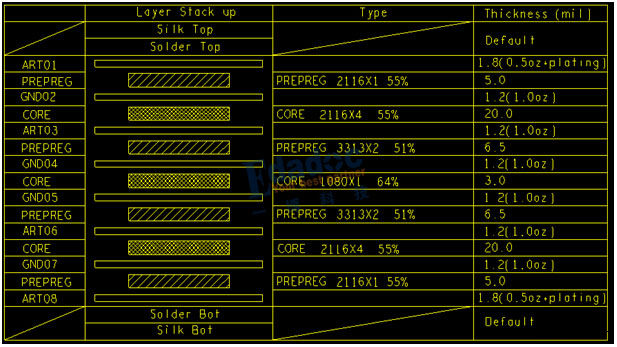

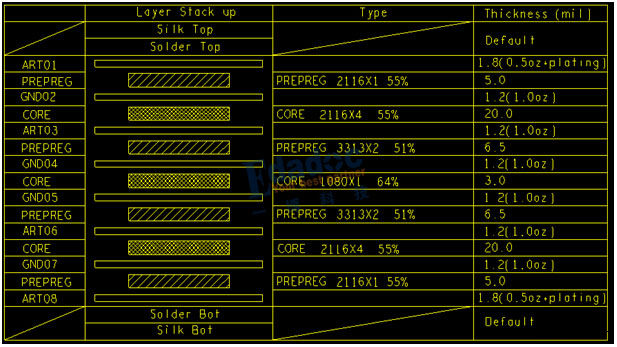

对于阻抗计算而言,层叠设置是先决条件,首先必选先设置好单板的具体层叠信息,下面是一个常见八层板的层叠信息,以这个为例子,看看阻抗计算的一些注意事项。

图一

对于信号线而言,在板子上实现的形式又分为微带线和带状线,两者的不同,使得阻抗计算选择的结构不一致,下面分别讨论这两种常见的阻抗计算的情况。

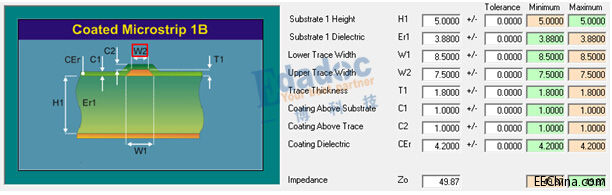

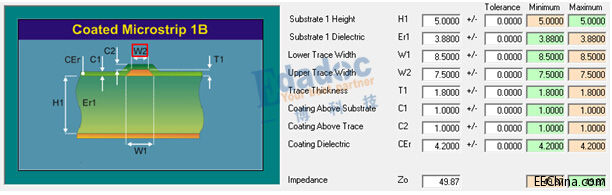

a、微带线

微带线的特点就是只有一个参考层,上面盖绿油。下面是单线(50Ω)和差分线(100Ω)的具体参数设置。

图二

注意事项:

1、H1是表层到参考层的介质厚度,不包括参考层的铜厚;

2、C1、C2、 C3是绿油的厚度,一般绿油厚度在0.5mil~1mil左右,所以保持默认就好,其厚度对于阻抗有细微影响,这也是处理文字面是,尽量不让丝印放置在阻抗线上的原因。

3、T1的厚度一般为表层铜厚加电镀的厚度,1.8mil为0.5OZ+Plating的结果。

4、一般W1是板上走线的宽度,由于加工后的线为梯形,所以W2<W1.一般当铜厚为1mil以上时W1-W2=1mil,当铜厚为0.5mil时W1-W2=0.5mil。

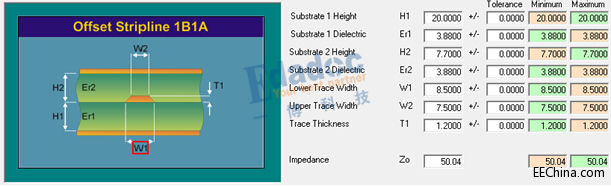

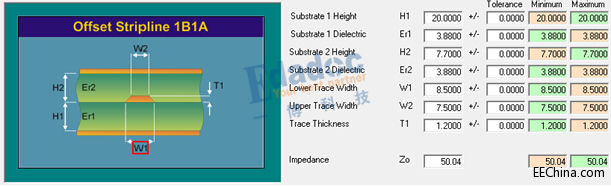

b、带状线

带状线是位于两个参考平面之间的导线。下面是单线(50Ω)和差分线(100Ω)的具体参数设置。

图三

注意事项:

1、H1是导线到参考层之间CORE的厚度,H2是导线到参考层之间PP的厚度(考虑pp流胶情况);如图一所示层叠,若阻抗线在ART03层,那么H1就是GND02到ART03之间的介质厚度,而H2则是GND04到ART03之间的介质厚度再加上铜厚。

2、Er1和Er2之间的介质不同时,可以填各自对应的介电常数。

3、T1的厚度一般为内层铜厚;当单板为HDI板是,需要注意内层是否有电镀。

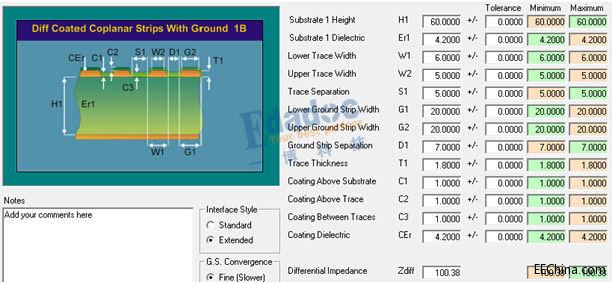

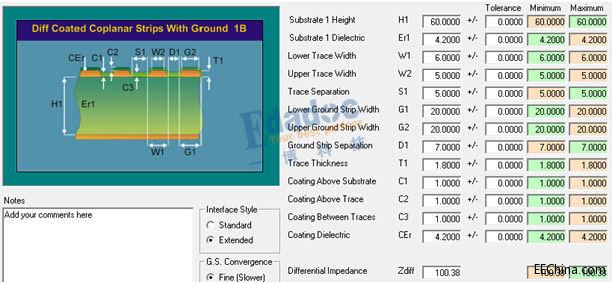

上述是常见的阻抗线的计算,然而有部分单板由于板子较厚,层数较少,利用上面的方法没有办法计算出阻抗线的具体参数,这时候就要考虑共面阻抗了,如下图所示:

注意事项:

1、H1是导线到最近参考层之间介质的厚度。

2、G1和G2是伴随地的宽度,一般是越大越好。

3、D1是到伴随地之间的间距。

问题:了解基本的阻抗计算后,对于单板上的信号线而言,他们的阻抗和什么因素有关,各自是什么关系(正比还是反比)?

上次讲到了阻抗计算和工艺制程之间的一些"权衡的艺术",主要是为了达到我们阻抗管控目的的同时,也能保证工艺加工的方便,以及尽量降低加工成本。接下来,就具体说说,利用SI9000计算阻抗的具体过程。

如何计算阻抗

对于阻抗计算而言,层叠设置是先决条件,首先必选先设置好单板的具体层叠信息,下面是一个常见八层板的层叠信息,以这个为例子,看看阻抗计算的一些注意事项。

图一

对于信号线而言,在板子上实现的形式又分为微带线和带状线,两者的不同,使得阻抗计算选择的结构不一致,下面分别讨论这两种常见的阻抗计算的情况。

a、微带线

微带线的特点就是只有一个参考层,上面盖绿油。下面是单线(50Ω)和差分线(100Ω)的具体参数设置。

图二

注意事项:

1、H1是表层到参考层的介质厚度,不包括参考层的铜厚;

2、C1、C2、 C3是绿油的厚度,一般绿油厚度在0.5mil~1mil左右,所以保持默认就好,其厚度对于阻抗有细微影响,这也是处理文字面是,尽量不让丝印放置在阻抗线上的原因。

3、T1的厚度一般为表层铜厚加电镀的厚度,1.8mil为0.5OZ+Plating的结果。

4、一般W1是板上走线的宽度,由于加工后的线为梯形,所以W2<W1.一般当铜厚为1mil以上时W1-W2=1mil,当铜厚为0.5mil时W1-W2=0.5mil。

b、带状线

带状线是位于两个参考平面之间的导线。下面是单线(50Ω)和差分线(100Ω)的具体参数设置。

图三

注意事项:

1、H1是导线到参考层之间CORE的厚度,H2是导线到参考层之间PP的厚度(考虑pp流胶情况);如图一所示层叠,若阻抗线在ART03层,那么H1就是GND02到ART03之间的介质厚度,而H2则是GND04到ART03之间的介质厚度再加上铜厚。

2、Er1和Er2之间的介质不同时,可以填各自对应的介电常数。

3、T1的厚度一般为内层铜厚;当单板为HDI板是,需要注意内层是否有电镀。

上述是常见的阻抗线的计算,然而有部分单板由于板子较厚,层数较少,利用上面的方法没有办法计算出阻抗线的具体参数,这时候就要考虑共面阻抗了,如下图所示:

注意事项:

1、H1是导线到最近参考层之间介质的厚度。

2、G1和G2是伴随地的宽度,一般是越大越好。

3、D1是到伴随地之间的间距。

问题:了解基本的阻抗计算后,对于单板上的信号线而言,他们的阻抗和什么因素有关,各自是什么关系(正比还是反比)?

- Cadence发布EDA业界第一款具备端到端并行处理流程的Encounter数字实现系统(11-04)

- 高分辨率ADC的板布线(11-01)

- 基于FPGA的空间电场信号采集系统设计(11-28)

- Cadence 推出创新的FPGA-PCB协同设计解决方案(04-25)

- 高速PCB布线实践指南(11-01)

- 点评:全方位剖析中国集成电路核心技术发展之困(01-08)