一张图看懂阻抗偏差这件事

时间:03-01

来源:互联网

点击:

--为什么常规阻抗控制建议是10%后记

作者:吴均一博科技高速先生团队队员

过了正月十五,高速先生继续开张,恭祝新老朋友们新年快乐,猴年猴赛雷!

有朋友说:高速先生为了研究问题,还真是认(chui)真(mao)细(qiu)致(ci)哈。一个常规阻抗为什么是控制10%偏差,也能写的这么详(luo)细(shuo)。

有时候,高速先生也是有苦难言哈,自打阻抗话题开始群殴,就有公司市场人员拜托上门:你们写写阻抗控制10%这个事情吧,老是有客户要求我们做5%,昨天还有人要求控制到2.5%……

1、 正态分布的智慧

我们的工艺专家东哥临危受命,施展浑身解数连续写了好几篇,其中第二篇还是凌晨1:47发出来的,第三篇号称是打着吊瓶写的,大家记得在后台回复一下,一起来给东哥点个赞哈。

认真拜读了东哥的文章,总结起来就是:设计容易,生产不易,且生(产)且珍惜!

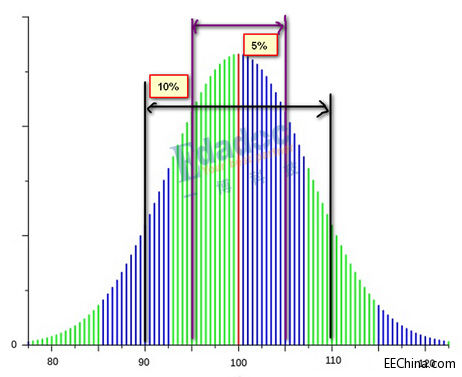

生产是物理加工制程,不管生产如何管控,总归最后要满足正态分布原则。我们看看这张图:(高速先生团队的平面设计休婚假回家了,所以图片有点丑,多包涵)

100欧姆的差分阻抗要求,如果按照90~110欧姆范围来管控(上图黑色区域),大部分板子能满足需求,也就是说良品率不错。如果要求95~105欧姆(上图紫色区域),能够满足要求的板子就少了,大部分板子就只能报废。如果要求97.5~102.5欧姆,我只能说,你的产品太土豪了。

如果按照80~120欧姆范围来管控,不是更多板子可以通过吗?那样的话,可能你的信号就通不过了!阻抗对信号的影响,我们在后续文章会一一展开。

正态分布的智慧,也就是权衡妥协的智慧,可接受的信号质量,可接受的良品率。

2、更精确的阻抗控制要求怎么办?

大部分数字信号为什么不需要更高精度的阻抗控制要求,大家可以看看之前袁波发的文章,阻抗偏差到60~65欧姆有什么危害?

有些特殊的领域,需要更高的阻抗控制要求,比如传说中的微波射频信号,也比如高速先生一直在做的TRL测试板,我们该怎么办?

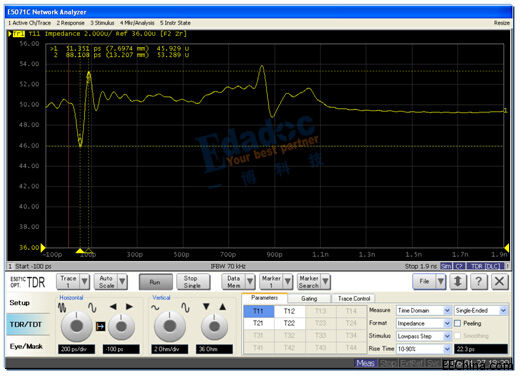

先来显摆显摆我们的测试板,实际阻抗测试的数据:

篇幅关系,不能贴太多图,实际上TRL测试板的设计功力之一就是阻抗优化与控制,包括了SMA接触区域的阻抗优化,及测试校准件的最终阻抗控制。

我们一直很自豪的就是,我们做的好几版TRL测试板,最终的阻抗线控制都在5%以内甚至更小。我们的做法是把阻抗控制的风险自己来把控,详细指定了层叠参数,不允许生产环节进行调整。这就要求设计人员非常了解生产加工及材料可能的问题,并提前规避。

要做到这一点,就要求设计工程师非常了解生产。东哥辛辛苦苦写的三篇文章,浏览量并不大,我还是很痛心。设计人员总是会轻视生产加工环节,这是要吃苦头的。所以这里再帮东哥推荐下之前的三篇生产加工的文章。

经过这几期的文章,大家知道了板厂常规只接受10%的阻抗误差管控要求,如果要求5%,必然会导致良品率降低,成本上升。那么问题来了:如果大家今天也变身高速先生,来做TRL测试板,要求板厂严格按照层叠要求及设计线宽间距来生产,最终阻抗的风险你自己来承担,你会在设计中注意哪些细节?如何提供层叠要求?

作者:吴均一博科技高速先生团队队员

过了正月十五,高速先生继续开张,恭祝新老朋友们新年快乐,猴年猴赛雷!

有朋友说:高速先生为了研究问题,还真是认(chui)真(mao)细(qiu)致(ci)哈。一个常规阻抗为什么是控制10%偏差,也能写的这么详(luo)细(shuo)。

有时候,高速先生也是有苦难言哈,自打阻抗话题开始群殴,就有公司市场人员拜托上门:你们写写阻抗控制10%这个事情吧,老是有客户要求我们做5%,昨天还有人要求控制到2.5%……

1、 正态分布的智慧

我们的工艺专家东哥临危受命,施展浑身解数连续写了好几篇,其中第二篇还是凌晨1:47发出来的,第三篇号称是打着吊瓶写的,大家记得在后台回复一下,一起来给东哥点个赞哈。

认真拜读了东哥的文章,总结起来就是:设计容易,生产不易,且生(产)且珍惜!

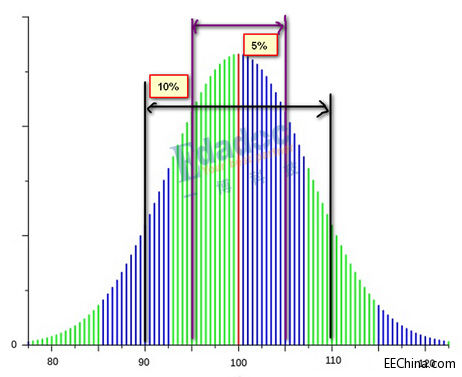

生产是物理加工制程,不管生产如何管控,总归最后要满足正态分布原则。我们看看这张图:(高速先生团队的平面设计休婚假回家了,所以图片有点丑,多包涵)

100欧姆的差分阻抗要求,如果按照90~110欧姆范围来管控(上图黑色区域),大部分板子能满足需求,也就是说良品率不错。如果要求95~105欧姆(上图紫色区域),能够满足要求的板子就少了,大部分板子就只能报废。如果要求97.5~102.5欧姆,我只能说,你的产品太土豪了。

如果按照80~120欧姆范围来管控,不是更多板子可以通过吗?那样的话,可能你的信号就通不过了!阻抗对信号的影响,我们在后续文章会一一展开。

正态分布的智慧,也就是权衡妥协的智慧,可接受的信号质量,可接受的良品率。

2、更精确的阻抗控制要求怎么办?

大部分数字信号为什么不需要更高精度的阻抗控制要求,大家可以看看之前袁波发的文章,阻抗偏差到60~65欧姆有什么危害?

有些特殊的领域,需要更高的阻抗控制要求,比如传说中的微波射频信号,也比如高速先生一直在做的TRL测试板,我们该怎么办?

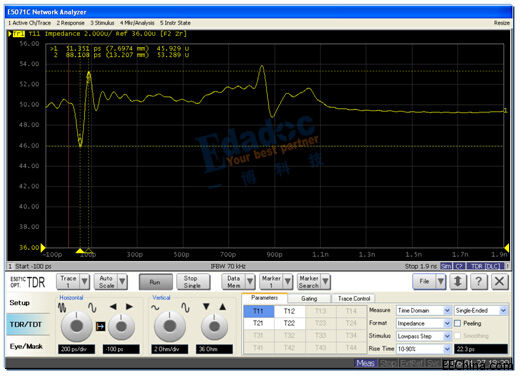

先来显摆显摆我们的测试板,实际阻抗测试的数据:

篇幅关系,不能贴太多图,实际上TRL测试板的设计功力之一就是阻抗优化与控制,包括了SMA接触区域的阻抗优化,及测试校准件的最终阻抗控制。

我们一直很自豪的就是,我们做的好几版TRL测试板,最终的阻抗线控制都在5%以内甚至更小。我们的做法是把阻抗控制的风险自己来把控,详细指定了层叠参数,不允许生产环节进行调整。这就要求设计人员非常了解生产加工及材料可能的问题,并提前规避。

要做到这一点,就要求设计工程师非常了解生产。东哥辛辛苦苦写的三篇文章,浏览量并不大,我还是很痛心。设计人员总是会轻视生产加工环节,这是要吃苦头的。所以这里再帮东哥推荐下之前的三篇生产加工的文章。

经过这几期的文章,大家知道了板厂常规只接受10%的阻抗误差管控要求,如果要求5%,必然会导致良品率降低,成本上升。那么问题来了:如果大家今天也变身高速先生,来做TRL测试板,要求板厂严格按照层叠要求及设计线宽间距来生产,最终阻抗的风险你自己来承担,你会在设计中注意哪些细节?如何提供层叠要求?

射频 相关文章:

- 如何设计射频电路及其PCB Layout(06-15)

- PCB设计中射频接口和射频电路的特性(06-26)

- 射频开关模块功能电路PCB板的设计(10-25)

- 射频/微波PCB的信号注入"法门"(02-12)

- 射频集成电路设计中常见问题与方案解析(03-09)

- PCB电路设计中磁珠的选用(09-05)