美国普度大学研发出SOI CMOS功率放大器,可用于5G、下一代雷达和微型卫星

在美国国防先期研究计划局(DARPA)的部分资金支持下,美国普度大学研究出采用绝缘体上硅(SOI)互补金属氧化物半导体(CMOS)工艺、基于三层共源共栅(triple Cascode)组合晶体管版图的高效率功率放大器,适用于下一代移动电话、车用低成本防撞雷达和通信用轻量微型卫星。

现有移动电话中传输信号用功率放大器主要采用砷化镓(GaAs),由于不能与其他硅基CMOS信号处理器件集成,限制了移动电话集成度的进一步提升。新的放大器基于CMOS设计,可提高集成度、寿命和性能,减少制造和测试成本,并降低功耗。

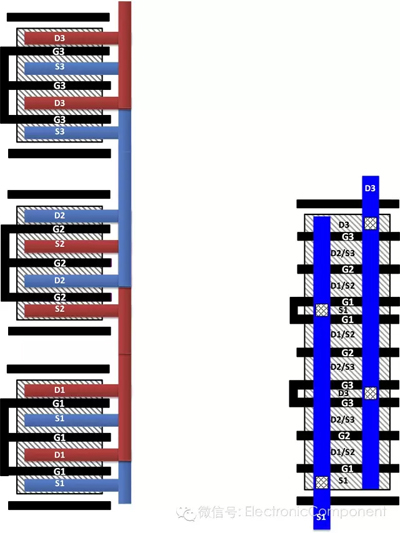

普度大学在新设计的SOI CMOS放大器中,对部分硅晶体管进行了堆叠合并,减少了晶体管间通常所需的金属互联数量,从而减少了寄生电容和获取更高工作频率。

第五代移动电话(预计在2019年)需要能够工作在更高频率和效率的功率放大器,提供比现有手机更快的数据传输和视频下载速度,并消耗更少的功耗,以更好地满足新兴物联网需求。值得一提的是,新研制的CMOS放大器还将有力推动微型卫星的发展,将微型卫星的重量降为现有技术的百分之一。

研究人员目前正在研究新一版功率放大器,功率性能将再提升一倍。下一步的工作是将该放大器与手机其他器件实现单片集成。研究人员为该研究结果发表了两篇论文,并正申请三项专利。

左图是移动手机中功率放大器的标准版图,右边是普度大学的新设计

技术细节

堆叠的三级共源共栅结构作为功率放大器的基本单元,能够容易地获取高增益、高功率、高效率和缩小版图面积。研究人员用格罗方德45nm CMOS SOI工艺制造出两个毫米波功堆叠率放大器。

第一个功率放大器工作在K波段(24-28GHz),带有三个三级共源共栅单元,每个单元都使用标准带有独立版图的晶体管。在24GHz、偏置电压10.8V时,最大线性功率增益是13dB,饱和输出电压是25.3dBm,-1dB输出功率(P1dB)是23.8dBm,峰值功率附加效率(PAE)是20%。

第二个功率放大器工作在U波段(40-60GHz),带有两个三级共源共栅单元,每个单元采用了组合型版图,有效减少内部寄生电容,带来PAE性能的显著提升。在46GHz、偏置电压6V下,饱和输出功率(PSAT)达到22.4dBm,线性增益17.4dB,峰值PAE42%,漏极效率(DE)49%。在46GHz、偏置电压4.8V下,PSAT减小至20dBm,DE和峰值PAE分别增加至53%和45%。

来源:大国重器——聚焦世界军用电子元器件

- 飞利浦发布针对不断融合微波应用的硅基BiCMOS技术(11-13)

- 可覆盖100m的车载雷达用CMOS收发器亮相(02-23)

- 三星推出网络摄影机专用CMOS影像感测器(04-13)

- NDK推出CMOS时钟振荡器M55310/30(05-18)

- 恩智浦将推出采用SiGe工艺技术的微波射频产品(05-20)

- 凌力尔特推出采用SiGe BiCMOS 技术的低噪声和低失真的差分放大器(10-13)