5G流行词Massive MIMO背后的信号处理

见而忽略的功率。

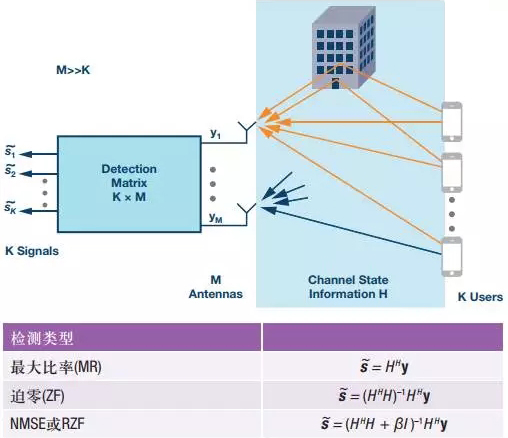

图8. 上行链路信号处理H表示共轭转置

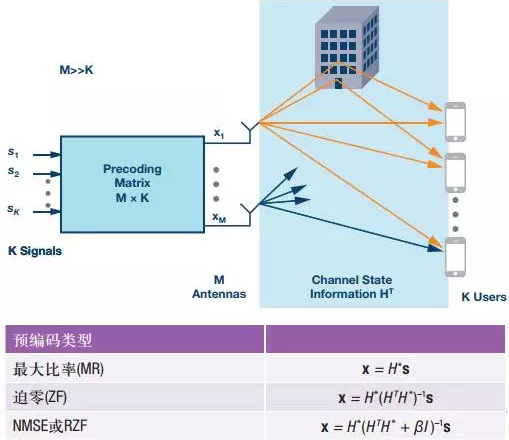

图9. 下行链路信号处理T表示转置。* 表示共轭

顾名思义,最大比率滤波旨在最大程度提高信噪比(SNR)。从信号处理角度看,这是最简单的方法,因为检测/预编码矩阵刚好是CSI矩阵H的共轭转置或转置。其最大缺点是忽略了用户间干扰。

迫零预编码试图解决用户间干扰问题,通过设计优化标准来使其最小。检测/预编码矩阵是CSI矩阵的伪逆。伪逆的计算开销高于MR情况中的复共轭。然而,由于太注重降低干扰,用户的接收功率会受影响。

MMSE试图在放大信号与降低干扰之间取得平衡。这种整体观需付出的代价是信号处理复杂度较高。MMSE方法给优化引入了一个正则项—在图8和图9中表示为ß—利用它可以找到噪声协方差与发射功率的平衡点。此方法在文献中有时也被称为正则化迫零(RZF)。

以上并未囊括所有预编码/检测技术,只是简单介绍了主要线性方法。另外还有非线性信号处理技术,例如脏纸编码和连续干扰消除便可用来解决此问题。这些方法可提供最优容量,但实现起来非常复杂。上述线性方法对massive MIMO而言一般是足够的,天线数目可以很大。预编码/检测技术的选择取决于计算资源、天线数目、用户数目和系统所处环境的多样性。对于天线数目远大于用户数目的大天线阵列,最大比率方法可能足以满足需要。

现实系统向Massive MIMO

提出的实际挑战

在现实场景中实现massive MIMO时,还有其他实际问题需要考虑。举个例子,假设一个天线阵列有32个发射(Tx)信道和32个接收(Rx)信道,工作在3.5 GHz频段。那么需要放置64个RF信号链,在给定工作频率下,天线间距约为4.2 cm。这说明,有大量硬件需装入一个很小的空间中。它还意味着会耗散大量功率,不可避免会带来温度问题。ADI的集成收发器为此类问题提供了高效解决方案。

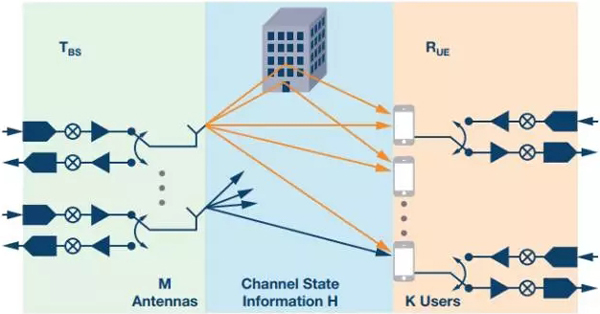

上文讨论了利用系统的互易性来大幅削减信道估计和信号处理开销。图10显示了一个实际系统中的下行链路信道。它分为三个部分:空中信道(H)、基站发射RF路径的硬件响应(TBS)和用户接收RF路径的硬件响应(RUE)。上行链路与此相反,RBS表征基站接收硬件RF路径,TUE表征用户发射硬件RF路径。互易性假设虽然对空中接口成立,但对硬件路径不成立。由于迹线不匹配、RF路径间同步不佳和温度相关的相位漂移,RF信号链会给系统带来误差。

图10. 实际下行链路信道

对RF路径中的所有LO(本振)PLL使用同一同步参考时钟,并对基带数字JESD204B信号使用同步SYSREF,有助于解决RF路径间的延迟问题。但在系统启动时,RF路径之间仍会有通道间的相位失配,由温度引起的相位漂移会进一步扩大此问题。因此很显然,系统在启动时需要初始化校准,此后运行中需要周期性校准。通过校准可实现互易性优势,使信号处理复杂度维持在基站,并且只需要表征上行链路信道。这样可获得一般意义上的简化,从而仅需要考虑基站RF路径(TBS和RBS)。

有多种方法可校准这些系统——

· 在天线阵列前面放置一个校准天线,利用此校准天线来校准接收和发射RF信道。以这种在阵列前方放置一根天线的方式是否满足实际系统校准的需求,是有疑问的。

· 利用阵列中现有天线之间的互藕作为校准机制,这有很高的可行性。

· 在基站中的天线之前增加一些无源耦合路径(或许是最简单直接的方法)。这会增加硬件复杂性,但应能提供一个鲁棒的校准机制。

为了全面校准系统,从一个指定校准发射信道发送一个信号,所有RF接收路径通过无源耦合连接接收该信号。然后,每个发射RF路径依次发送一个信号,该信号在各天线的耦合点被接收,被传回到一个合路器,再被送至指定校准接收路径。温度相关效应的变化一般很慢,故与信道特性不同,无需频繁执行温度相关校准。

ADI的收发器和Massive MIMO

ADI的集成收发器产品系列特别适合需要高密度RF信号链的应用。AD9371具有2个发射路径、2个接收路径和一个观测接收机,并有3个小数N分频PLL用于RF LO生成,采用12 mm ×12 mm封装。这一无与伦比的集成度使得制造商能够及时且经济高效地创建复杂系统。

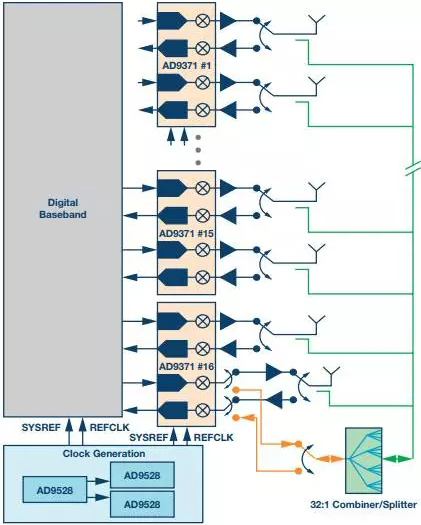

图11显示了一个使用多个AD9371收发器的可能系统实现。该系统有32个发射信道和32个接收信道,采用16个AD9371收发器。三个AD9528时钟发生器为系统提供PLL参考时钟和JESD204BSYSREF。

图11. 采用AD9371收发器的32 Tx、32 Rx massive MIMO射频头框图

AD9528是一款双级PLL,提供14路LVDS/HSTL输出,集成JESD204B SYSREF发生器,可用于多器件同步。AD9528排列成扇出缓冲配置,其中一个用作主器件,它的一些输出用于驱动时

- ADI公司为下一代蜂窝与宽带无线应用提供直接变频接收机解决方案(08-17)

- ADI ADRF6655 100-2500 MHz有源混频方案(08-30)

- ADI ADL5354高性能RF混频方案(09-07)

- Anadigics AWT6241 TD-SCDMA手机线性功率放大方案(07-26)

- ADI ADF4150HV 4.4 GHz频率合成方案(09-07)

- 射频收发器为航空航天和防务应用提供突破性的SWaP解决方案(10-23)