DDR3内存的PCB仿真与设计

3.3时序分析

DDR3是并行总线,其时序属源同步系统,在满足信号质量的前提下,也必须满足时序要求。对于源同步时钟,驱动芯片的数据和时钟信号由内部电路提供即数据和时钟并行传输。DDR3对不同的时序关系采用分组设计,其时序关系如表2.

表2时序分组关系

源同步时序计算公式:

Tsetup_margin=Tvb-Tsetup-Tskew

Thold_margin=Tva-Thold-Tskew

公式中:Tsetup margin\Thold_margin:建立时间余量\保持时间余量,Tvb\Tva:驱动端的建立时间和保持时间,Tsetup\Thold接收端的建立时间和保持时间,Tskew:指数据、地址信号参考时钟引起的偏移。其中Tvb\Tva,Tsetup\Th01d参数值都是能从器件手册中获取,关键是数据与选通信号飞行时间的时序偏移(skew),包含驱动端输出的偏移和在PCB板上的走线长度的偏移,需通过时序仿真非理想随机码进行分析计算得出。

以DDR3数据读写操作为例,根据下表芯片资料中的时序参数进行静态时序裕量的计算,获得PCB设计的时序控制规则。

表3仿真所需要的时序参数(数据率:1333MHz)控制器:

写操作:

Tsetup_margin=0.25-0.03=0.22ns

Thold_margin=0.25-0.065=0.185ns

读操作:

Tsetup_margin = Thold_margin=(0.38*1.5-0.125)/2 - 0.125=97.5ps

上述计算值是理论上的时序余量,其实源同步时序除本身芯片自身固有特性所带来的延时外还受其他因素的影响,都属于偏移范围,主要包括:

(1)高速总线造成的信号完整性问题如串扰、同步开关噪声、码间干扰(ISI)等影响,需通过信号仿真分析来估算。

(2)高速总线互连所产生的时序偏斜:主要是信号总线互连链路中的布线误差,整个链路含器件封装内部走线、pcb板上走线和走线过孔等产生的时序偏差,可通过等长布线来控制其时序偏斜。

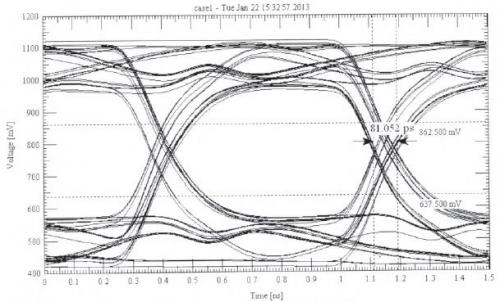

对8位数据总线DQ进行分析,选取一根数据线为受害线,其余数据线为反向伪随机码,条件设为最快驱动,在此最坏情况进行综合仿真,查看其受扰线的波形情况。

比较图5、图6后可看出此数据线受到各方面的因素综合影响,使波形眼图中的眼高和眼宽都相应减小,导致数据总线时序裕量大大减少。上述时序裕量需减去此值再考虑其他噪声因素,结合经验留些时序余量后,就可把时序余量转换成PCB设计时的布线长度约束(约6in/ns)。

图5 DO数据总线理想波形

图6 DQ数据总线最坏情况下的实际波形

4 PCB设计

4.1设计规则约束

(1)等长约束

采用分组等长方式,分组如下:

数据线与DQS、DM信号组:64位数据线按8位一组,每组分别对应其各自的DQS和DM信号;由于数据时序余量最小,组内严格控制延时,以对应的DQS为基准,等长精度在±10mil.

地址线、控制线、时钟线组:需等长控制,地址线与控制线各分支的误差±20mil,它们与时钟线误差在±100mil,差分时钟线之间±5rail.

(2)间距约束

DDR3同组线间的间距保持在2倍线宽;不同组类线的间距保持在3倍线宽;DDR3线与其他jBDDR3线之间的间距应大于50mil,用于串扰控制。

(3)线宽约束

根据传输线阻抗要求和印制板叠层结构计算走线线宽,设置走线线宽规则,保证阻抗的一致性。

4.2布线技巧

同组内总线尽量同层走线,时钟线与地层相邻;尽量少用过孔,如用需组内过孔数相同,保证其一致性;相邻信号走线需交叉,避免长距离的重叠走线,如相邻层间距足够大,可适当降低要求;

走线避免采用直角应用45.斜线或圆弧角走线;尽量采用3W原则走线;

与电源层相邻的信号层中的高速走线应避免跨电源\地平面;

电源层比地层内缩20H(H:电源层与地层的介质厚度);不允许有孤立铜的存在。

5 PCB板后仿验证

DDR3的PCB设计结束后进行后仿分析,用以对前面的仿真分析进行验证。PCB板后仿主要是对DDR3信号质量和时序关系进行分析。

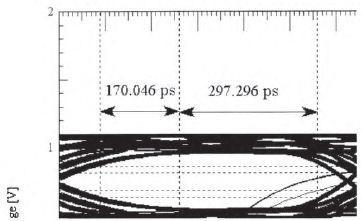

5.1 DDR3的差分时钟验证

DDR3差分时钟在PCB布线后对其后仿真分析,抽取一对实际时钟走线对所走链路进行分析其波形如下图7:其单调性和上下过冲都满足要求。

图7:差分时钟PCB走线波形图8数据总线写时序

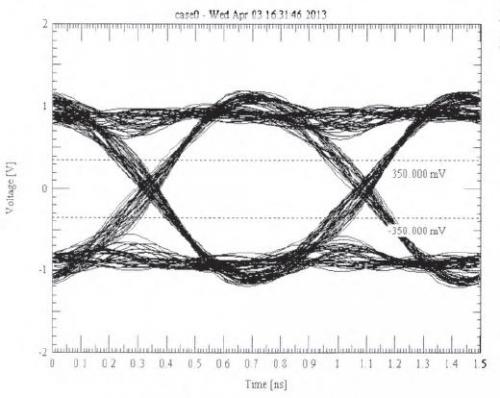

5.2 DDR3的时序验证

对于布线后的时序验证也是十分重要的环节。在确定好同步信号组及对应的选通信号后利用Cadence软件的BUS setup功能进行综合分析,位数据总线及相应的DQS信号,设定时钟频率666MHz,设定相应ibis模型,加入随机码流,最终进行分析后可通过测量得到时序参数可计算时序裕量,验证PCB布线是否满足相关的时序关系。分析结果见图8.

图8数据总线写时序

从上图8可测量出数据总线的建立时间和保持时间,根据DDR3数据相应时序进行静态时序计算,再综合考虑其余因素对时序的影响来估算包括其PCB走线长度引起的偏移等,满足其DDR3接收端的建立时间和保持时间的时序正确性,其它时序关系类似可通过此验证。