半导体C-V测量基础

与相角

R+jX:电阻与电抗

Cp-Gp:并联电容与电导

Cs-Rs:串联电容与电阻

其中:Z=阻抗

D=耗散因子

θ=相角

R=电阻

X=电抗

G=电导

图4. C-V测量得到的主要电气变量

成功C-V测量的挑战

C-V测试配置的框图虽然看上去非常简单,但是这种测试却具有一定的挑战。一般而言,测试人员在下面几个方面会遇到麻烦:

低电容测量(皮法和更小的值)

C-V测试仪器与圆片器件的连接

漏电容(高D)的测量

利用硬件和软件采集数据

参数提取

克服这些挑战需要仔细注意所用的技术以及合适的硬件和软件。

低电容测量。 如果C较小,那么DUT的交流响应电流就较低,难以测量。但是,在较高的频率下,DUT阻抗将减小,从而电流会增大,比较容易测量。半导体电容通常非常低(低于1pF),低于很多LCR表的测量范围。即使那些声称能够测量这些小电容值的测试仪可能也会由于说明书晦涩难懂而很难判断最终的测量精度。如果无法明确给出测试仪整个量程的精度,那么用户需要因此而咨询制造商。

高D(漏)电容。半导体电容除了C值较低之外,还具有泄漏的特点。当与电容并联的等价电阻太低时就会出现这种情况。这会导致电阻性阻抗超过电容性阻抗,C值被噪声所淹没。对于具有超薄栅氧层的器件,D的值可能大于5。一般而言,随着D的增大,电容测量的精度迅速下降,因此高D是实际使用电容计的一个限制因素。同样,较高的频率有助于解决这一问题。在较高的频率下,电容性阻抗较低,使得电容电流较高,更容易进行测量。

C-V测量的互连。大多数测试环境下,DUT都是圆片上的一个测试结构:它通过探测器、探针卡适配器和开关矩阵连接C-V测试仪。即使没有开关,仍然也会使用探测器和大量的连线。在较高的频率下,必须采用特殊的校正和补偿技术。通常情况下,这是通过组合使用开路、短路或者校准器件来实现的。由于硬件、布线和补偿技术非常复杂,因此经常与C-V测试应用工程师进行交流是一个好的办法。他们擅长使用各种探测系统,克服各种互连问题。

获取有用的数据。除了上述的精度问题,C-V数据采集中实际需要考虑的因素包括测试变量的仪器量程,参数提取软件的多功能性和硬件的易用性。一般而言,C-V测试已仅限于约30V和10mA直流偏压。但是,很多应用,例如LD MOS结构的特征分析、低k夹层电介质、MEMS器件、有机TFT显示器和光电二极管,需要在较高的电压或电流下进行测试。对于这些应用,需要单独的高压直流电源和电容计;高达400V的差分直流偏压(0到±400V)和高达300mA的电流输出是非常有用的。在C-V测试仪的HI和LO端加载差分直流偏压能够更灵活地控制DUT内的电场,这对于新型器件的研究和建模是非常有用的,例如纳米级元件。

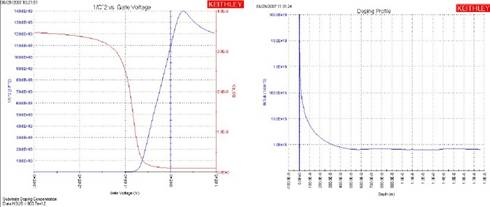

仪用软件应该包括无需用户编程可直接使用的测试例程。这些应该适用于大多数广泛使用的器件工艺和测试技术,即本文前三段中提及的有关内容。有些研究者可能会对一些不常见的测试感兴趣,例如对MIM(金属-绝缘体-金属)型电容进行C-V和C-f扫描,测量圆片上的互连小电容,或者对双端纳米器件进行C-V扫描。利用自动绘图功能能够方便的实现参数提取(例如,如图5所示)。

图5. 利用吉时利4200-SCS进行参数提取的实例表现了半导体的掺杂特征(左边的蓝线),它与1/C2 与Vg的关系呈倒数关系(红线)。右图给出了掺杂分布,即每立方厘米的载流子数与衬底深度的函数关系。

通常,人们都希望工程技术人员和研究人员在几乎没有任何仪器使用经验或培训的情况下就能够进行C-V测量。具有直观用户界面和简单易用特征的测试系统使得这一点成为现实。其中包括简单的测试配置、序列控制和数据分析。否则,用户在掌握系统方面就要比采集和使用数据花费更多的时间。对测试系统其它考虑因素包括:

紧密集成的源-测量单元、数字示波器和C-V表

方便集成其他外部仪器

基于探针的高分辨率和高精度测量(直流偏压低至毫伏级,电容测量低至飞法级)

测试配置和库易于修改

提供检测/故障诊断工具帮助用户确定系统是否正常工作

作者简介

Lee Stauffer是位于美国俄亥俄州克里夫兰市的吉时利仪器公司的高级市场经理,负责面向半导体制造和研究市场的研发和支持产品。他接受过电子工程和半导体器件物理专业的正规教育,在半导体工艺和产品工程、器件特征分析和仪器设计领域具有20年的丰富经验。他的联系电话为440-248-0400,电子邮箱为lstauffer@keithley.com。