双目立体视觉摄像头模块开发搭建,含源代码、电路图

,用来与CLK协调完成D_I(7:0)到D_O(15:0)的转化,起到像素前后部分的标志位作用);

FV_I:帧有效信号(Frame Valid),也称场同步信号,来自摄像头模块,输出一帧图像期间,电平为高,帧与帧之间时,电平拉低;(参见MT9D112_DS Page28 Figure18)

LV_I:行有效信号(Line Valid),也称行同步信号,来自摄像头模块,输出图像的一行期间,电平为高,行与行之间时,电平拉低;(参见MT9D112_DS Page28 Figure18)

PCLK_I:信号来自CAM_PCLK_I经过I/O缓冲器(IOBUF)后的输出,逻辑上等价于CAM_PCLK_I;

RST_I:模块复位信号,来自SysCon模块的ASYNC_RST端口。

Output:

D_O(15:0):16-bit数据输出信号(RGB565),由两个8-bit的输入数据组装得到,代表一个像素的颜色值等,输出给FBCtl图像缓存控制模块的DIA(15:0);

DV_O:输出给FBCtl图像缓存控制模块的ENA,作为使能信号,每当一个像素的16位数值配齐时置1;

MCLK_O:输出给摄像头,作为其外部时钟信号XCLK的输入(6-54MHz);

PCLK_O:输出给FBCtl图像缓存控制模块的CLKA,来自于PCLK_I的缓冲,作为图像存储时的像素同步时钟;

PWDN_O:恒定为0,直接输出给摄像头的,起到power_up功能;

RST_O:输出给摄像头,用作摄像头复位(低有效);

VDDEN_O:与Inst_camctlB的相同端口求与后输出到摄像头的VDDEN管脚,应该是连到摄像头,作为工作接通通电源的使能信号;

SCL:输出到摄像头的SCLK端口(FPGA→Camera),作为串行接口的时钟输入;

SDA:输出到摄像头的SDATA端口(FPGA↔Camera),作为串行接口的信号传输。

(3)图像缓存控制模块

Input:

ENC:来自VideoTimingCtl模块的VDE_O端口,读写控制();

RSTC_I:来自SysCon模块的ASYNC_RST端口;

CLKC:来自SysCon模块的PCLK_O端口;

//////////////////////////////////////////////////////////////////////////////

ENB:来自CamCtlB模块的DV_O端口,读写控制(1写);

RSTB_I:来自Inst_InputSync_FVB模块的D_O端口取反与SysCon模块的ASYNC_RST端口求或;

CLKB:来自CamCtlB模块的PCLK_O端口;

/////////////////////////////////////////////////////////////////////////////

ENA:来自CamCtlA模块的DV_O端口,读写控制(1写);

RSTA_I:来自Inst_InputSync_FVA模块的D_O端口取反与SysCon模块的ASYNC_RST端口求或;

CLKA:来自CamCtlA模块的PCLK_O端口;

/////////////////////////////////////////////////////////////////////////////

ddr2clk_2x:来自SysCon模块的DDR2CLK_2X_O端口;

ddr2clk_2x_180:来自SysCon模块的DDR2CLK_2X_180_O端口;

pll_ce_0:来自SysCon模块的PLL_CE_0_O端口;

pll_ce_90:来自SysCon模块的PLL_CE_90_O端口;

pll_lock:来自SysCon模块的PLL_LOCK端口;

async_rst:来自SysCon模块的ASYNC_RST端口;

mcb_drp_clk:来自SysCon模块的MCB_DRP_CLK_O端口;

RD_MODE(1:0):来自SysCon模块的MSEL_O(1:0)端口;

DIB(15:0):来自Inst_camctlB模块的D_O(15:0)端口;

DIA(15:0):来自Inst_camctlA模块的D_O(15:0)端口;

Output:

RDY_O:该信号取反后与SysCon模块的ASYNC_RST信号求或后输给VideoTimingCtl模块的RST_I端口;

mcb3_dram_ras_n:输出给DDR2;

mcb3_dram_cas_n:输出给DDR2;

mcb3_dram_we_n:输出给DDR2;

mcb3_dram_odt:输出给DDR2;

mcb3_dram_cke:输出给DDR2;

mcb3_dram_dm:输出给DDR2;

mcb3_dram_udm:输出给DDR2;

mcb3_dram_ck:输出给DDR2;

mcb3_dram_ck_n:输出给DDR2;

DOC(15:0):输出给DVITransmitter模块的BLUE_I/GREEN_I/RED_I,以RGB565的方式自高位向低位排列;

mcb3_dram_a(12:0):输出给DDR2;

mcb3_dram_ba(2:0):输出给DDR2;

mcb3_dram_udqs:双向端口,连接到DDR2;

mcb3_dram_udqs_n:双向端口,连接到DDR2;

mcb3_rzq:双向端口,连接到DDR2;

mcb3_zio:双向端口,连接到DDR2;

mcb3_dram_dqs:双向端口,连接到DDR2;

mcb3_dram_dqs_n:双向端口,连接到DDR2;

mcb3_dram_dq(15:0):双向端口,连接到DDR2;

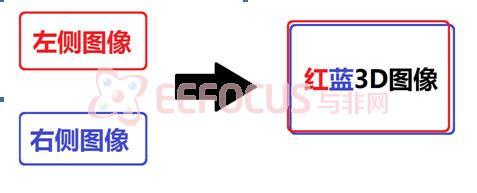

图像处理实现:

第二部分:三维空间定位

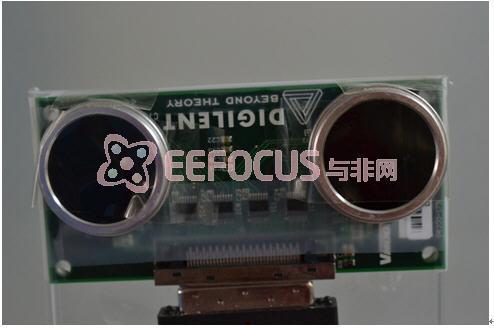

硬件组成: 摄像头模块:在摄像头前加装了两个850nm的红外滤光片,用来滤出红外光点。

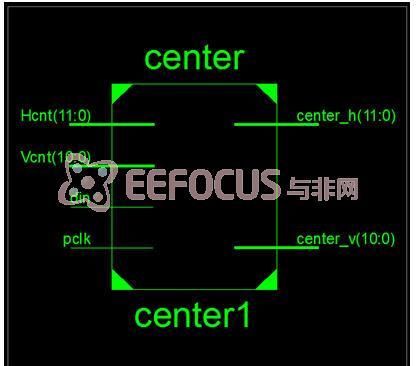

模块源代码:

module center(

input pclk, // pixel clock

input din,

FPGA 双目摄像头 立体视觉 UART数据传输 相关文章:

- 利用FPGA和新技术,使LCD进入HDTV市场(08-27)

- 基于DSP和FPGA的电视观瞄系统设计(09-02)

- FPGA与SRAM相结合完成大容量数据存储(09-03)

- HDTV接收机中Viterbi译码器的FPGA实现(09-09)

- 基于FPGA的液晶显示接口设计 (09-26)

- 解决硬盘驱动器能耗难题(10-13)