用中档FPGA实现高速DDR3存储器控制器

时间:01-24

来源:中电网

点击:

引言

由于系统带宽不断的增加,因此针对更高的速度和性能,设计人员对存储技术进行了优化。下一代双数据速率(DDR)SDRAM芯片是DDR3 SDRAM。 DDR3 SDRAM具有比DDR2更多的优势。这些器件的功耗更低,能以更高的速度工作,有更高的性能(2倍的带宽),并有更大的密度。与DDR2相比,DDR3器件的功耗降低了30%,主要是由于小的芯片尺寸和更低的电源电压(DDR3 1.5V而DDR2 1.8V)。 DDR3器件还提供其他的节约资源模式,如局部刷新。与DDR2相比,DDR3的另一个显著优点是更高的性能/带宽,这是由于有更宽的预取缓冲(与4位的DDR2相比,DDR3为8位宽),以及更高的工作时钟频率。然而,设计至DDR3的接口也变得更具挑战性。在FPGA中实现高速、高效率的DDR3控制器是一项艰巨的任务。直到最近,只有少数高端(昂贵)的FPGA有支持与高速的DDR3存储器可靠接口的块。然而,现在新一代中档的FPGA提供这些块、高速FPGA架构、时钟管理资源和需要实现下一代DDR3控制器的I/O结构。本文探讨设计所遇到的挑战,以及如何用一个特定的FPGA系列LatticeECP3实现DDR3存储器控制器。

DDR3存储器控制器的挑战

针对存储器控制器,DDR3器件面临一系列的挑战。DDR3的工作频率起始于DDR2的更高的工作频率,然后趋于更高的频率。 DDR3接口需要的时钟速度超过400 MHz。这是对FPGA架构的一个重大挑战。针对DDR3存储器控制器的架构,fly-by结构和读写调整变得更加复杂。

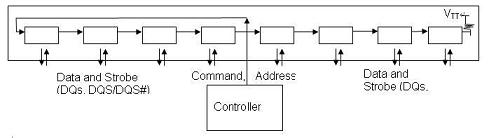

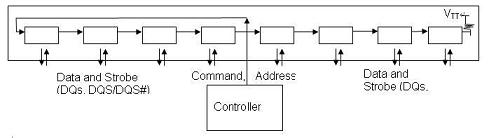

不同于DDR2的T型分支拓扑结构,DDR3采用了fly-by拓扑结构,以更高的速度提供更好的信号完整性。fly-by信号是命令、地址,控制和时钟信号。如图1所示,源于存储器控制器的这些信号以串行的方式连接到每个DRAM器件。通过减少分支的数量和分支的长度改进了信号完整性。然而,这引起了另一个问题,因为每一个存储器元件的延迟是不同的,取决于它处于时序的位置。通过按照DDR3规范的定义,采用读调整和写调整技术来补偿这种延迟的差异。fly-by拓扑结构在电源开启时校正存储器系统。这就要求在DDR3控制器中有额外的信息,允许校准工作在启动时自动完成。

图1 针对DDR3的Fly-by结构

读和写调整

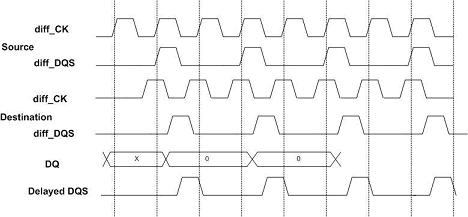

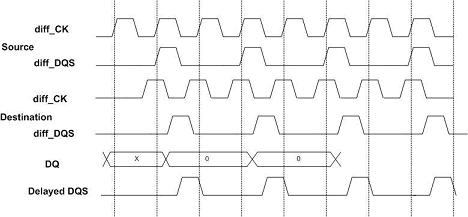

在写调整期间,存储器控制器需要补偿额外的跨越时间偏移(对每个存储器器件,信号延迟是不同的),这是由于fly-by拓扑结构及选通和时钟引入的。如图2所示,源CK和DQS信号到达目的地有延迟。对于存储器模块的每个存储器元件,这种延迟是不同的,必须逐个芯片进行调整,如果芯片有多于一个字节的数据,甚至要根据字节来进行调整。该图说明了一个存储器元件。存储器控制器延迟了DQS,一次一步,直到检测到CK信号从0过渡到到1。这将再次对齐DQS和CK,以便DQ总线上的目标数据可以可靠地被捕获。由于这是由DDR3存储器控制器自动做的,电路板设计人员无须担心实施的细节。设计人员会从额外的裕度中得到好处,这是由DDR3存储器控制器中的写调整的特性所创建的。

图2 写调整的时序图

DDR3存储器时钟资源和接口模块

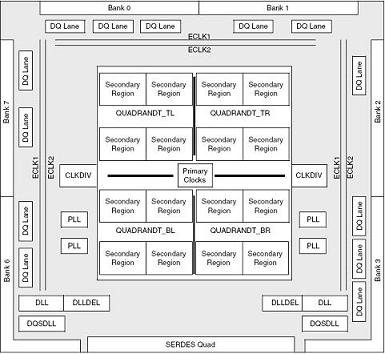

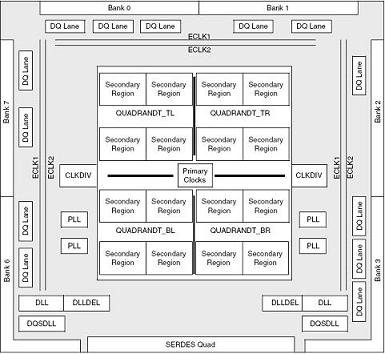

LatticeECP3 FPGA的I/O有专门的电路支持高速存储器接口,包括DDR、DDR2和DDR3 SDRAM存储器接口。如图3所示,ECP3系列还有专用的时钟资源,以支持下一代DDR3高速存储器控制器。边缘时钟(ECLK1,ECLK2)是高速,低相偏的时钟,用于时钟控制数据高速地进出器件。在DQS的通道提供时钟输入(DQS)和与该时钟相关的多达10个输入数据位。DQSBUF服务于每个DQS通道,以控制时钟访问和延迟。DQSDLL支持DQS通道(每个器件的左侧和右侧都有一个)。DQSDLL是专门用于构建90度时钟延迟的DLL。

图3 LatticeECP3 DDR存储器时钟资源

莱迪思的DQS电路包括一个自动时钟转换电路,简化了存储器接口设计,并确保了可靠的操作。此外,DQS的延迟块提供了针对DDR存储器接口所需的时钟对齐。通过DQS的延迟单元至专用的DQS布线资源,向PAD提供DQS信号。温度,电压和工艺变化对专用DQS延迟块产生的差异由设置的校准信号来补偿(7位延迟控制),校准信号源于器件对边的两个DQSDLL。在器件的一半,每个DQSDLL弥补各自边的DQS延迟。通过系统时钟和专用反馈环路,对DLL环进行了补偿。

LatticeECP3 FPGA的锁相环用于生成针对DDR3存储器接口时钟。例如,对于一个400 MHz的DDR3接口,通用锁相环用于生成三个时钟:400 MHz的时钟,有90 °相移的400 MHz时钟和200 MHz时钟。有90 °相移的400 MHz时钟用于生成DQ和DQS输出。没有相移的400 MHz时钟用于产生时钟(CLKP和CLKN)到DDR3存储器。200 MHz时钟用于生成地址和命令(ADDR/CMD)信号。该时钟的实现对客户是透明的,可用莱迪思的设计工具自动地实现。

DDR3所需的写调整是通过使用动态延迟输入至专门的DDR3存储器接口的模块,这称为DQSBUFD模块。这个DQSBUFD模块包含了DQS延迟块,时钟极性控制逻辑和数据有效模块。DDR3所需的写调整是通过使用动态延迟(DYNDELAY)输入DQSBUFD模块。根据写调整的要求,可以延迟每个DQS组的输出。

对于DDR3存储器读接口,当存储器件驱动DQS为低电平时,DQS转换检测块检测DQS的过渡情况,并生成读时钟来传输数据至FPGA。

莱迪思的IPexpress工具可用于生成上面阐述的DDR3存储器接口块。通过提供与高速DDR3存储器接口所需的合适块,这些在LatticeECP3中预制的块使设计人员减少了设计的复杂性。

DDR3存储器控制器

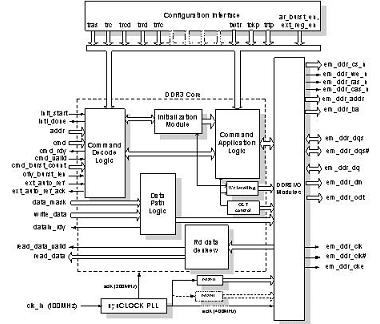

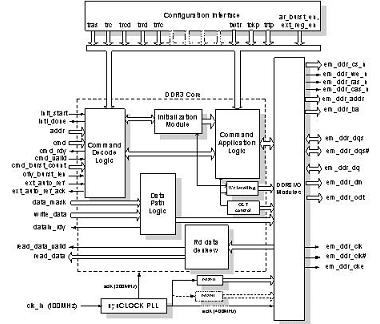

莱迪思提供一个全功能的DDR3存储器控制器IP核,接口至符合行业标准的DDR3元件和DIMM。莱迪思的DDR3存储器控制器的框图如图4所示。莱迪思的存储器控制器连接到LatticeECP3 的DDR3存储器接口模块(IO模块)和时钟电路,针对接口至DDR3存储器元件和DIMM,为客户提供现成的解决方案。这个控制器实现了一些功能,以改善整个吞吐量。例如,实现命令流水线,以改善整体吞吐量。该IP使用有效的分组(bank)管理技术来并行管理多个分组。这可以使访问延迟最小,有利于提高存储器的带宽。

图4 莱迪思DDR3存储器控制器框图

使用莱迪思的IPexpress工具,可以生成LatticeECP3 的DDR3存储器控制器。基于GUI的工具使设计人员能够指定存储器控制器的参数(时钟频率、数据总线宽度、配置等)以生成DDR3存储器控制器IP核。设计人员可以通过图形用户界面定制参数。例如,图形用户界面允许用户定制存储器的时序参数,并用新的时序值重新生成存储器控制器。除了DDR3存储器控制器IP核之外,还提供仿真模型和测试平台,这样设计人员可以在将它按装到电路板上之前,对设计进行测试。

LatticeECP3 DDR3存储器控制器已经用DDR3存储器元件和DIMM做了充分的验证。莱迪思还提供了多种硬件评估板,客户可用于检查LatticeECP3 DDR3存储器控制器的操作,接口至任何DIMM的 DDR3元件。LatticeECP3系列是业界唯一支持DDR3存储器接口的中档FPGA,从而针对下一代的系统设计,为设计人员提供了低成本,低功耗的解决方案。

结论

系统带宽的需求继续以指数形式增长。由于DDR3 SDRAM的价格下降了,DDR3 SDRAM芯片将更广泛地用于网络应用。这些增加系统带宽的要求正在推动着存储器的接口速度增加,同时继续使成本降低。用中档的FPGA促进稳定的高速存储器接口设计是LatticeECP3系列FPGA的主要目标。针对下一代存储器控制器的需要,ECP3的专用、灵活的DDR功能意味着现在设计人员有了一个节约成本的解决方案。LatticeECP3 DDR3基元与莱迪思的DDR3存储器控制器IP核的结合大大降低了DDR3存储器接口的复杂性,针对用DDR3实现下一代系统设计,促进更快地将产品推向市场。

由于系统带宽不断的增加,因此针对更高的速度和性能,设计人员对存储技术进行了优化。下一代双数据速率(DDR)SDRAM芯片是DDR3 SDRAM。 DDR3 SDRAM具有比DDR2更多的优势。这些器件的功耗更低,能以更高的速度工作,有更高的性能(2倍的带宽),并有更大的密度。与DDR2相比,DDR3器件的功耗降低了30%,主要是由于小的芯片尺寸和更低的电源电压(DDR3 1.5V而DDR2 1.8V)。 DDR3器件还提供其他的节约资源模式,如局部刷新。与DDR2相比,DDR3的另一个显著优点是更高的性能/带宽,这是由于有更宽的预取缓冲(与4位的DDR2相比,DDR3为8位宽),以及更高的工作时钟频率。然而,设计至DDR3的接口也变得更具挑战性。在FPGA中实现高速、高效率的DDR3控制器是一项艰巨的任务。直到最近,只有少数高端(昂贵)的FPGA有支持与高速的DDR3存储器可靠接口的块。然而,现在新一代中档的FPGA提供这些块、高速FPGA架构、时钟管理资源和需要实现下一代DDR3控制器的I/O结构。本文探讨设计所遇到的挑战,以及如何用一个特定的FPGA系列LatticeECP3实现DDR3存储器控制器。

DDR3存储器控制器的挑战

针对存储器控制器,DDR3器件面临一系列的挑战。DDR3的工作频率起始于DDR2的更高的工作频率,然后趋于更高的频率。 DDR3接口需要的时钟速度超过400 MHz。这是对FPGA架构的一个重大挑战。针对DDR3存储器控制器的架构,fly-by结构和读写调整变得更加复杂。

不同于DDR2的T型分支拓扑结构,DDR3采用了fly-by拓扑结构,以更高的速度提供更好的信号完整性。fly-by信号是命令、地址,控制和时钟信号。如图1所示,源于存储器控制器的这些信号以串行的方式连接到每个DRAM器件。通过减少分支的数量和分支的长度改进了信号完整性。然而,这引起了另一个问题,因为每一个存储器元件的延迟是不同的,取决于它处于时序的位置。通过按照DDR3规范的定义,采用读调整和写调整技术来补偿这种延迟的差异。fly-by拓扑结构在电源开启时校正存储器系统。这就要求在DDR3控制器中有额外的信息,允许校准工作在启动时自动完成。

图1 针对DDR3的Fly-by结构

读和写调整

在写调整期间,存储器控制器需要补偿额外的跨越时间偏移(对每个存储器器件,信号延迟是不同的),这是由于fly-by拓扑结构及选通和时钟引入的。如图2所示,源CK和DQS信号到达目的地有延迟。对于存储器模块的每个存储器元件,这种延迟是不同的,必须逐个芯片进行调整,如果芯片有多于一个字节的数据,甚至要根据字节来进行调整。该图说明了一个存储器元件。存储器控制器延迟了DQS,一次一步,直到检测到CK信号从0过渡到到1。这将再次对齐DQS和CK,以便DQ总线上的目标数据可以可靠地被捕获。由于这是由DDR3存储器控制器自动做的,电路板设计人员无须担心实施的细节。设计人员会从额外的裕度中得到好处,这是由DDR3存储器控制器中的写调整的特性所创建的。

图2 写调整的时序图

DDR3存储器时钟资源和接口模块

LatticeECP3 FPGA的I/O有专门的电路支持高速存储器接口,包括DDR、DDR2和DDR3 SDRAM存储器接口。如图3所示,ECP3系列还有专用的时钟资源,以支持下一代DDR3高速存储器控制器。边缘时钟(ECLK1,ECLK2)是高速,低相偏的时钟,用于时钟控制数据高速地进出器件。在DQS的通道提供时钟输入(DQS)和与该时钟相关的多达10个输入数据位。DQSBUF服务于每个DQS通道,以控制时钟访问和延迟。DQSDLL支持DQS通道(每个器件的左侧和右侧都有一个)。DQSDLL是专门用于构建90度时钟延迟的DLL。

图3 LatticeECP3 DDR存储器时钟资源

莱迪思的DQS电路包括一个自动时钟转换电路,简化了存储器接口设计,并确保了可靠的操作。此外,DQS的延迟块提供了针对DDR存储器接口所需的时钟对齐。通过DQS的延迟单元至专用的DQS布线资源,向PAD提供DQS信号。温度,电压和工艺变化对专用DQS延迟块产生的差异由设置的校准信号来补偿(7位延迟控制),校准信号源于器件对边的两个DQSDLL。在器件的一半,每个DQSDLL弥补各自边的DQS延迟。通过系统时钟和专用反馈环路,对DLL环进行了补偿。

LatticeECP3 FPGA的锁相环用于生成针对DDR3存储器接口时钟。例如,对于一个400 MHz的DDR3接口,通用锁相环用于生成三个时钟:400 MHz的时钟,有90 °相移的400 MHz时钟和200 MHz时钟。有90 °相移的400 MHz时钟用于生成DQ和DQS输出。没有相移的400 MHz时钟用于产生时钟(CLKP和CLKN)到DDR3存储器。200 MHz时钟用于生成地址和命令(ADDR/CMD)信号。该时钟的实现对客户是透明的,可用莱迪思的设计工具自动地实现。

DDR3所需的写调整是通过使用动态延迟输入至专门的DDR3存储器接口的模块,这称为DQSBUFD模块。这个DQSBUFD模块包含了DQS延迟块,时钟极性控制逻辑和数据有效模块。DDR3所需的写调整是通过使用动态延迟(DYNDELAY)输入DQSBUFD模块。根据写调整的要求,可以延迟每个DQS组的输出。

对于DDR3存储器读接口,当存储器件驱动DQS为低电平时,DQS转换检测块检测DQS的过渡情况,并生成读时钟来传输数据至FPGA。

莱迪思的IPexpress工具可用于生成上面阐述的DDR3存储器接口块。通过提供与高速DDR3存储器接口所需的合适块,这些在LatticeECP3中预制的块使设计人员减少了设计的复杂性。

DDR3存储器控制器

莱迪思提供一个全功能的DDR3存储器控制器IP核,接口至符合行业标准的DDR3元件和DIMM。莱迪思的DDR3存储器控制器的框图如图4所示。莱迪思的存储器控制器连接到LatticeECP3 的DDR3存储器接口模块(IO模块)和时钟电路,针对接口至DDR3存储器元件和DIMM,为客户提供现成的解决方案。这个控制器实现了一些功能,以改善整个吞吐量。例如,实现命令流水线,以改善整体吞吐量。该IP使用有效的分组(bank)管理技术来并行管理多个分组。这可以使访问延迟最小,有利于提高存储器的带宽。

图4 莱迪思DDR3存储器控制器框图

使用莱迪思的IPexpress工具,可以生成LatticeECP3 的DDR3存储器控制器。基于GUI的工具使设计人员能够指定存储器控制器的参数(时钟频率、数据总线宽度、配置等)以生成DDR3存储器控制器IP核。设计人员可以通过图形用户界面定制参数。例如,图形用户界面允许用户定制存储器的时序参数,并用新的时序值重新生成存储器控制器。除了DDR3存储器控制器IP核之外,还提供仿真模型和测试平台,这样设计人员可以在将它按装到电路板上之前,对设计进行测试。

LatticeECP3 DDR3存储器控制器已经用DDR3存储器元件和DIMM做了充分的验证。莱迪思还提供了多种硬件评估板,客户可用于检查LatticeECP3 DDR3存储器控制器的操作,接口至任何DIMM的 DDR3元件。LatticeECP3系列是业界唯一支持DDR3存储器接口的中档FPGA,从而针对下一代的系统设计,为设计人员提供了低成本,低功耗的解决方案。

结论

系统带宽的需求继续以指数形式增长。由于DDR3 SDRAM的价格下降了,DDR3 SDRAM芯片将更广泛地用于网络应用。这些增加系统带宽的要求正在推动着存储器的接口速度增加,同时继续使成本降低。用中档的FPGA促进稳定的高速存储器接口设计是LatticeECP3系列FPGA的主要目标。针对下一代存储器控制器的需要,ECP3的专用、灵活的DDR功能意味着现在设计人员有了一个节约成本的解决方案。LatticeECP3 DDR3基元与莱迪思的DDR3存储器控制器IP核的结合大大降低了DDR3存储器接口的复杂性,针对用DDR3实现下一代系统设计,促进更快地将产品推向市场。

- 利用FPGA和新技术,使LCD进入HDTV市场(08-27)

- 基于DSP和FPGA的电视观瞄系统设计(09-02)

- FPGA与SRAM相结合完成大容量数据存储(09-03)

- HDTV接收机中Viterbi译码器的FPGA实现(09-09)

- 基于FPGA的液晶显示接口设计 (09-26)

- 解决硬盘驱动器能耗难题(10-13)