利用可配置处理器来创建多标准多分辨率视频引擎

时间:10-23

来源:电子工程世界

点击:

随着消费类电子产品,尤其是手机、PDA和便携式媒体播放器(PMP)的急剧发展,其对于终端硅供应商的要求也大大提高。对这些供应商来说,设计仅仅能够适用于一到两个多媒体编解码器或无线标准的IC已经远远不够了。消费者希望他们的设备能够播放各种采用不同的编码标准和无线下载标准的媒体。因此,必须采取一个新的更具灵活性的途径来更好地适配新的媒体标准。在本文中,我们主要谈一谈视频解码器和编码器引擎所面对的挑战和机遇。

基于RTL的传统视频引擎设计方法

上一代视频ASIC设计的目的是为了解码和编码MPEG-2,因为这是DVD所使用的标准。其中也有些支持MPEG-1,可以播放VCD。大多数情况下,这种单个应用的逻辑实现策略就是:利用RTL(寄存器转换层,寄存器转换逻辑)来设计定制化MPEG-2解码器和编码器。下图1是一个典型的MPEG-2视频ASIC结构,展示了由视频子系统、主控制器和片上存储器组成的RTL功能块。

随着市场形势的改变,现在的视频ASIC必须能够支持多种视频标准,并具有多个分辨率。由于下列原因,传统的RTL方法已经不再有效:

·随着标准数量的增加,RTL功能块的数量和复杂性也增加;

·无论是执行一个新的视频标准,还是升级现有的已执行的标准,或者修改bug,都需要进行硅芯片重制;

·在第一代硅执行之后的这4-5年内,视频编解码器,尤其是编码器在性能上(比特率、性能)有很大的改进。要执行这些改进的成果,也必须在所有的RTL方法中进行硅芯片重制。

在视频引擎中使用处理器,而不是固定的RTL

那么,有没有其它办法呢?使用一个可编程处理器是最佳方案,因为它可以解决上面提到的所有问题:(1)处理器和编解码器之间很容易建立连接端口;(不论是采用新的视频标准,还是升级现有的编解码器或者修改bug,都可以很容易地在软件中进行);(3)通过软件升级,可以很容易地应用视频编解码器执行中的改进。

但是,由于其性能瓶颈,传统的处理器只能用于一般的编码,而不能用于视频引擎。嵌入式DSP也不是专为视频而设计的,但拥有通用DSP应用所需的硬件功能单元、指令和接口。因此,要在传统的RISC和DSP处理器上执行视频编解码,就意味着这些处理器必须以非常高的速度运行(MHz),而且还需要大量内存并消耗大量功率,但是在便携式设备中,这显然是行不通的。

只要我们对某个视频内核中所需的计算次数作一个简单分析,就很容易得出这一点。绝对误差和是大多数视频解码运算的动作估计中所进行的一个重要计算步骤。SAD运算的目的在于发现两个连续视频帧之间的宏模块的运动。它是通过计算这两个宏模块中每套相应的象素值之间的绝对误差之和来实现这一目的的。

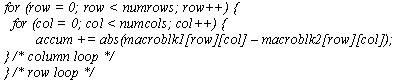

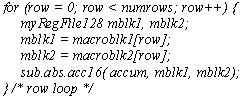

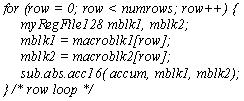

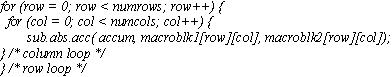

下面的C代码展示了SAD运算的一次简单执行:

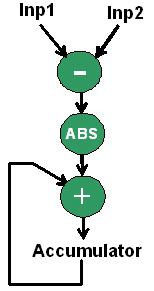

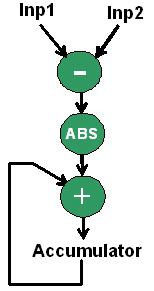

图1展示了SAD运算中的基本计算步骤。如图所示,其中主要进行的计算有减、算绝对值和结果累计。

图1:绝对误差和(SAD)内核中进行的主要计算

计算一个RISC上的两个16x16宏模块的SAD需要进行256次减法、256次求绝对值和256次相加――总共进行了768次计算,还不包括传输数据所需的负载与内存。由于每一帧当中所有的宏模块都必须进行这一运算,很显然这在计算上成本是很昂贵的,而且会随着视频帧分辨率的增加而越来越难。

实际上,在一个带有一些如相乘和乘法累加等指令的中等范围通用型RISC处理器上,如果要以CIF的分辨率进行H。26?Baseline解码,需要250MHz的速率,而如果进行H。26?Baseline编码,所需速率更是超过1GHz。这意味着光是处理器内核就要消耗将近500mW的功率,更不用提内存和视频片上系统中其它部分消耗的功率了。很显然这种处理器不能作为嵌入式多媒体处理器用于便携式设备中。

可配置处理器解决了问题

如何在处理器中进行SAD运算呢?有一个方法是编写一个能够同时进行"减-求绝对值-加"计算的指令。这可以将16x16宏模块所需的计算次数从768减少到256。另外,由于一个执行这种综合化简单运算的功能单元一般都能够优化成一个周期,意味着计算周期也被减少到了256。

但是如何执行这个"减-求绝对值-加"指令呢?

在这个时候,就需要可配置处理器了。可配置处理器是嵌入式的,设计者可以配置选项菜单中进行选择,并通过添加特殊应用指令、寄存器文件和接口来扩展处理器功能。

下面是目前的可配置处理器具备的一些可配置和可扩展性功能,传统的固定式处理器是没有这些功能的:

可配置性,有下面的一系列选项可供选择:

·设计者想要或者不想要的指令,包括:16x16相乘或乘法累加、漏斗转换、浮点指令等;

·零耗循环、5或7个步进管线、本地数据加载/存储单元的数量等各种功能;

·是否需要内存保护、内存转换或者一个全内存管理单元(MMU);

·是否需要一个系统总线接口;

·系统总线和本地内存接口的宽度;

·本地内存的数量和大小;

·中断的次数、种类和等级

可扩展性,可自由添加下列由设计者自定义的组件:

·寄存器和寄存器文件;

·多周期、任意复杂功能单元;

·SIMD功能单元;

·将基本型处理器转换成多发射处理器;

·定制能够直接从数据路径读取和写入的接口,例如在处理器内核上的类似于GPIO(通用IO)的端口或管脚,以及可以用来和其它逻辑或者处理器内核进行连接的外置FIFO。

可配置性的优点在于使你可以通过选择你的应用所需的功能选项来构建一个规模适中的处理器,而可扩展性的优点则是让设计者可以通过创造能加快应用速度的指令、寄存器文件、功能单元和接口来定制处理器,使之完全与其视频应用相匹配。但必须注意的是,只有当今先进的可配置处理器才具能提供设计者自定义可扩展性。

利用可配置处理器来构建视频引擎

创建能进行多次运算的功能单元

这一步即是SAD运算和加速SAD运算的内容。

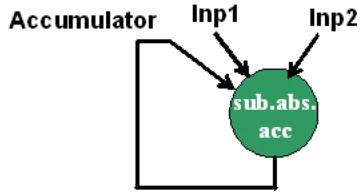

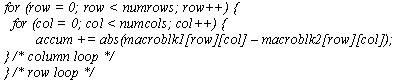

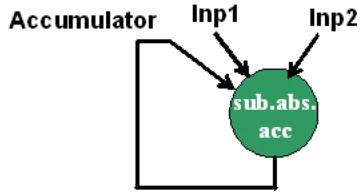

对于可配置处理器来说,要添加这一综合运算功能简直是小菜一碟。它可以添加名为"sub。abs。acc(减-求绝对值-加)"的新指令来进行"相减、求绝对值和相加"运算。如图3所示。

图2:进行"相减、求绝对值和相加"运算的新指令

现代的可配置处理器(例如Tensilica的Xtensa处理器)所配的软件工具会自动修改编辑器工具,包括C/C++编辑器、汇编程序、调试器、模仿器和ISS(指令集仿真器)。此时,C编辑器会识别新的C内部指令"sub。abs。acc"并安排相应的指令,调试器则显示sub。abs。acc功能模块中使用的内部信号,同时,汇编程序会将之作为一个新的指令进行处理,而ISS则对之进行周期精确级仿真。

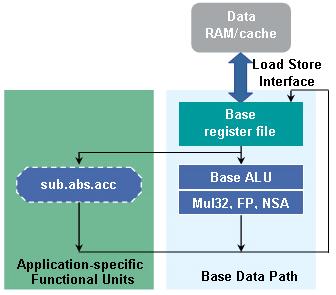

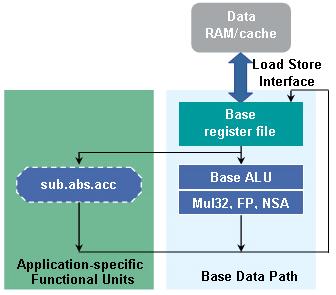

图3是嵌入这种新的视频特殊功能单元之后数据路径的简化图。必须注意的是,硬件生成工具不仅能够自动生成功能单元逻辑,还可自动嵌入正向路径、控制逻辑和旁路逻辑来将这一新的功能单元和数据路径的其它部分相连。

图3:嵌入sub。abs。acc视频特殊功能单元之后数据路径的简化图

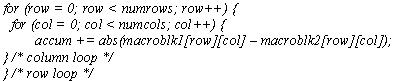

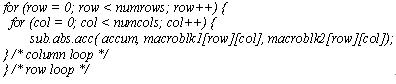

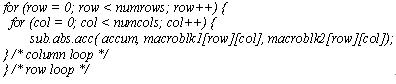

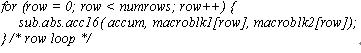

现在,运用了C内部指令来进行SAD运算的C代码就变为:

正如前文所说,这将16x16宏模块(例如:numrows=numcols=16)的计算次数减少至256次。

创建SIMD功能单元

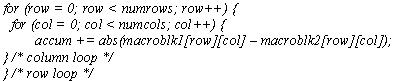

除了上面的成果,我们还可以实现进一步改进。在这个内核中,内循环穿越整个宏模块,并进行同样的计算。此时恰恰可以创建一个SIMD(单指令多数据)功能单元和相应的指令sub。abs。acc16,来在16象素上同时进行"相减、求绝对值和相加"运算,如图4所示。

图4:SIMD在16象素上同时进行的"相减、求绝对值和相加"运算

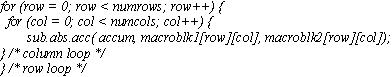

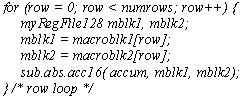

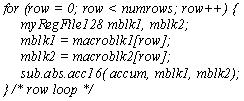

相应的C内部指令是sub。abs。acc16,用来在SAD运算中重写C代码:

此时,SAD运算的次数从768次减少至仅16次。

但是,上面的C代码是不精确的。我们掩盖了一个细节,那就是sub。abs。acc16指令要求来自两个宏模块的128-b的输入。这要求支持两个功能-一个128b的寄存器文件和一个宽加载/存储接口-这些会在接下来的部分进行讨论。

创建自定义寄存器文件

在可配置处理器中创建一个任意大小的自定义寄存器文件是很简单的。例如,一个名为"myRegFile128"并带有4个寄存器的128b寄存器文件,就可以创建一个相应的新的C数据类型,用于C/C++编码中来显示变量。另外,软件工具还可以进行"移动"操作,能将各种C数据类型转换成这种新的自定义数据类型。

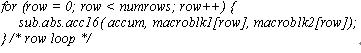

因此,使用了sub。abs。acc16内部指令和新的寄存器文件的SAD运算的正确的C编码是:

接着,C/C++编辑器将生成移动指令来将数据从普通的C数据类型转化成自定义C数据类型"myRegFile128",并为新的寄存器文件进行寄存器分配。

基于RTL的传统视频引擎设计方法

上一代视频ASIC设计的目的是为了解码和编码MPEG-2,因为这是DVD所使用的标准。其中也有些支持MPEG-1,可以播放VCD。大多数情况下,这种单个应用的逻辑实现策略就是:利用RTL(寄存器转换层,寄存器转换逻辑)来设计定制化MPEG-2解码器和编码器。下图1是一个典型的MPEG-2视频ASIC结构,展示了由视频子系统、主控制器和片上存储器组成的RTL功能块。

随着市场形势的改变,现在的视频ASIC必须能够支持多种视频标准,并具有多个分辨率。由于下列原因,传统的RTL方法已经不再有效:

·随着标准数量的增加,RTL功能块的数量和复杂性也增加;

·无论是执行一个新的视频标准,还是升级现有的已执行的标准,或者修改bug,都需要进行硅芯片重制;

·在第一代硅执行之后的这4-5年内,视频编解码器,尤其是编码器在性能上(比特率、性能)有很大的改进。要执行这些改进的成果,也必须在所有的RTL方法中进行硅芯片重制。

在视频引擎中使用处理器,而不是固定的RTL

那么,有没有其它办法呢?使用一个可编程处理器是最佳方案,因为它可以解决上面提到的所有问题:(1)处理器和编解码器之间很容易建立连接端口;(不论是采用新的视频标准,还是升级现有的编解码器或者修改bug,都可以很容易地在软件中进行);(3)通过软件升级,可以很容易地应用视频编解码器执行中的改进。

但是,由于其性能瓶颈,传统的处理器只能用于一般的编码,而不能用于视频引擎。嵌入式DSP也不是专为视频而设计的,但拥有通用DSP应用所需的硬件功能单元、指令和接口。因此,要在传统的RISC和DSP处理器上执行视频编解码,就意味着这些处理器必须以非常高的速度运行(MHz),而且还需要大量内存并消耗大量功率,但是在便携式设备中,这显然是行不通的。

只要我们对某个视频内核中所需的计算次数作一个简单分析,就很容易得出这一点。绝对误差和是大多数视频解码运算的动作估计中所进行的一个重要计算步骤。SAD运算的目的在于发现两个连续视频帧之间的宏模块的运动。它是通过计算这两个宏模块中每套相应的象素值之间的绝对误差之和来实现这一目的的。

下面的C代码展示了SAD运算的一次简单执行:

图1展示了SAD运算中的基本计算步骤。如图所示,其中主要进行的计算有减、算绝对值和结果累计。

图1:绝对误差和(SAD)内核中进行的主要计算

计算一个RISC上的两个16x16宏模块的SAD需要进行256次减法、256次求绝对值和256次相加――总共进行了768次计算,还不包括传输数据所需的负载与内存。由于每一帧当中所有的宏模块都必须进行这一运算,很显然这在计算上成本是很昂贵的,而且会随着视频帧分辨率的增加而越来越难。

实际上,在一个带有一些如相乘和乘法累加等指令的中等范围通用型RISC处理器上,如果要以CIF的分辨率进行H。26?Baseline解码,需要250MHz的速率,而如果进行H。26?Baseline编码,所需速率更是超过1GHz。这意味着光是处理器内核就要消耗将近500mW的功率,更不用提内存和视频片上系统中其它部分消耗的功率了。很显然这种处理器不能作为嵌入式多媒体处理器用于便携式设备中。

可配置处理器解决了问题

如何在处理器中进行SAD运算呢?有一个方法是编写一个能够同时进行"减-求绝对值-加"计算的指令。这可以将16x16宏模块所需的计算次数从768减少到256。另外,由于一个执行这种综合化简单运算的功能单元一般都能够优化成一个周期,意味着计算周期也被减少到了256。

但是如何执行这个"减-求绝对值-加"指令呢?

在这个时候,就需要可配置处理器了。可配置处理器是嵌入式的,设计者可以配置选项菜单中进行选择,并通过添加特殊应用指令、寄存器文件和接口来扩展处理器功能。

下面是目前的可配置处理器具备的一些可配置和可扩展性功能,传统的固定式处理器是没有这些功能的:

可配置性,有下面的一系列选项可供选择:

·设计者想要或者不想要的指令,包括:16x16相乘或乘法累加、漏斗转换、浮点指令等;

·零耗循环、5或7个步进管线、本地数据加载/存储单元的数量等各种功能;

·是否需要内存保护、内存转换或者一个全内存管理单元(MMU);

·是否需要一个系统总线接口;

·系统总线和本地内存接口的宽度;

·本地内存的数量和大小;

·中断的次数、种类和等级

可扩展性,可自由添加下列由设计者自定义的组件:

·寄存器和寄存器文件;

·多周期、任意复杂功能单元;

·SIMD功能单元;

·将基本型处理器转换成多发射处理器;

·定制能够直接从数据路径读取和写入的接口,例如在处理器内核上的类似于GPIO(通用IO)的端口或管脚,以及可以用来和其它逻辑或者处理器内核进行连接的外置FIFO。

可配置性的优点在于使你可以通过选择你的应用所需的功能选项来构建一个规模适中的处理器,而可扩展性的优点则是让设计者可以通过创造能加快应用速度的指令、寄存器文件、功能单元和接口来定制处理器,使之完全与其视频应用相匹配。但必须注意的是,只有当今先进的可配置处理器才具能提供设计者自定义可扩展性。

利用可配置处理器来构建视频引擎

创建能进行多次运算的功能单元

这一步即是SAD运算和加速SAD运算的内容。

对于可配置处理器来说,要添加这一综合运算功能简直是小菜一碟。它可以添加名为"sub。abs。acc(减-求绝对值-加)"的新指令来进行"相减、求绝对值和相加"运算。如图3所示。

图2:进行"相减、求绝对值和相加"运算的新指令

现代的可配置处理器(例如Tensilica的Xtensa处理器)所配的软件工具会自动修改编辑器工具,包括C/C++编辑器、汇编程序、调试器、模仿器和ISS(指令集仿真器)。此时,C编辑器会识别新的C内部指令"sub。abs。acc"并安排相应的指令,调试器则显示sub。abs。acc功能模块中使用的内部信号,同时,汇编程序会将之作为一个新的指令进行处理,而ISS则对之进行周期精确级仿真。

图3是嵌入这种新的视频特殊功能单元之后数据路径的简化图。必须注意的是,硬件生成工具不仅能够自动生成功能单元逻辑,还可自动嵌入正向路径、控制逻辑和旁路逻辑来将这一新的功能单元和数据路径的其它部分相连。

图3:嵌入sub。abs。acc视频特殊功能单元之后数据路径的简化图

现在,运用了C内部指令来进行SAD运算的C代码就变为:

正如前文所说,这将16x16宏模块(例如:numrows=numcols=16)的计算次数减少至256次。

创建SIMD功能单元

除了上面的成果,我们还可以实现进一步改进。在这个内核中,内循环穿越整个宏模块,并进行同样的计算。此时恰恰可以创建一个SIMD(单指令多数据)功能单元和相应的指令sub。abs。acc16,来在16象素上同时进行"相减、求绝对值和相加"运算,如图4所示。

图4:SIMD在16象素上同时进行的"相减、求绝对值和相加"运算

相应的C内部指令是sub。abs。acc16,用来在SAD运算中重写C代码:

此时,SAD运算的次数从768次减少至仅16次。

但是,上面的C代码是不精确的。我们掩盖了一个细节,那就是sub。abs。acc16指令要求来自两个宏模块的128-b的输入。这要求支持两个功能-一个128b的寄存器文件和一个宽加载/存储接口-这些会在接下来的部分进行讨论。

创建自定义寄存器文件

在可配置处理器中创建一个任意大小的自定义寄存器文件是很简单的。例如,一个名为"myRegFile128"并带有4个寄存器的128b寄存器文件,就可以创建一个相应的新的C数据类型,用于C/C++编码中来显示变量。另外,软件工具还可以进行"移动"操作,能将各种C数据类型转换成这种新的自定义数据类型。

因此,使用了sub。abs。acc16内部指令和新的寄存器文件的SAD运算的正确的C编码是:

接着,C/C++编辑器将生成移动指令来将数据从普通的C数据类型转化成自定义C数据类型"myRegFile128",并为新的寄存器文件进行寄存器分配。

- 数字机顶盒技术综述 (08-08)

- H.264:视频压缩编码的新发展(08-28)

- H.264/AVC视频压缩编码标准的新进展(08-29)

- 数字视频系统中的集成新概念(下)(09-12)

- 数字视频系统设计中的集成新概念(上)(09-12)

- H.264视频解码芯片中视频控制器的设计 (01-03)