四路视频输入处理器SAA7144HL的应用

SAA7144HL是4个单独的多标准视频解码器的组合,是完全的3.3V CMOS电路和高集成的视频监测应用电路。详细介绍了SAA7144HL的内部功能,给出了SAA7144HL的典型应用电路。

l 引言

SAA7144HL是4个单独的多标准视频解码器的组合,是一个完全的3.3V CMOS电路和高集成的视频监测应用电路。基于行锁定时钟解码原理的4个视频解码器可以把彩色PAL、SECAM和NTSC信号解码成兼容彩色分量值的CCIR 601,并可接收来自TV或VTR的共8个复合电视广播信号源的模拟输入。

SAA7144HL集成的高性能多标准数据双向限幅器支持多VBI数据标准。

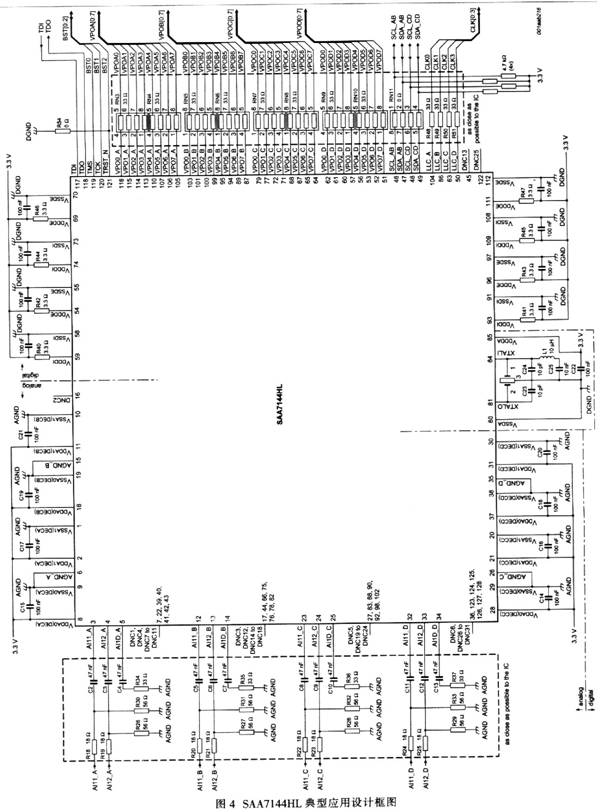

2 SAA7144HL的组成

SAA7144HL的功能方框如图1所示。四个视频解码器(A,B,C,D)中的任意一个都包含一个对于两路复合电视广播信号(CVBS)源的源选择模拟处理电路、抗混叠滤波器、模数转换器(ADC)、自动箝位和增SECAM和NTSC)、亮度对比度饱和度控制电路、多标准双向限幅器和一个27 MHz VBI数据旁路。

SAA7144HL的4个解码器通过I2C总线控制,2个解码器共用一个总线接口,全部读取反馈性能由外部控制,比特率可达400 kbit/s。所有解码器共用的所有标准只需要一个24.576 MHz石英晶体。解码器可以自动检测50Hz和60Hz的场频率,并自动在PAL和NTSC标准间转换。3.3V CMOS设备具有5 V的数字输入和I/O端口。SAA7144HL采用LQFPl28小型封装。

3 SAA7144HL的典型应用设计

3.1 模拟控制电路

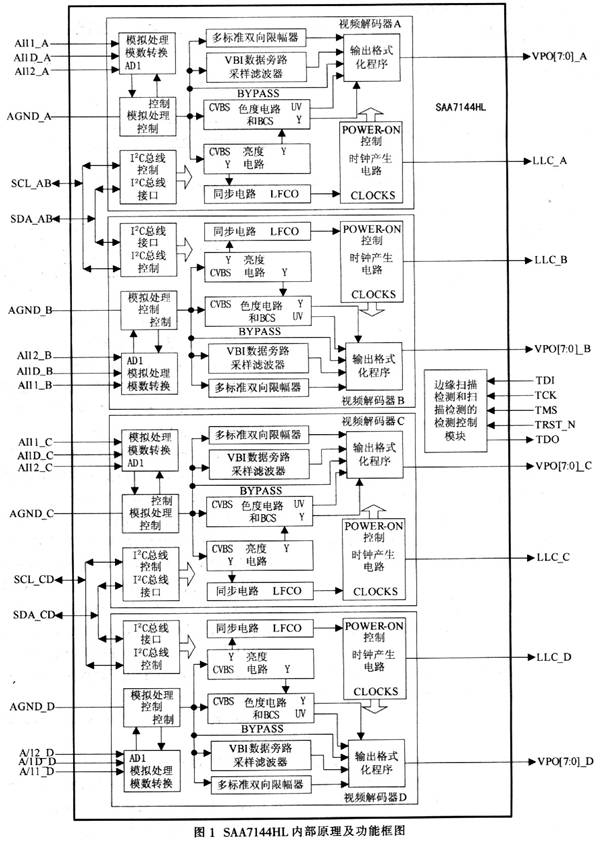

抗混叠干扰滤波器通过滤波控制电路与线锁时钟频率相适应。其特征曲线如图2所示,在垂直消隐阶段没有增益和箝位控制功能。

3.2 箝位电路

箝位电路控制模拟输入信号的正确箝位,耦合电容器也用于存储和滤波箝位电压。内部数字箝位比较器用来产生与上箝位或下箝位相关联的信息。双ADC通道的箝位级由亮度(120)和色度(256)确定。通常使用的箝位时间由视频HCL脉冲后沿设置。

3.3 增益控制电路

增益控制电路通过I2C总线接收模拟放大器的静态增益级或通过作为模拟输入控制(AICO)一部分的AGC自动控制该放大器。

亮度自动增益控制把CVBS信号放大到需要的信号幅度,与ADC输入电压范围相匹配。AGC的有效时间与视频信号底部同步。

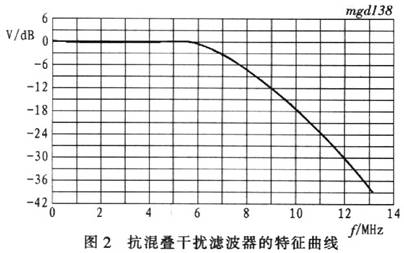

3.4 时钟发生电路

内部的CGC产生视频输入处理器需要的全部时钟信号。内部信号LFCO是一个数模转换信号,由水平锁相环(PLL)提供,它是行频的倍数:

6.75 MHz=429xfH(50Hz),或6.75 MHz=432xfH(60Hz)

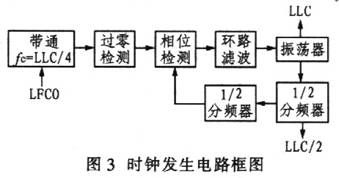

LFCO信号乘以内部锁相环电路的2和4倍频因子获得输出时钟信号,PLL电路包括相位检测器、环路滤波、压控振荡器(VCO)和分频器。矩形输出时钟有50%的占空比。时钟频率如表l所示,时钟发生电路框图如图3所示。

3.5 多标准VBI双向限幅电路

多标准数据双向限幅器是一个VBI(Vertical Blanking Interval)和FF(Full Field)视频数据采集模块。与软件模块相结合,限幅器可以采集几乎所有现存格式的广播VBI和FF数据。

与VBI数据限幅器相匹配的实现和程序设计模型嵌入在多媒体视频数据采集电路SAA5384中。该电路可在时钟运行周期中恢复当前时钟相位,把数据位数限制在选定的数据率上,并把它们组成字节。时钟频率、信号源、场频率和容许的误差数必须通过子地址40H,比特位7~4的I2C总线规定。每一个VBI行可选择多个标准,设计的理想标准是通过I2C总线的41H~57H子地址(LCR2[7:0]到LCR24[7:0])。为了调节限幅器对信号源的处理,通过I2C总线的5BH(位2~0),59H(HOFF10~HOFF0)和5BH(位4),5AH(VOFF8~VOFFO)子地址完成水平和垂直方向的偏移补偿。

VBI数据解码的格式化操作在VPO总线输出接口内完成。

3.6 未处理VBI数据旁路

对于一个27 MHz未处理VBI数据旁路,数字化CVBS信号经过模数转换后上抽样。上抽样后的CVBS频率成分通过插值滤波器获得。

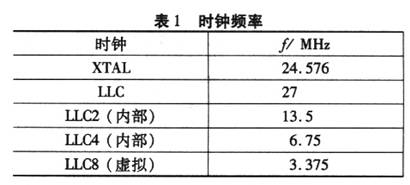

SAA7144HL的典型应用设计框图如图4所示。