技术文章:高清电视音频解码的定点DSP实现

点化程序时,以浮点程序为模板,逐个将模块改造成定点. 每做完一个模块,将定点程序解码结果与浮点程序的解码结果进行比较,直到差值达到要求为止. 每个模块改造前,先估计本模块内数据动态范围,再决定采用何种精度. 其中余弦函数的定点运算通过查表法实现,即先把[ 0 ,π/ 2]间划分为212 个小格子,然后把弧度值映射到小格子上,通过查表

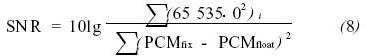

其中:PCMfix 为定点程序解码结果; PCMfloat 为浮点程序解码结果; 65 535. 0 为两个16 位PCM 样点之差的最大值.有的文献以∑PCM2float 为分子,这样算出来的结果与特定的码流有关,若码流PCM 样点值较大,计算出信噪比则较大. 而式(8) 不受具体码流的影响,客观地对不同码流作出评价对比. 定点程序分别经过男声、女声,小提琴声,海浪声和进行曲乐声等码流测试,SNR 都在74~78 dB 范围内,获得了较好的效果.

4 定点DSP 实现音频解码算法

TMS320DM642 是Ti 公司最新推出的一款针对多媒体处理领域的DSP ,它在C64x 的基础上,增加了许多外围设备和接口. 频率为600 MHz 的DM642 能够以30 帧的速度同时处理多达4 个分辨率为D1 (720 ×480) 的MPEG2 视频编码译码器. 此外,DM642 还能实时进行全面的Main-Profile-at-Main-Level (MP @ML) MPEG-2 视频编码,具有32MB 外部SDRAM、4 MB 闪存、组合视频输入/ 输出、S-视频输入/ 输出、V GA 输出端口以及支持媒体流的以太网端口.

将程序移植到DSP 上分两个阶段[6 ] : 第1 阶段,不考虑DSP 有关知识,根据DVP 改进算法编写C 程序,再在CCS 环境下调试C 程序,编译产生在C6000 内运行的代码,运用CCS 下的分析工具断点和profile 等,查找程序中运算量最大的部分,改进这部分代码性能;第2 阶段,使用DSP 提供的内联函数代替复杂的C 语言程序,使用数据打包技术,对短字长的数据使用宽长度访问,并通过消除冗余循环、循环展开等方法优化循环程序. 最后,利用DSP提供的汇编优化器,选定合适的优化选项进行编译,此步可通过线性汇编,在底层更好地利用资源.目标DSP 的乘法器为16 位×16 位,而程序中用到32 位×32 位乘法,结果为32 位. 因此采用3个16 位×16 位乘法代替,输出结果仍保留32 位.其方法为

Y32 = X132 ?X232 = X1low16 ?X2low16 + ( X1high16 ?X2low16 + X1low16 ?X2high16 ) n<<16 (9)

经过测试,该式计算对性能没有影响.

1) 输入控制

DSP 解码时,将待解压缩的mp3文件转化成dat 格式的文件,DSP 可直接将dat 格式的数据加载到片外存储器中. 具体方法为,先在程序中定义一个与mp3 文件相同大小的数组,然后将dat 文件放到数组首地址所指向的区域并指定数据长度. 由于mp3 文件大小为几兆,所以定义的数组长度超过bss 段最大偏移,需定义成far 型;也可以不用far 声明数组,而将编译方式改成大模式.大模式下bss 段的大小无任何限制,但编译器对变量使用寄存器间接寻址方式,这样需要3 条指令才能加载一个变量,故对变量存取速度很慢.

2) 输出控制:采用DSP 提供的实时操作系统

DSP/ BIOS 实现实时输出音频. 首先在DSP/ BIOS配置工具中建立TSK 对象,并与解码函数相对应,然后指定函数优先级,DSP/ BIOS 将自动进行任务调度和执行. 在配置工具中还需指定内存分配情况. DM642 中L2 cache 和片内存储器共用,可使用芯片支持库CSL 的API 函数分配cache 及片内存储器大小. 片内存储器的一部分作为子带滤波器申诸的动态空间.

调试时可以用LOG 对象显示解码进度, 以LOG_ printf 代替C 语言调试中的printf , 因为printf 不是DSP 中的指令,将占用大量的时钟周期,在对实时性要求很高的应用中根本无法满足要求. LOG_printf 语句可以满足实时要求. 先在DSP/BIOS 配置工具里建立一个LO G 对象,在Message窗口可实时观测程序进度,几乎不影响程序性能.DSP/ BIOS 提供两种数据传输模型,管道模型(pipe) 用于PIP 和HST 模块;流模型( st ream) 用于SIO 和DEV 模块. 管道支持底层的通信,而流支持高级的与设备无关的I/ O. 音频口输出时采用流模型,流和I/ O 设备交互的数据流向如图3 所示. 流模块(SIO) 使用驱动程序(由DEV 模块管理) 与这些设备交互. 控制输出前先进行初始化,即在DSP/BIOS 配置工具里定义一个User-Defined Devices对象, 再使用音频口初始化函数_EVMDM642 _EDMA_AIC23_init 对此对象进行初始化. 上层的API 函数即可对这个设备进行操作,通过结构体SIO_At t r s 设置设备特征.

图3 流和设备间的交互

解码输出过程为:首先使用SIO_create 产生一个指向设备的流. 流以异步方式进行I/ O 操作,定义两个指向输出流的缓冲区用以数据交换,数据输入和输

- 利用FPGA和新技术,使LCD进入HDTV市场(08-27)

- 下一代机顶盒的技术趋势和解决方案(08-30)

- HDTV接收机中Viterbi译码器的FPGA实现(09-09)

- 深入浅出讲解高清数字电视(09-24)

- 三重播放网络环境下验证IPTV服务质量(10-15)

- 基于TVP9000的高清数字电视设计(01-06)