微电子所造强力数据转换器,30GSps超高速这是要逆天啊

超高速模拟数字转换器(ADC)和数字模拟转换器(DAC)是下一代光通信及无线宽带领域的核心芯片,在大数据中心、以太网光互联、短距离互联通讯等领域有着广泛应用。美、日等国自上世纪60、70年代起始终占据该领域的技术最高点。

中国科学院微电子研究所于2006年在研究员刘新宇带领下成立了超高速数模混合电路研发团队,以实现AD/DA研制的整体跨越为目标。经过近10年的技术积累,团队在超高速ADC/DAC的设计方法、理论分析方法以及封装测试等方面积累了丰富的研究经验,在国内外一流学术刊物上发表了20多篇学术论文,申请了20余项发明专利,建立起了通用采样率为Gsps的数模混合电路的设计分析和测试评估平台。

在国家"863"项目的支持下,该团队的研究工作取得了突破性进展,成功研制出超高采样率、宽频带的30Gsps 6bit ADC/DAC芯片,大大缩短了与先进国家的技术差距,为我国在该领域摆脱国外技术壁垒限制增加了关键性的筹码,对下游产业的发展起到了极大的促进作用。该芯片的使用简单灵活,可实现并行多波段/多波束运行,并可提供较高的动态范围。目前,该芯片已在武汉邮电科学院构建的1Tb/s相干光OFDM传输验证平台上实现应用验证。

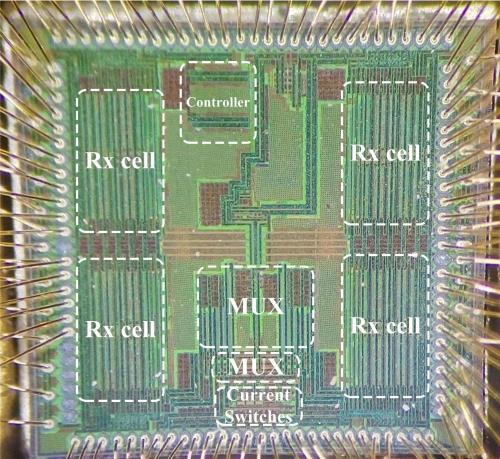

30Gsps 6bit ADC芯片面积为3.9mm x 3.3mm ,采用4路交织技术,子ADC采用自主创新的折叠内插架构。芯片内部集成三项误差校准电路,通过与FPGA配合可实现通道之间的自动校准。芯片输出采用24路高速串行数据接口,支持在30GSps采样率下全速率输出。芯片的最高采样率为30Gsps,每秒可产生300亿次模数转换,总功耗为8W。该款芯片的-3dB带宽为18GHz。在30Gsps采样率下,低频有效位达到5bit,高频有效位大于3.5bit,无杂散动态范围(SFDR)大于35dBc。

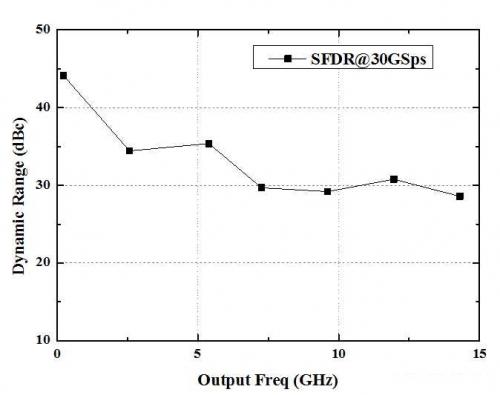

30Gsps 6bit DAC的芯片面积为3mm x 2.8mm,采用了分段式电流舵DAC架构。该芯片集成24路高速串行数据接收器,以及4-1MUX高速电路,支持在30GSps采样率下全速率输出。该芯片还集成了占空比校正和延迟偏差校准电路。测试结果表明芯片在30Gsps 采样率下工作时,低频无杂散动态范围(SFDR)达到44dBc,在第一奈奎斯特区内SFDR大于28.5dBc。芯片总功耗6.2W。

图1. 30Gsps 6bit ADC的实物照片和高频测试结果

图2. 30Gsps 6bit DAC的实物照片和SFDR测试结果

- ST发布VIPer17开关式离线电源转换器(04-28)

- 德州仪器推出最小型双通道 16 位 800 MSPS 内插 DAC(03-08)

- 恩智浦发布基于LatticeECP3 FPGA器件的CGV高速转换器演示板(04-27)

- IDT推出了 SyncE(同步以太网)解决方案(10-05)

- 大唐移动利用 ADI 公司的高速四通道 DAC 实现高性能、小尺寸无线基站(04-05)

- 友尚集团推出基于的TI的三相智能电表SoC系列(10-13)