PA数据链路解密之PCI-E总线

摘要:作为新一代的通用总线接口标准,PCI-Express(PCI-E)高带宽、低延迟、可扩展、支持热插拔等优点,使其全面取代了PCI、AGP等早期总线。ZLG致远电子功率分析仪的内部多个高速数据总线中,也包含了PCI-E。下面我们来一起认识这一接口。

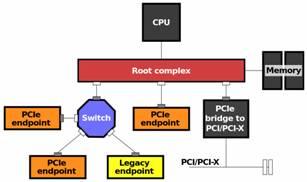

1.1 架构

图 1 框架图

1、 Root Complex(RC)

PCI-E根控制器,集成在主处理器系统中,管理处理器与PCIE设备的连接。

2、 Switch

PCI-E交换设备,用于PCI-E总线的扩展。

3、 Bridge

PCI-E桥设备,用于PCI-E与其它总线的桥接。例如:PCIE to PCI桥。

4、 Endpoint(EP)

PCI-E终端设备,例如网卡等通讯板卡或其它数据采集板卡。

实际应用中,我们关注较多的则是此类设备。

1.2 通讯

1、 地址映射

EP设备可通过配置自身PCI-E控制器,将设备内部一段内存地址映射到CPU保留地址空间。CPU通过访问该映射后的地址,便可透明地读写设备,而不必关心物理传输细节。

2、 直接内存访问

EP设备具有总线主控能力,即能够主动访问CPU地址空间。通过修改PCI-E控制器的地址映射,配合DMA控制器,可以实现无需CPU干预的数据传输。

3、 MSI(Message Signaled Interrupt)中断

EP设备可以将某个特定消息写到特定地址,触发一个CPU中断。

1.3 枚举

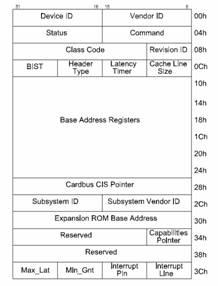

1、 配置空间

图 2 1 配置空间

如图2所示,配置空间是由EP设备定义,用于描述EP设备资源及特性的一组寄存器。在枚举过程中,RC会扫描PCI-E总线上的所有设备。通过访问该设备的配置空间,可以获得加载EP设备驱动所需的DeviceID、VendorID等信息。

2、 BAR(Base Address Registers)

EP设备可向RC请求将自身的1~6段设备地址映射到CPU的地址空间,这1~6个CPU地址由RC软件在枚举过程中分配并回写到配置空间中的BAR寄存器。

3、 枚举流程

图 3 枚举流程

如图3所示,CPU以一定顺序扫描系统内的PCI-E总线,为发现的设备分配总线号、设备号,构建设备树,分配地址空间并回写BAR。操作系统启动后,将根据DeviceID、VendorID找到匹配的驱动程序并加载运行。

- 美超微携新100Gbps高性能计算集群解决方案参展SC 2015(10-18)

- QLogic可靠性—“值得信赖”(06-17)

- 浏览色情网站的历史画面,将被NVIDIA GPU重现?(01-11)