Synopsys新型DDR4 IP套件提高高性能云计算系统的容量与可靠性

DesignWare DDR4 IP解决方案助力服务器更快解决复杂计算问题

亮点

不降低性能的同时,内存容量扩展高达400%

利用高级错误校正码,在失效的DRAM上重建所有数据

运用嵌入式校准处理器,提供最高的设计裕度与信号完整性

通过重试失败的内存命令,减少系统宕机时间

新思科技(Synopsys,Inc.,纳斯达克股票代码:SNPS)日前宣布:3200Mbps的 Synopsys DesignWare® DDR4 IP的一系列新功能不但能够扩展高性能云计算系统的内存容量,而且能够提高可靠性、可存取性以及可服务性(RAS)。DDR IP支持高级错误校正码(ECC),能够校正单颗器件上的所有DRAM故障,从而在不丢失数据的情况下置换有缺陷的DIMM。此外,DDR IP支持最多16 rank的高容量DDR4 LRDIMM和DDR4 3D Stacked (DDR4-3DS) DRAM内存,相比以前的所支持的4个rank,其在不降低性能的同时将容量扩展了高达400%。该IP包括业内唯一的嵌入式校准处理器,可以在上电状态下训练系统,从而提升设计裕度和信号完整性。校准处理器也可以训练高达四种有效的运行模式,从而满足快速功耗和频率变化要求。Synopsys的DDR4控制器和PHY IP解决方案能够使云和虚拟服务器环境同时为大量客户端提供支持,并且迅速解决复杂计算问题。

美光科技(Micron Technology, Inc)计算与网络营销主管Matthias Buchner表示:"随着网络、存储和安全应用对DRAM的要求不断提高,有效接入更多内存至关重要。系统架构师利用美光的SDRAM DDR4大幅提高了其产品的可靠性、容量和性能。Synopsys的DDR4 IP在不降低性能的同时进一步扩展了可接入内存容量,使设计人员能够提高其系统的整体性能。"

DesignWare uMCTL2内存控制器和uPCTL2协议控制器支持DDR4/3和LPDDR4/3标准,并提供强大的RAS功能。该控制器带有重操作功能的DDR4命令/地址(CA)校验与写入循环冗余码校验(CRC)能够提供数据与命令/地址完整性,通过返回最近一次已知的良好状态并重试失败的命令来使系统从命令或地址错误中恢复。控制器上新型高级ECC采用改良版Reed-Solomon编码,可以修正每个字段内多达四个连续数据位,当连接系统级芯片(SOC)的单颗DRAM器件完全失效时该功能可能是必需实现的。

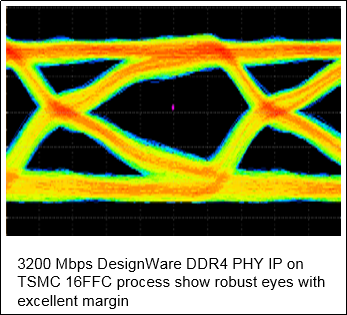

为了促进系统级优化,DesignWare DDR4/3 PHY上的新型嵌入式校准处理器可以针对IP可以捕获的每一总线比特位生成二维读写数据眼图,从而提高测试设计(DFT)的功能。至多四个有效的运行状态在引导时间进行训练,并随着电压与温度的变化得以维护。每个有效运行状态可以拥有独特的频率、均衡设置以及终端电阻设置,使主机系统级芯片能够根据功耗和频率要求更改运行模式。

Synopsys的IP和原型设计营销副总裁John Koeter表示:"内存访问已经成为高性能存储、计算以及云服务器应用方面的一项重要设计依据。通过提供高容量LRDIMM、高级ECC和嵌入式校准支持等差异化功能,Synopsys使设计人员能够在不牺牲最大工作频率的同时大幅提高自己系统的内存容量。"

可用性与资源

DesignWare uMCTL2内存控制器、DesignWare uPCTL2 协议控制器和DesignWare DDR4/3 PHY的新功能现已可用。除了这些控制器和PHY,Synopsys的完整DDR4 IP解决方案还包括IP子系统、IP原型设计套件、IP软件开发套件、验证IP以及利用DesignWare DDR Explorer和Platform Architect MCO进行的性能分析。

- Synopsys发布物联网SOC应用的DesignWare Bluetooth完整低功耗IP解决方案(09-19)

- 云计算推动,节能以太网技术将诞生(08-18)

- Netronome为中国云计算大幅提速升效降成本(05-02)

- QingCloud发布IaaS、PaaS重量级产品 推进“以应用为中心”战略(06-28)

- 众说纷“云”:云计算在存储领域的异军突起(11-22)

- IBM在爱尔兰开设欧洲首个“云计算中心”(02-20)