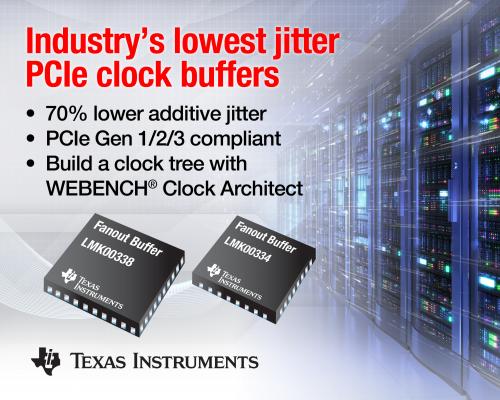

TI推出业界最低抖动 PCIe 时钟缓冲器LMK00338

2014 年 3 月 13 日,北京讯 日前,德州仪器 (TI) 宣布推出两款支持 PCI Express (PCIe) 1 代、2 代以及 3 代接口标准的 4 输出及 8 输出高速电流驱动逻辑 (HCSL) 时钟扇出缓冲器。LMK00334 可为输入时钟创建 4 个缓冲副本,而 LMK00338 则可产生 8 个缓冲副本。与同类竞争器件相比,它们不仅支持锐降 70% 的附加抖动,而且还可支持显著提高的电源噪声抑制,从而可在 PCIe 3.0 规范下为系统设计人员提供足够的抖动容限。这两款器件在 TI 最新 WEBENCH® 时钟架构的支持下,有助于为高速通信、网络以及数据中心系统简化时钟树设计,充分满足服务器、交换机以及路由器等应用需求。

LMK00334 与 LMK00338 的主要特性与优势:

• 业界最低的附加抖动:100 MHz (PCIe 3.0) 下 30 fs、12KHz 至 20 MHz (HCSL 156.25 MHz) 下 86fs,设计人员能够更加高度灵活地针对整个链路进行定时预算分配;

• 优异的噪声抑制:100MHz 下 -75dBc 的高电源抑制比 (PSRR) 可提供比同类竞争器件更好的抖动性能及噪声抗扰度,实现稳健的信号完整性;

• 高度灵活的通用输入端:2 组通用输入工作频率高达 400 MHz,并兼容于任何输入类型,包括 CML、LVPECL、LVDS、SSTL、HSTL、HCSL 或单端时钟及晶体振荡器;

• 简单易用:引脚模式控制有助于系统设计人员便捷地开关单个输出组。

LMK00334 及 LMK00338 能够与CDCM9102 及 CDCM6208 PCIe 时钟发生器相结合,创建高性能时钟树解决方案。TI 时钟分配及扇出缓冲器可为时钟树设计人员提供支持各种通信、网络、工业及消费类应用所需的高灵活性、高性能以及各种高级特性。

工具与支持

工程师可通过使用 TI WEBENCH® 时钟架构工具加速 LMK00334 与 LMK00338 的时钟树设计。它是业界首款定时设计工具,可通过详尽的器件数据库推荐和仿真系统时钟树解决方案。它不仅支持锁相环 (PLL) 滤波器设计,而且还能够仿真输出时钟的相位噪声。此外,该工具还能够实现对完整时钟树端对端抖动性能的仿真。

LMK00334 与 LMK00338 都可采用 LMK00338 评估板 (EVM) 来验证功能及性能规范。此外,TI 还为 LMK00334 与 LMK00338 提供有 IBIS 仿真模型。

德州仪器在线技术支持社区www.deyisupport.com可为工程师提供更多的技术支持,在这里他们能够与同行工程师及 TI 专家互动交流,搜索解决方案、获得帮助、共享知识并帮助解决技术难题。

供货情况与封装

采用 5 毫米 × 5 毫米、32 引脚 WQFN 封装的 LMK00334 现已开始供货,同步供货的还有采用 6 毫米 × 6 毫米、40 引脚 WQFN 封装的 LMK00338。

- 德州仪器最新ZigBee无线网络处理器简化产品设计(03-25)

- 德州仪器推出集成D类放大器的新型低功耗音频编解码器(01-06)

- 德州仪器携手Virtual Extension打造低成本能源管理解决方案(05-16)

- 德州仪器推出首款隔离式 CAN 收发器(06-17)

- 德州仪器推出业界最低功耗的全新6核高性能处理器(10-06)

- 风河推出商用级Android平台(11-10)