赛普拉斯率先向市场推出采用 65 纳米工艺技术的 SRAM

时间:04-02

来源:与非网

点击:

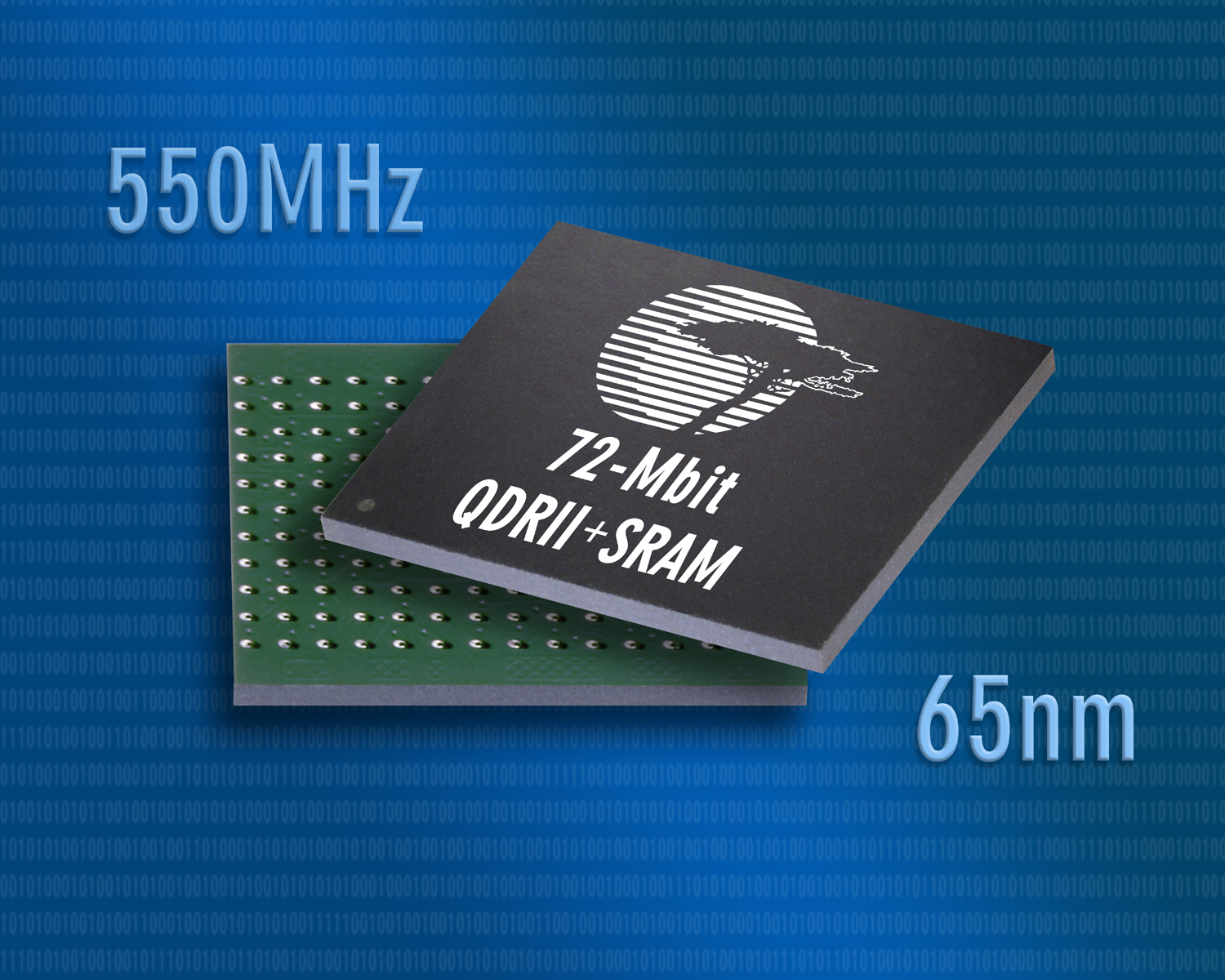

赛普拉斯(NYSE: CY)-SRAM 领域的业界领先公司,日前宣布,该公司在业界率先推出采用 65 纳米线宽的 Quad Data Rate™ (QDR™) 和 Double Data Rate (DDR) SRAM 器件样品。新推出的 72-Mbit QDRII、QDRII+、DDRII 和 DDRII+ 存储器采用了赛普拉斯合作伙伴制造商 UMC 开发的工艺技术。新型 SRAM 实现了目前市场上最快的 550 MHz时钟速度,在 36 位 I/O 宽度的 QDRII+ 器件中可实现高达 80 Gbps 的总数据传输速度,而功耗仅为 90 纳米 SRAM 的一半。这种新型存储器非常适用于因特网核心与边缘路由器、固定与模块化以太网交换机、3G 基站和安全路由器等网络应用,而且还能提高医疗影像和军用信号处理系统的性能。上述产品可与 90 纳米 SRAM 引脚兼容,从而帮助网络客户提高性能、增加端口密度,而且还不必改变原有的板卡布局。

相对于 90 纳米的上一代产品,65 纳米的 QDR 和 DDR SRAM 能将输入输出电容降低 60%。QDRII+ 和 DDRII+ 器件具有片内终结电阻器 (ODT),消除了外部端需接电阻的要求,因而可提高信号的完整性,降低系统成本,节约板上空间。65 纳米产品采用的是锁相环路 (PLL) 而非延迟锁相环 (DLL) 技术,其可使数据有效窗口扩展 35%,以帮助客户缩短开发时间、节约开发成本。

赛普拉斯存储器和影像部门的执行副总裁 Dana Nazarian 指出:"我们不断丰富自身的同步 SRAM 产品系列,以期拓展目标市场,扩大市场份额。赛普拉斯致力于推动 SRAM 市场的长期发展,并不断巩固我们的领先地位。"

供货情况和图片

65 纳米的 QDRII、QDRII+、DDRII 和 DDRII+ SRAM 目前已经推出样品,预计将于 2009 年第三季度实现量产。上述每款产品均提供不同 I/O 宽度(x18 或 x36)、突发长度(B4 或 B2)和延迟(1.5、2.0 或 2.5)的多种配置标准。65 纳米的 72-Mbit SRAM 采用标准的 165 引脚微间距球栅阵列 (FBGA) 封装,为便于技术移植,其可与现有的 90纳米 QDR和 DDR 器件引脚兼容。如欲查看 QDRII+ SRAM 的高分辨率图片,敬请访问以下网址:www.cypress.com/go/pr/65nmQDRSRAMphoto。

关于赛普拉斯

赛普拉斯公司能够为客户提供高性能、可编程的混合信号解决方案,以实现产品的快速上市和系统的出众价值。赛普拉斯的产品包括 PSoC® 可编程片上系统、USB 控制器、通用可编程时钟和内存。此外,公司还提供从 CyFi™ 低功耗 RF 解决方案到 West Bridge® 和 EZ-USB® FX2LP 控制器等多种有线和无线连接技术,以增强多媒体手机的连通性和性能。赛普拉斯服务于诸多市场领域,包括消费电子、计算、数据通信、汽车和工业等。赛普拉斯在纽约证券交易所上市,股票代码为 CY。更多信息,请访问赛普拉斯网站www.cypress.com。

相对于 90 纳米的上一代产品,65 纳米的 QDR 和 DDR SRAM 能将输入输出电容降低 60%。QDRII+ 和 DDRII+ 器件具有片内终结电阻器 (ODT),消除了外部端需接电阻的要求,因而可提高信号的完整性,降低系统成本,节约板上空间。65 纳米产品采用的是锁相环路 (PLL) 而非延迟锁相环 (DLL) 技术,其可使数据有效窗口扩展 35%,以帮助客户缩短开发时间、节约开发成本。

赛普拉斯存储器和影像部门的执行副总裁 Dana Nazarian 指出:"我们不断丰富自身的同步 SRAM 产品系列,以期拓展目标市场,扩大市场份额。赛普拉斯致力于推动 SRAM 市场的长期发展,并不断巩固我们的领先地位。"

供货情况和图片

65 纳米的 QDRII、QDRII+、DDRII 和 DDRII+ SRAM 目前已经推出样品,预计将于 2009 年第三季度实现量产。上述每款产品均提供不同 I/O 宽度(x18 或 x36)、突发长度(B4 或 B2)和延迟(1.5、2.0 或 2.5)的多种配置标准。65 纳米的 72-Mbit SRAM 采用标准的 165 引脚微间距球栅阵列 (FBGA) 封装,为便于技术移植,其可与现有的 90纳米 QDR和 DDR 器件引脚兼容。如欲查看 QDRII+ SRAM 的高分辨率图片,敬请访问以下网址:www.cypress.com/go/pr/65nmQDRSRAMphoto。

关于赛普拉斯

赛普拉斯公司能够为客户提供高性能、可编程的混合信号解决方案,以实现产品的快速上市和系统的出众价值。赛普拉斯的产品包括 PSoC® 可编程片上系统、USB 控制器、通用可编程时钟和内存。此外,公司还提供从 CyFi™ 低功耗 RF 解决方案到 West Bridge® 和 EZ-USB® FX2LP 控制器等多种有线和无线连接技术,以增强多媒体手机的连通性和性能。赛普拉斯服务于诸多市场领域,包括消费电子、计算、数据通信、汽车和工业等。赛普拉斯在纽约证券交易所上市,股票代码为 CY。更多信息,请访问赛普拉斯网站www.cypress.com。

- 瑞萨推出路由器和交换机使用的高速SRAM产品(06-20)

- Ramtron推出8-Mb并口非易失性F-RAM存储器(06-21)

- 赛普拉斯推出具有集成实时时钟功能的新串行产品系列(09-26)

- 赛普拉斯推出首款65纳米144-Mbit SRAM(09-28)

- 65纳米144-Mbit SRAM(赛普拉斯)(09-29)

- Marvell推出开创性基于SRAM网络搜索引擎Questflo(09-21)