借力大小核设计架构 多核处理器强效又省电

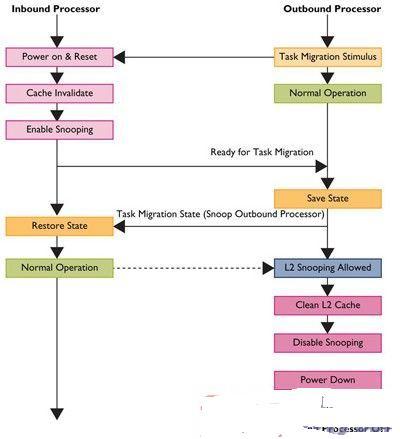

图3big.LITTLE运算任务切换流程图

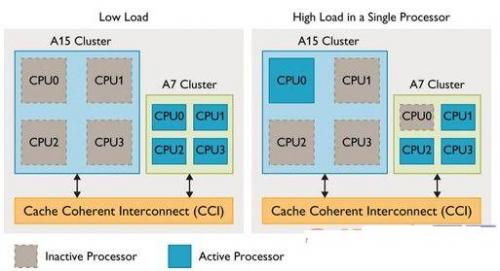

由于LITTLE处理器丛集中,每个处理器都将对应一个big丛集的处理器,因此CPU乃成对配置(Cortex-A15及Cortex-A7处理器上都有CPU0,Cortex-A15及Cortex-A7处理器上都有CPU1,以此类推),不论何时每个配对中只有一个处理器可运转;而系统则会主动侦测各处理器负载,在高负载时将内容执行移到大核心(图4)。当负载从离埠核心移到入埠核心,便会关闭其中一个核心,这种模式让big与LITTLE核心组合能随时运转。

图4big.LITTLE系统CPU切换示意图

[@B]big.LITTLEMP支援非对称丛集运作[@C]big.LITTLEMP支援非对称丛集运作

至于big.LITTLEMP模式则进一步将软体堆叠分配到两个丛集中各个处理器,如此一来,所有CPU皆可同时运作,将系统效能提升到最高点。

由于big.LITTLE系统可经由CCI-400达到快取记忆体的一致性,因此有另一种模式能让Cortex-A15及Cortex-A7处理器同时运作并同步执行程式码,称为big.LITTLEMP,基本上可看作一种异质性多工处理模型。这是big.LITTLE系统最先进且最具弹性的模式,能跨越两个丛集调整单一执行环境。

在这种使用模式下,若执行绪有上述处理效能方面的需求,便可开启Cortex-A15处理器核心并同时透过Cortex-A7处理器核心执行任务。如果没有这方面需求,则只须开启Cortex-A7处理器,在实际应用上,不同丛集的处理器核心不一定一致,而big.LITTLEMP比较容易支援非对称的丛集。

改善低频运算多余功耗big.LITTLE备受瞩目

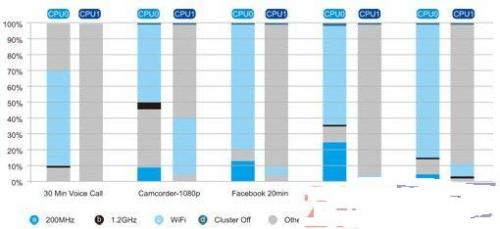

big.LITTLE技术之所以受到IC设计业者瞩目,原因就是一般行动工作量对效能的需求各有不同,必须找到最合适的核心处理。图5显示的是目前搭载Cortex-A9的行动装置中,两个核心在DVFS、闲置与完全关机状态下所花费时间的百分比,(a)处代表最低频率操作点;(b)处则代表最高频率操作点,介于两者之间则属中级频率。

图5低密度使用案例的DVFS驻留时间

除DVFS状态之外,作业系统电源管理也会使中央处理器闲置,图中(c)处代表闲置时间,当CPU闲置的时间够长,系统电源控制软体将完全关闭其中一个核心以节省耗电,图中(d)处便代表这部分。

从图5可清楚看出应用程式处理器在好几种普通工作量下,都有相当多时间处于低频率状态,在big.LITTLE系统里,系统单晶片(SoC)可利用耗能较低的Cortex-A7核心,执行最高操作频率以外的所有工作。以相同方式分析更为密集的工作量,Cortex-A7处理器对应出低于1GHz频率的机会仍然很大。

事实上,自2011年起,使用者层级软体已能在big.LITTLE排程上运转,不过,那只是在处理器核心与互联的软体模型环境上发展。为完整评估big.LITTLE系统效能、功耗及调校是否合宜,还须打造一个能让使用者软体全速运转的测试晶片。

ARM测试晶片早在2012年初夏即由晶圆代工厂完成,并在短短几周内开始搭配参考设计板运转,支援完整版的Linux系统及Android4.0作业系统。这个测试晶片包含一个双核心Cortex-A15丛集、一个三核心Cortex-A7丛集,以及CCI-400快取一致汇流排架构。会影响部分使用者评效基准的绘图处理器并不包括在内,但平台仍可支援Linux、Android作业系统与效能测试软体。

测试晶片的Cortex-A15最高频率达1.2GHz,Cortex-A7则为1GHz.效能评析结果显示,虽然测试晶片上的记忆体系统效能不如big.LITTLESoC量产后的预测水准,但Cortex-A15与Cortex-A7中央处理器的效能仍落在预期范围内。

用来测试big.LITTLE效能的任务量,主要基于Android4.0系统,透过网页进行网路浏览器效能循环,背景则有音效播放。在此实例中均以相当密集的工作量搭配对性能需求不高的背景活动,网路浏览器每2秒便进行网页循环,每页卷动达500画素,因此对系统效能需求相对较高。

这组结论属于较早期的测试结果,用来测试初版big.LITTLEMP修正程式组,将Linux排程程式从一个完整而平衡的排程模式调整成big.LITTLE模式。预期未来在更多业者投入软体修正后,效能与能耗将更进一步改善,而其他可调校的部分也将有相关解决方案被提出。

另外,测试晶片缺少GPU,使CPU的负载高过搭载GPU系统在卸载状态下的负载水准,而在CPU负载较低的状况下,可能会较常使用LITTLE核心,进而达到节能目的。它包含一套基本的电压及频率操作点,但没有对单一处理器核心做独立的电源开关设计,因此big.LITTLE系统单晶片量产后测试结果可望提升。举例来说,后台任务效能便可节省超过70%能耗。

IC设计业者正全力投入big.LITTLE开发,然而,各界最常见的疑问就是应选择哪一种软体模式?目前主要是在CPU切换与big.LITTLEMP之间择一,而两种方式各有正反意见。在CPU切换方面,由于big及LITTLE核心处于搭配成对的状态,因此对称式的拓扑能顺畅运作;而big及LITTLE核心数量不同的非对称式拓扑则须额外的运转。

big.LITTLEMP模式效果更出色

由于Cortex-A7中央处理器核心体积较小,因此可使用四个LITTLE核心加上一到两个big核心,这种作法可能会具有吸引力。从正面角度来看,中央处理器切换让电源及效能的调校更为容易,可重复利用既有的作业系统电源管理程式码,代表实作将有多年的研发及测试结果做为支援。加上不必调整核心排程程式,范围比执行big.LITTLEMP模式更为简化,而软体模式也能日趋成熟。

整体而言,CPU切换是一种极佳解决方案,相关IC设计业者亦正研拟升级至big.LITTLEMP模式,以提供更多元的处理器运算解决方案。big.LITTLEMP具有多项技术优势,虽技术尚未完全成熟,但目前的测试结果已相当不错。由于此模式也支援非对称式拓扑,故毋须调整软体即可完全利用系统中所有核心,对提升晶片效能并降低功耗更有利。

举例来说,big.LITTLEMP能同步利用所有核心在短时间内达到最高效能,或将big与LITTLE核心上的DVFS设定与排程程式设定调成不同状态,以节省更多电力。不过弹性提升仍有其代价,晶片商与系统业者均须增加调校动作,才能从big.LITTLEMP平台获取完整的效能及能耗优势。

大小核 多核处理器 big LITTLE ARM 相关文章:

- 借力big.LITTLE设计架构 多核处理器强效又省电(11-19)

- 2014年芯片处理器热点趋势(11-24)

- 多核处理器构架的高速JPEG解码算法(02-07)

- 多核嵌入式处理技术推动汽车技术发展(11-18)

- 多核处理器的九大关键技术(03-02)

- 多核处理器设计的九大关键问题(03-16)