iEthernet W5200数据手册(版本1.2.4)之:引脚分配

时间:09-18

来源:3721RD

点击:

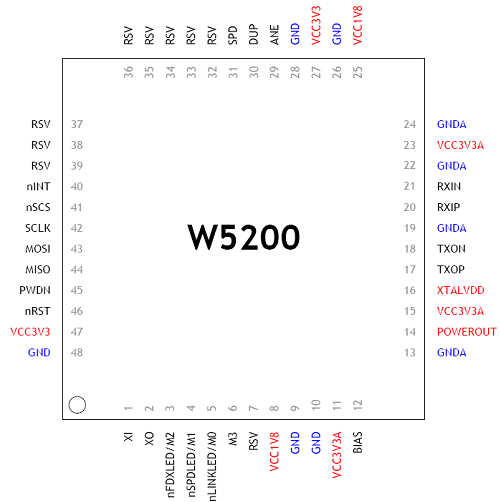

1.引脚分配

图 1

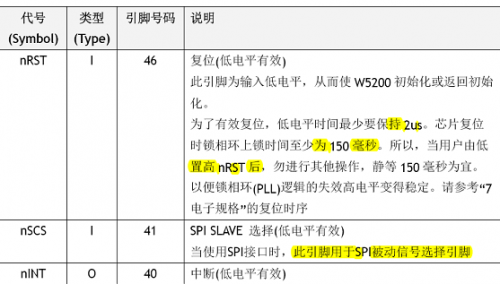

1.1 微控制器(MCU)接口信号

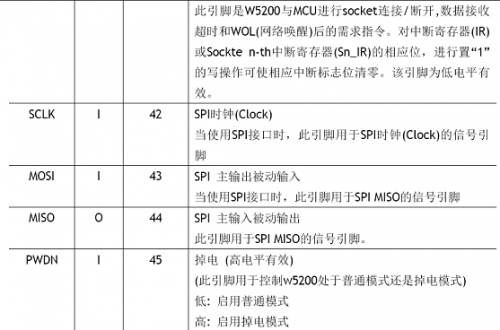

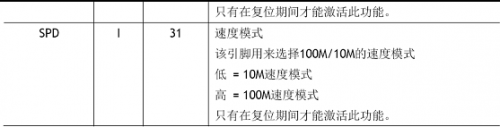

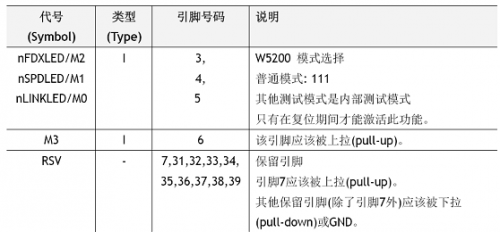

1.2 物理层(PHY)信号

1.3 综合信号

l 注意: 上拉/下拉电阻 = 40KΩ 到 100KΩ。平常的值为75KΩ.

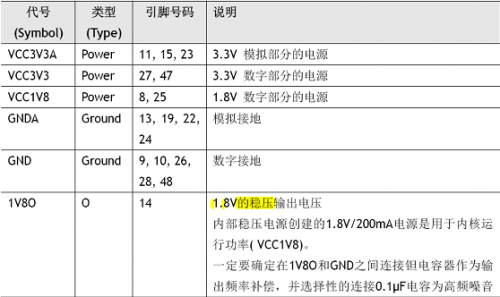

1.4 电源信号

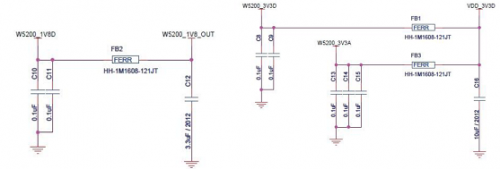

图 3 电源设计

推荐的电源设计:

1. 去耦电容尽可能靠近W5200。

2. 尽可能保证地线层足够宽。

3. 如果地线层宽度足够,具有独立的模拟地线层和数字地线层是很好的做法。

4. 如果地线层不够宽,那么只能将模拟和数字地线层设计为一个单一的地线层,而不是将它们分开。

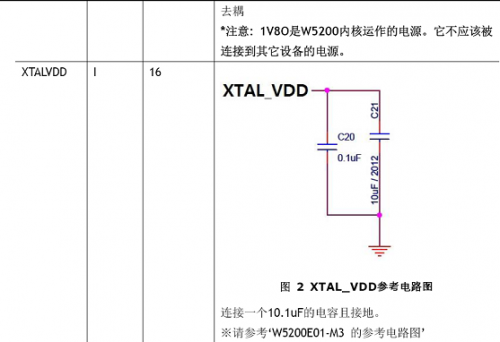

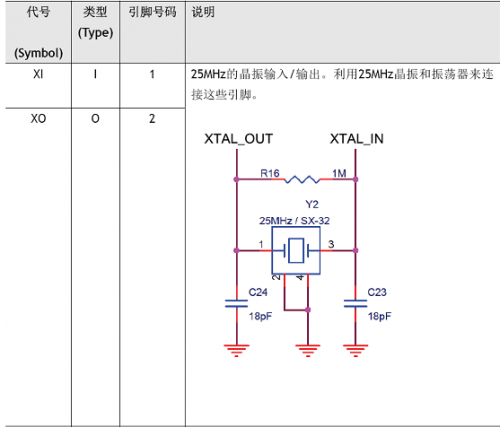

1.5 时钟信号

图 4 晶振体参考原理图

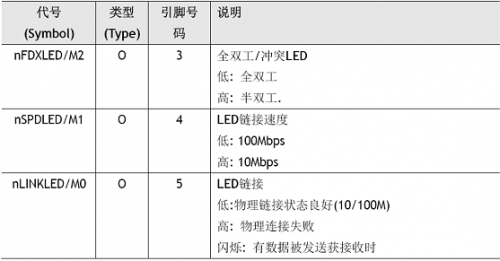

1.6 LED 信号

- iEthernet W5200数据手册(版本1.2.4)之:寄存器说明(09-18)

- iEthernet W5200数据手册(版本1.2.4)之:外部接口(09-18)

- iEthernet W5200数据手册(版本1.2.4)之:电器规格(09-18)

- ARM硬件设计一:电源和时钟 (02-27)

- 单端反激开关电源原理与设计(06-30)

- 89C51单片机为控制核心的开关电源优化设计(11-04)