视频信号采集与图象传输技术的研究----基于 EPP 的视频信号采集系统的设计

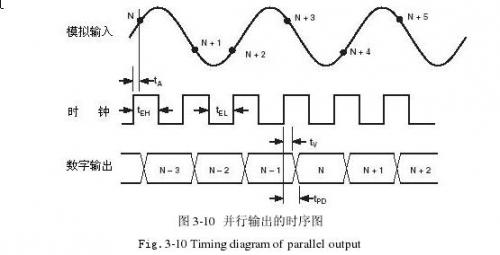

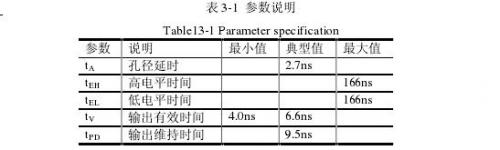

果可以并行输出,非常容易和微处理器或DSP(数字信号处理器)接口。AD9057的并行输出时序如图3-10所示,图中各个参数的说明如表3-1.在上升沿,采样保持器进入保持状态,并开始A/D转换,经过孔径时间t A =2.7ns,数据端开始输出数据。经过一个t EH的时间间隔后(t EH =166ns),采样结束。在低电平时,即一个t EL的时间间隔(t EL =166ns),A/D转换器处于保持状态。经过一个时钟周期即t EL +t EH后,一个转换周期结束。当下一个上升沿到来时,

开始下次采样,也就是转换一结束就开始下次采样。由图3-10可看出在AD9057中有四个速率位10MSPS的A/D转换器同时工作,当第一个A/D转换器开始转换的时候,此时第四个A/D转换器刚好转换完成,输出第四个的转换结果,以此类推,这样形成了AD9057的40MSPS的转换速率。

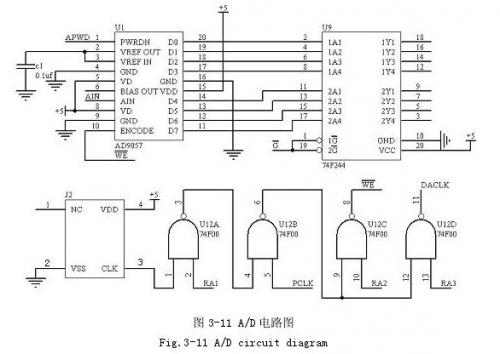

图3-11所示为AD9057用于CCD图象采集系统的电路图。目的是把CCD读出的模拟信号(单极性)转换为8位数字信号,以便微机能够进行处理,该电路采用的是并行输出模式。

2. 1. 4存储器存储单元采用一片CYPRESS的静态存储器(SRAM)芯片CY7C1049B,CY7C1049B是一种高性能的CMOS静态存储器,其存储容量为512K×8Bit. CY7C1049B具有以下特点:

(1)高速:tAA =12ns,tAA为从地址有效到数据有效之间的时间间隔,

(2)低的激活功率(最大1320mW),

(3)低的CMOS备用电源(2.75mW),

(4)2V数据保持功能,

(5)具有自动关断电源的功能,

(6)输入输出与TTL电平兼容,

(7)用CE和OE可简单的实现存储器扩展。

这些特点使CY7C1049B适用于高带宽图形、数字信号处理系统、高性能计算机系统及其外围电路等方面的应用。

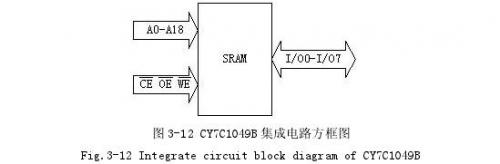

CY7C1049B是一种典型的静态存储器,静态存储器的集成电路方框图如图3-12所示。

CY7C1049B存储、读、写的时序说明如下:

CY7C1049B上的地址总线是由A0~A18组成。无论是读还是写SRAM,该电路的芯片允许信号必须有效。正像ROM一样,这是通过转变SRAM的片选信号到逻辑电平0来实现的。由于数据总线I/O0~I/O7是双向的。这就是说,当写数据到SRAM时,它们将作为输入;而当从SRAM中读取数据时,它们将作为输出。

通过设置一个新的控制信号--写允许(WE)输入信号,可以决定数据线将如何操作。在对SRAM中的存储单元进行写操作时,相应的写输入信号必须变为逻辑0电平,这就是将数据线配置为输入;相反,如果要从一个存储单元读取数据,则写信号(WE)应为逻辑1电平。当从SRAM读取数据时,输出允许(OE)信号必须有效,通过在OE这个输入端上施加逻辑0信号,将使该电路处于非高阻态的输出方式。

利用此芯片的原因是视频图像不能实时地送到计算机里去,其主要的原因在于快速的视频图像数据流和计算机慢速的数据传输之间的矛盾,于是很自然地想到设立一个缓存,先把视频图像存入缓存,再慢慢地把缓存的数据送入计算机。

2. 1. 5时钟电路及存储器地址的产生本系统中采用的时钟器件是无需外围电路的四个引脚的8MHz的晶振,时钟电路由一个8MHz的晶振和两片74F00构成。时钟电路有三个作用,为A/D转换器、D/A转换器以及计数器提供时钟;产生SRAM的地址(地址也可由主机程序产生);存入视频信号,并且可为系统中的其它芯片产生控制信号。存储器地址A0-A18分别和5片74F193计数器级联成的电路相连接。由于视频采集系统需要很高的速度,考虑到8MHz时钟的频率比较高,这里计数器宜选用同步计数器,因为同步计数器中各个时钟触发器的时钟信号都是输入计数脉冲,而异步计数器的各个时钟触发器,有的触发器其时钟信号是输入计数脉冲,有的触发器其时钟信号则是其它触发器的输出。所以同步计数器比异步计数器工作频率比较高,传输延迟时间短,两者需要同样多的宏单元而同步计数器有较快的时钟到输出的时间。74F193具有这些特点且无需外电路就能级联,分别把BO和CO接到后一级的CP D和CP U即可,所以选用了74F193 [24][25][26]。

系统的存储部分主要由存储器(CY7C1049B)、暂存器(74F244)、多路选通器(74LS257)、计数器(74LS193)和8MHz的晶振组成。系统把A/D转换器送来的数字视频信号送入CY7C1049B中存储。由5片计数器对其进行编址。由于视频采集系每幅图象采集512行,每行采集512个点,而存储器容量为512k,可存储1024行,1片CY7C1049B可以存储两幅完整的图象。

编址方法为:采用5片计数器级联,对时钟进行计数,将其输出与CY7C1049B相连,来完成对CY7C1049B的编址。

时钟、AD9057、计数器、CY7C1049B的时序配合过程为:单片机发出指令,时钟开始工作,输出的是8MHZ的高低电平。此时,A/D转换器接通,每当上升沿到来时,A/D开始工作,视频模拟信号经A/D转换器转换为数字信号。而当下降沿到来时,存储器片选有效,数据存入存储器。如果上升沿打开存储器,从A/D转换器输出的数据还不稳定,所以,采用下降沿开始存储。由计算机来发出指令,控制CY7C1049B的读写。而当计算机发出指令从存储器里读数据的同时,计算机发出指令使A/D转换器停止工作。此时,74F244输出为高阻态。以免因A/D转换器的数据输出端有数据而使采集来的数据不准确[27][28]。