如何设计可靠的电力线通信

使数据包被成功地收到,我们也需要检查其是否受到噪声破坏。这就是循环冗余检查(CRC)发挥的作用。CRC使得接收机可以侦测到收到的任何错误的数据包。当检测到一个错误的数据包时,接收机可以选择要么请求发射机重发数据包或不发出承认确认(结果是触发发射机自动发出数据包重试)。 自适应增益控制:为了克服连续噪声的影响,一些电力线通信设备可以实现自适应增益控制(AGC)。利用AGC,接收机可以在噪声平面动态调整灵敏度,所以它能更好的区分噪声和数据。

很明显,一个系统里调解或克服噪声的方法越多,那么这个系统就越可靠。具备双向通讯的确认机制,同时还有重试和CRC,对噪声控制会更有利。

电力线网络阻抗

电力线上的信号阻抗会影响信号功率,可以由发射机传输到电力线。此阻抗依赖于电力线和连接到电力线的节点/设备的阻抗。每次设备或节点插进电源插座时电力线阻抗都会发生变化。当电力线信号阻抗和发射机电路匹配时,传输的信号功率最大。这两个阻抗相差越大,传输信号功率越小,因而,电力线通信性能会更差。

这种阻抗动态变化是在电力线通讯中最棘手的问题之一。如果想要达到的电力信号性能的鲁棒性,那么电力线通信的发射机和接收机需要事先设计能预测这些阻抗的变化。发射机的不断地和电力线匹配阻抗,可以使信号最大化传输,同时接收机高阻抗可以确保接收端信号丢失最少。

网络协议

一个良好的鲁棒性和无差错的网络协议可能对电力线通信的可靠性有最大的影响。系统设计很少有不受物理因素控制的,如噪声和电力线阻抗,最优化电力线通信网络协议的实施可显著提高PLC的性能。网络协议可以使PLC系统成功或失败,使用正确的网络协议,有可能达到100%成功的电力线通信。

考虑到大多数电力线通信应用支持同一电力线上有数十到数百节点连接,网络协议对节点间的数据包进行判断,这样所有节点可以公平地共享线上可用带宽,没有一个节点可以独占通信通道。网络协议的定义和实施也确定了可以在同一条线上通讯的PLC节点最大数量。这篇文章所讨论的噪声章节,其大部分技术中可以用网络协议实现,例如,确认、重试、CRC。跑在PLC系统上的程序实现方式,不必担心其技术实现。从应用程序来看,软件只会收到有效的电力线通信数据。一些电力线通信设备内置了网络协议,而另一些则要求开发人员定义、写代码、并进行管理。如果协议不能在PLC设备本身运行,开发人员需要考虑指定另一个处理器来运行协议。

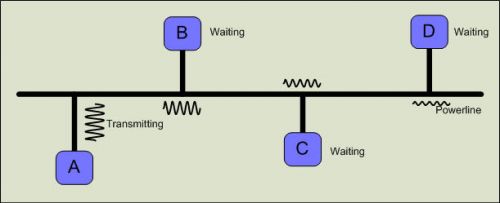

另一个重要的方面就是互操作性和共处。CENELEC委员会的载波侦听多路访问(CSMA) (见图4)确保了一套电力线通信节点可以与其他厂商的共存。PLC设备以令人难以置信的速度增长,这是保证PLC设备部署面向未来的一个重要方式。

图4:多个PLC节点共享同一条电力线

CENELEC委员会的载波侦听多路访问(CSMA)方法确保了多个节电可以在同一条电力线共存并有效的共享访问。

接收机(Rx)灵敏度

根据电力线的特点、负载、和通过电力线的分段长度,信号在接收机接收之前会明显减弱。有较高接收灵敏度的接收机 (也就是说,它可以可靠地接收到非常低强度的信号)可以从线上收到较低强度的信号,从而可以增加有效的通讯距离。然而,高灵敏度并不总是好的。例如,一个高灵敏度的接收机,不仅能检测到小信号,它也能检测到通道中的小噪声。因此,重要的是,需要有一个机制可以有效的防止接收机把噪声混淆为实际信号。自适应增益控制(AGC)就是可以达到这个目的一种机制。就象之前讨论的,使用自适应增益控制,接收机可以在噪声平面动态调整灵敏度,这样它就可以更好的区分噪声和数据。

多个相位

大多数的建筑物有50Hz / 60 Hz变压器产生的多个相位。因为大多数PLC信号工作在较高的频率,所以有一种可能,就是信号会被变压器过滤掉,因而无法传输到相邻的相位。相邻相位很可能就在同一幢房子里。这就产生了一个潜在的问题,PLC信号不能到达房子或建筑物的所有相位。这是完全依赖于变压器的设计。解决这个问题的办法是,把PLC信号从一个相位耦合到到另一个。有两种大家都了解的技术可以做到这一点:

1)电容式相耦合:这种技术需要在变压器端连接一个电容穿过相位, PLC信号可以通过。在这里,变压器的物理访问是必需的,在许多情况下这种方法可能不可行或性价比高。

2):无线相耦合:在这种技术中,PLC数据从一个相位传输到另一个时使用了两种射频设备-每个相位连接一个。这两个设备可以连接到相位的任何插座,只要他们都在彼此的范围。实施这一技术不需要用到变压器的物理存取。

无线耦合不会打扰到变压器,因此在大多数情

- Whirlpool 选择赛普拉斯PSoC CapSense界面为其新型洗衣机产品实施触摸感应操控(03-24)

- 加快程序执行:电气工程师的观点(07-24)

- 自由支配!不要让MCU、内核或编程语言干扰你的设计(03-06)

- MCU做不到,而PSoC可以——赛普拉斯PSoC 4可编程片上系统架构(07-03)

- PSoC Creator简化可编程器件上的软硬件协同设计(12-04)

- 串行和并行接口SRAM对比(10-26)