基于VME总线的RDC接口电路设计

编码。如果从设备电路板上需要多种类型数据传送,那么仅仅用地址来编码是不够的,必须把AM码加入到REGION编码中,因为不同的数据类型有不同的AM码。总之,对REGION编码的目的是告诉CY7C960,出现在VME总线上的地址是否落入从设备电路板地址段。

译码电路可以选择EPLD、GAL等可编程逻辑器件,设计者可以根据电路的复杂程度来确定。一般把AM码、地址线、CS[0:5]、读/写线、DBE[0:3]线等纳入可编程逻辑器件的输入端。输出端向本地电路提供片选信号及向CY7C960提供REGION码。

2.5 CY7C960的初始化配置

任何一个使用CY7C960的VME总线电路板,在每次上电或SYSRESET *有效时都必须将初始化配置文件装入CY7C960中。这个文件的内容包括工作模式、REGION码/AM码真值表、REGION码/CS(ChipSelect)输出真值表、REGION码/DBE真值表、CS及DBE输出的极性、译码延时时间等。可以使用Cypress公司提供的WinSVIC软件来生成这个文件。

CY7C960在I/O模式下,共有6个CS输出端(CS0~CS05),16个REGION(RECION0~REGION15)。通过配置,CY7C960将知道在那个RE-GION内响应何种类型的数据传送,以及驱动哪些CS。设计者可以根据电路板的复杂程度灵活使用这些CS作为外设的片选信号。

WinSVIC将按照上面配置的结果输出一个.bin文件,这就是我们所需要的初始化配置文件。这个文件由 380字节组成,一旦被装入CY7C960,电路板的功能就确定下来。

那么,怎样把文件装人CY7C960呢?可以使用一个PROM电路来实现这个功能。其原理见图3。

通过一个编程器将.bin文件烧入PROM内。CY7C960在上电或SYSRESET*有效时,把PREN*引脚驱动为低,使PROM电路使能。引脚LA[1]/PCLK端向PROM发出时钟信号,引脚LA[2]/PDATA端接收PROM发出的"串行流"。PROM发出固定长度的数据给CY7C960,CY7C960一旦检测到正确的数据数量,就把PREN*引脚驱动为高,终止PROM电路工作。从上电开始到PROM工作结束,约需380μs。这个工作周期应在VME总线的SYSRESET周期(即200 ms)内完成。如果PROM在工作过程中被意外打断,那么CY7C960将不响应任何VME总线活动。

PROM电路可以使用XILINx公司生产的XC1736,它的容量为36 228 bit。

3 RDC电路

凡采用机扫方式的雷达,都必须采集天线的角度值。我们采用旋转变压器加RDC芯片的方式来获取角度的数字量,因为这种方式所采集的角度值精度高、稳定性好、抗干扰能力强,而且解算电路相对简单。AD2S80A是AD公司生产的高性能RDC(芯片),可用于旋转变压器的数字转换。它的最高分辨率可以达到16 bit。带宽及跟踪速率等动态特性由设计者通过选择外围电路来决定。

为了实现数据的采集与处理,需把RDC与PLD电路进行接口。接口电路很简单,只要把RDC的/IN-HBIT端和/ENBABLE端与PLD的输出端相连即可。

/INHBIT端:/INHBIT信号禁止数据从可逆计数器传输到输出锁存器中,不影响AD2S80A的跟踪环运行。释放该信号,转换器会自动刷新输出锁存器。

/ENBABLE端:/ENBABLE信号决定输出数据的状态。高电平时,使输出数据引脚保持高阻状态;低电平时,把锁存器中的数据传输到引脚上,对该信号的操作不影响AD2S80A的运行。

读数据的时序如图4所示。先给/INHBIT端加低电平并保持(可以使用一个锁存器),经过600 ns以后,给/ENBABLE端加低电平读取数据,读完后,立即释放/INHBIT端,把它恢复成高电平。

4 AD2S80A与VME总线的接口

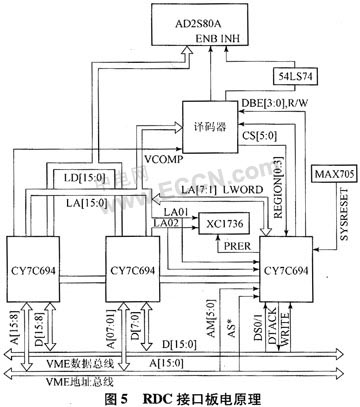

图5为RDC接口板的电原理图。因为AD2S80A是16位的,所以使用2片CY7C964、1片CY7C960。由图可以看出,对于板级设计者而言,使用CY7C960和CY7C964,只需简单地把VME总线上的控制线、数据线、地址线与它们相连接,本地I/O电路只与译码电路有关。电路板工作时,CY7C960和CY7C964首先通过PROM(XC1736)完成初始化,然后主设备发出读RDC指令,CY7C960经过比较REGION码、AM码,驱动相应的CS端为有效,译码电路根据CS、地址等信号分别驱动RDC的/INHBIT端和/ENBABLE端有效,这样就可以读到数据。

5 结束语

基于VME总线的从设备I/O板,如果使用CY7C960和CY7C964作为桥电路芯片,只要一个译码电路(PLD)及少量TTL逻辑电路就可以构成完整的接口电路,使板级设计者无需知道VME总线复杂的时序及逻辑关系就可以进行电路设计,比起使用FPGA作为接口芯片,大大节省了设计周期,降低了设计难度。CY7C960和CY7C964体积小,价格便宜,非常适合工程应用。使用这种技术的电路板已经在若干个机载雷达项目中运用,得到比较好的效果。

- 基于MSP430系列单片机的CAN总线接口转换卡设计(01-17)

- 各种通讯总线介绍(01-18)

- I2C总线原理及应用实例 (01-18)

- I2C总线在多机通信中的应用(01-17)

- 基于SPI总线的电能计量芯片ATT7022及其在配电监测终端的应用(01-18)

- CAN总线—PROFIBUS-DP总线网关的实现方法(01-17)