基于FPGA的嵌入式系统设计

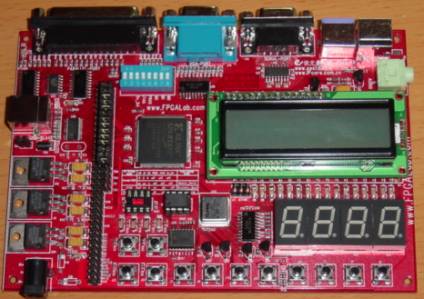

图1(a) 数字刀剑®系列之火龙刀

图1(b) 数字刀剑®系列FPGA评估板结构框图

3 基于Xilinx FPGA的嵌入式系统设计

3.1 FPGA基本开发流程与开发工具

FPGA基本开发流程主要包括设计输入(Design Entry);设计仿真(Simulation);设计综合(Synthesize);布局布线(Place & Route);配置(Configuration)五个主要步骤。

设计输入主要有原理图输入和HDL输入两种方式,一般开发商都同时支持两种输入方式。有些熟悉硬件设计的工程师开始喜欢利用原理图进行设计,这种方法非常直观,但基于可移植性和规范化方面的考虑,绝大部分深入FPGA设计和ASIC设计的工程师最终都将统一到HDL平台上来。

设计仿真包含功能仿真和时序仿真两项主要内容,功能仿真忽略了综合和布局布线导致的时延等因素,仅仅从逻辑上进行仿真,这对设计思路的验证是有帮助的,但必须通过时序仿真作进一步验证,发现并修正时序问题。

设计综合将HDL语言生成用于布局布线的网表和相应的约束。综合效果直接导致设计的性能和逻辑门的利用效率,因此,许多可编程逻辑器件开发商都 支持第三方综合和仿真工具,著名的有:Synplicity、Synopsys和ModelSim等。

布局布线工具利用综合生成的网表,在FPGA内部进行布局布线,并生成可用于配置的比特流文件。布局布线工具与可编程逻辑器件工艺及其布线资源密切相关,一般由可编程逻辑器件开发商直接提供。

随着可编程逻辑器件容量的不断增大和设计性能要求的不断提高,对传统的FPGA开发工具提出了挑战。以Xilinx公司为例,应IP Core开发和集成的需要,开发了IP Core使用工具Core Generator和IP Core包装工具IP Capture;提供了模块化设计工具Modular Design用于超大规模设计的团队项目开发;用片内逻辑分析仪ChipScope ILA进行片内逻辑调试;Xpower则用于设计功耗分析并得出相应的解决方案;还有System Generator结合Simulink甚至可以简单地实现数字信号处理模型(如FIR滤波器和FFT等)的FPGA硬件实现。此外,一些有争议的设计工具,如基于C语言的FPGA开发工具DK1等为超大容量FPGA设计和复杂逻辑设计提供了值得尝试的途径。

3.2 处理器IP Core:Micro Blaze与PPC405

将处理器IP Core嵌入到可编程逻辑器件是基于FPGA的嵌入式系统设计的前提条件,目前,国内外许多单位已成功的将51单片机、ARM和PPC等处理器内核嵌入各种可编程逻辑器件并进行了应用系统的设计,其中最著名的要数Xilinx公司的Micro Blaze和Altera公司的Nois了。Xilinx从Pico Blaze到Micro Blaze,再到PPC405,完成了从8位单片机到32位微处理器的逐步完善和性能提升。

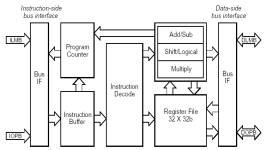

Micro Blaze 是一个专门为Xilinx FPGA优化的RISC嵌入式软处理器,符合IBM Core Connect标准,能够与PPC405系统无缝连接,Micro Blaze软处理器内核的结构如图2所示,

图2 Micro Blaze IP Core结构框图

它具备以下基本特征:

Ø 32个32bit通用寄存器

Ø 硬件乘法器(仅限Virtex II系列)

Ø 32bit地址总线和32bit数据总线

Ø 三操作数32bit指令字,两种寻址模式

Ø 独立的片内程序32bit总线和数据总线

Ø 片内总线遵循OPB(On-chip Peripheral Bus)标准

Ø 通过LMB(Local Memory Bus)访问片内Block RAM

Micro Blaze是一个非常简化,但有具有较高性能的软处理器内核,他可以在性价比很高的Spartan II(-E)系列FPGA上实现,系统时钟频率为75MHZ,仅占用400个Slice资源,相当于10万门FPGA容量的三分之一,而10万门的Spartan II系列FPGA的批量目标市场价格仅为10美元左右,非常适合消费类嵌入式产品应用需求。

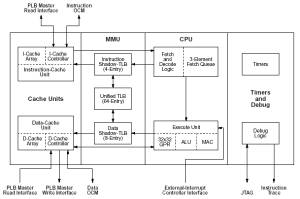

在Xilinx最新一代FPGA Virtex II Pro中,嵌入了IBM公司的PPC405 RISC结构硬处理器(如图3所示),

图3 PPC405 IP Core结构框图

该处理器内核具备以下特征:

Ø 32位、Harvard结构,300MHZ以上工作频率

Ø 支持IBM Core Connect总线标准

Ø 符合PowerPC UISA标准

Ø 低功耗:0.9mW/MHZ

Ø 硬件乘法和除法单元

Ø 32个32bit通用寄存器

Ø 16KB双端口程序缓存

Ø 16KB双端口数据缓存

Ø 内存管理单元(MMU)支持

Ø 独立的调试和跟踪接口

PPC405硬处理器内核性能上与现有的EPPC Core完全一致,含有PPC405 Core 的Virtex II Pro系列FPGA还附加了Gbit收发器和18×18硬件乘法器以及庞大的可编程逻辑资源,非常适合于通信、图像信号处理以及复杂应用系统的设计,并提供了更加灵活的设计模式。

3.3 基于Micro Blaze和PPC405 Core的SOPC软硬件开发

基于嵌入式处理器内核的SOPC系统开发是一个软硬件协同设计的过程,一方面,它极大地提高了系统设计的灵活性和快速的设计迭代周期,使整个开发过程变得更加

可控;另一方面,一些新的调试和设计问题,如逻辑分析仪和数字示波器的接入等,对调试设备和调试手段提出了更高的要求,为了尽可能避免问题的产生,要求有更好的设计工具和集成开发环境,保证IP Core资源的可用性和设计实现的一致性,让设计工程师从烦琐的内部时序调试中解放出来。

Xilinx提供了针对Micro Blaze Core应用系统开发的集成开发环境MDK,该开发环境包含了用于硬件描述和系统生成的Platform Generator、用于软件设计和编译的Micro Blaze IDE,GDB调试可通过FPGA配置JTAG接口进行,无需任何附加的调试硬件,配合Foundation ISE4.2和FPGA目标板即可进行全功能开发,MDK还包含了UART、GPIO、Watchdog、Timer/Counter、EMC和中断控制等基本处理器外设库,用户可以添加兼容OPB总线标准的任意IP Core。Insight和依元素科技均提供了功能全面的Micro Blaze Core评估工具。

PPC405 Core是一个高性能的处理器内核,它具有独立于FPGA JTAG的调试端口和更加复杂的调试功能,我们甚至可以将基于PPC405 Core的SOPC调试直观地理解为基于IBM PPC405处理器和大容量FPGA的单板机调试,只不过这个单板机无需进行传统的PCB设计和调试,设计迭代过程全部在计算机上进行。PPC405 Core的软件集成开发环境支持传统的IBM PPC405开发环境,Xilinx提供了相应的系统集成开发环境和GNU软件开发工具包支持。第三方软件开发商Wind River和Montvisa已分别宣布其VxWorks和HardHat Linux实时操作系统(RTOS)及其集成开发环境支持Virtex II Pro 系列FPGA,Insight和Avnet已开始销售含有Virtex II Pro FPGA的高端评估板。依元素科技也推出了用于开发PowerPC系列处理器的GNU集成开发工具和利刃®系列调试工具,以及含有PowerPC处理器的原型评估板。

IP Core FPGA 嵌入式 可编程逻辑器件 相关文章:

- 10大热点技术发展趋势分析(11-18)

- SIP协议简介(05-07)

- 基于51主控的lP电话设计(05-13)

- 基于Linux和S3C2410的嵌入式图象传输系统设计(05-24)

- 一种可靠的低成本嵌入式以太网接口设计(06-28)

- 嵌入式系统中TCP/IP协议的精简与实现(07-31)