嵌入式存储器的设计方法和策略

现在,要驱动500MHz的外部I/O引脚很不实际,我们设计了专用嵌入式ATE电路来俘获并评估嵌入式宏的实际存取时间。通过建立片上测试器,可确保采用低成本的数字测试器来驱动及评测芯片。 集总和加载方法是通用技术,面临分布式载荷造成的模型不精确的问题,并受到由阻容(RC)网络引起的传输线效应的影响。RC网络不仅包含阻容元件,还包含要对栅极、源极和漏极电容精确建模的晶体管。为了获得精确时序,要建立验证关键路径中所有元件与实际宏的LPE网表之间匹配程度的工具。对我们感兴趣的节点,要比较关键路径和LPE网表之间的引线、栅极、源极、漏极、耦合电容和电阻。当这些参数不匹配时,就必须修正负载模型。

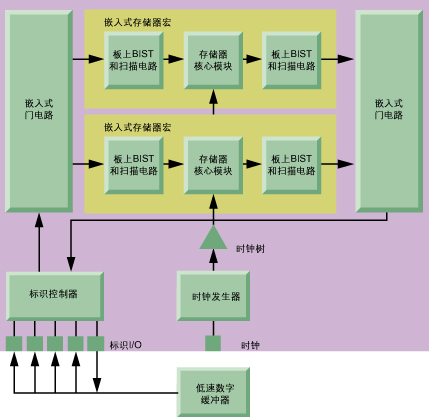

图2 验证存储器设计

时序和功能验证

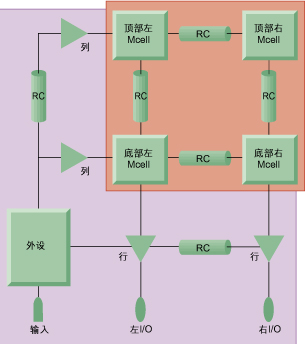

对高性能半导体芯片,精确的时序模型至关重要。为了提取嵌入式存储器中关键路径的特征并进行仿真,要采用了Avant!公司的Hspice软件。从仿真运行时间来看,仿真整个宏的LPE网表是不切实际的,为此要采用集总和加载技术(见图3)。

图3 采用集总和加载技术

Hspice可以仿真温度、P-T-V曲线并对每个角作出测量说明和绘图分析,从而便于查找不正确的电路行为,例如分析信号偏移率变差的程度、由串扰引起的信号尖峰、不期望的脉冲重叠程度、传输延迟变坏的程度、时钟电路的建立和保持时间变坏的程度等。

我们通常利用Verilog或VHDL模型来仿真整个SoC并对其建模。为了确保精确度,每个嵌入式存储器都有一个与之对应的Verilog模型,这样才能确保电路的功能与HDL模型匹配。对每个存储器,要建立全面的测试平台来测试所有的地址组合、控制和测试模式(即扫描和BIST),然后,我们将测试矢量及其相关的预测数据应用到每个宏的所有LPE网表。

如上所述,可以证明用Hspice仿真大型网表和大型测试向量集(通常有数千个向量)是不切实际的。为了弥合Hspice和Verilog之间的差距,要采用Synopsys公司的Timemill测试工具, 该工具可将逻辑等价性测试和电路的电性能验证结合起来,它可将向量驱动的全部存储器的LPE网表作为输入置于Verilog环境中进行仿真,其优点在于能检测电路网表和Verilog模型之间功能上的差异,并具有良好时序精度,从而发现时序缺陷。Timemill测试工具不是故障仿真器,但是测试向量能够涵盖99%以上的待测节点。我们在与Hspice仿真相同的P-T-V曲线下运行了Timemill测试。此外,还检测了未驱动的节点、最低和最高工作频率及P-T-V曲线的极端情形。

物理验证

我们还采用Mentor Graphics公司的Calibre工具来验证物理设计,并用完整的LVS和DRC规则基准来检验电路连接的正确性、所有的间距和宽度等,用附加的质量保证规则基准来检验浮动层、阻抗连接和不期望出现的几何结构。

对于版图的寄生参数抽取,要采用Mentor公司的xCalibre工具,它可生成用于Hspice关键路径分析和Timemill仿真的LPE网表。为了达到精确抽取,版图的层次必须与电路图的层次匹配,此外,所有的馈通(feedthrough)必须嵌入页元(leaf cell)中,这样其寄生效应才会在子电路的LPE网表中得到仿真。

LPE网表只能对关键路径仿真进行事后说明,但为了防止LPE预仿真和LPE后仿真的结果之间出现大的差异,这样做有必要。假如我们要达到高性能的仿真结果,关注实际版图的质量对电路设计技术也至关重要,例如合并或共用信号源极或漏极、屏蔽时钟信号线和解码信号线组、以及使用多个触点把电阻降到最小(在驱动大负载时,这点特别重要)。

质量保证

除了上述步骤和检验以外,在每个宏输出到系统设计工程师之前,要对其进行强化质量保证分析。目前,EDA质量保证工具正在形成之中,我们已经开发了很多专用检验工具。一级QA检验工具专用于较小面积的存储器开发,用该工具能确保Hspice关键路径网表加载与全版图LPE网表准确匹配。该工具还能分析整个LPE网表里的每个节点,并检验额外的驱动输出和偏移率,它检测到节点上的多个驱动器并找到易受电荷共享(特别是动态节点)和串扰影响的节点,然后要考虑耦合电容、驱动强度、接收器的噪声容限以及相邻节点的数量。检验之后,设计工程师必须纠正或者调整上述检验中有问题的节点。

我们采用一套特殊的DRC规则集对版图进行QA检验,该工艺找到具有阻性的连接点并检查电源格的完整性以及超宽晶体管。典型的DRC规则无法检查的阻性连接点或软连接不会导致芯片的功能故障,但容易产生与频率相关的问题或稳定性故障。

; 为了满足时序要求,设计工程师有时必须在噪声容限和速度之间作出折衷。即便如此,所有电路都必须通过最小噪声容限规则,否则当把存储器嵌入到整个CPU后,就存在故障隐患。存储器、比例逻辑(伪NMOS逻辑)和动态逻辑门等电路都要经过静态和动态噪声容限分析。对于那些在同一裸片上参数不匹配的器件(如差分传感放大器),要通过蒙特卡洛Hspice分析,最后,存储器单元和锁存器要在所有P-V-T曲线上进行可写性测试。

功率分配和电源格的完整性对宏的性能有显著影响。电压IR降到Vdd,Vss上的电位抖动对噪声容限、时序甚至电路的功能有重要影响,随着电源电压的降低和深亚微米特征尺寸Vts的减小,这个问题甚至会恶化。在0.18微米工艺中,窄线距必然电流密度高,从而增加了出现电子迁移故障的可能性。因为电流和焦耳热会造成互连线特性的逐步退化,通常在几个月或几年后就可能发生电子迁移故障,如果故障出现得太早,那么就有可能造成灾难性的损失。

采用Synopsys公司的Pow ermill(Timemill的姊妹工具)仿真整个宏的电源,能按照放置的位置详细描绘各子电路电源的电流图,该电流图和宏版图的RC网表一起,输入到分析电源总线IR压降和电子迁移的工具中,该工具将指出任何有故障的线段或触点/通孔,并允许设计工程师改进总线,同时,输出的版图错误标识图、轮廓图、3D电流和电压分布图有助于进一步分析。

事实上,不仅限于最高速和最小加工工艺,即使0.35微米以上的工艺和 100MHz以下的速度,也可以采用上述QA流程对噪声容限、串扰、IR压降或电子迁移相关的故障进行检测和分析。

- FPGA协同处理的优势(04-29)

- 如何采用FPGA协处理器实现算法加速(04-29)

- 三星ARM处理器S3C4510B的HDLC通道使用及编程 (05-03)

- Xilinx配置快速入门指南(08-03)

- WTB网络HDLC在FPGA中的实现(11-06)

- 32位单精度浮点乘法器的FPGA实现(11-25)