嵌入式多媒体处理器:选择双内核或单内核?

当单内核EMP不足时

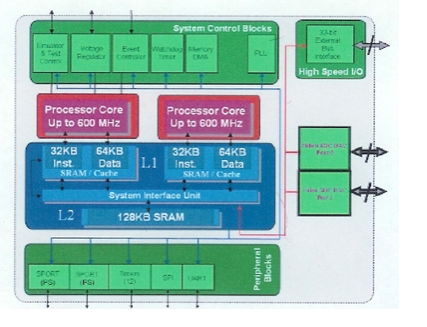

随着处理需求的不断增加,出现了这样的观点:即使一个600MHz的EMP对于某些应用来说都是不够的。这就是考虑采用双内核EMP的一个原因,例如ADSP-BF561(见图2)。

图2:双内核嵌入式媒体处理器ADSP-BF561的框图

增加另外一个处理器内核,不仅仅能将处理能力相对于单处理器的能力倍增,而且还有某些令人吃惊的结构好处,这种好处并不是立竿见影的。

传统的双内核处理器的应用采用了离散的且通常在每个内核上运行不同的任务。例如,一个内核可能执行所有的与控制相关的任务,例如图形和覆盖功能、网络连接、与大存储器的接口以及整体流控制。该内核还是操作系统或核(kernel)很可能驻留的地方。与此同时,第二个内核可能专门用于应用中的高密度处理功能。例如,压缩数据包可能通过网络接口传输到第一个内核,该内核对其进行预处理,并递交到第二个内核进行音频和视频解码。

这种模式受到采用分开的软件开发团队的开发商青睐。将这些功能类型进行划分的能力允许并行设计处理,消除项目中对关键路径依赖性。这种编程模式还对项目中的测试和验证阶段有所帮助。例如,如果一个内核上的代码发生变化,不一定会使另外一个内核上已经完成的测试工作付之东流。

对称的与非对称的多内核处理

为理解是什么让这种双内核方法令人兴奋,我们需要首先讨论"对称多处理(SMP)"。这是指一种通过高速路经相连接的两个相似(或相同)的处理器,并共享一组外设和存储器空间。它与"非对称多处理(AMP)"方法形成对比,其中结合了两颗不同的处理器,通常是在一个混合的架构中集成一个MCU和一个DSP。AMP方法的一种局限性在于,设计工程师必须对控制和DSP功能的共享部分进行"50/50"划分;例如一旦DSP"胜出",MCU将不能进行计算处理。SMP架构没有这种局限性,因为两个处理器内核是相同的,可以按照应用要求进行划分,甚至划分为100%的DSP或100%的MCU工作。此外,对称处理器还具有提供一种普通的集成设计环境的优点。只需要一组开发工具,而且针对单一开发平台培训开发团队的负担较小。

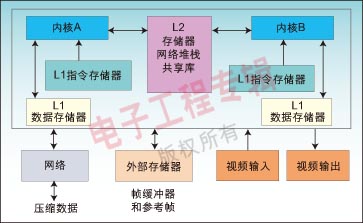

图3: BF5601就是对称多处理的很好体现

作为一种SMP友好的器件,BF561(图3)包含属于每个内核的高速L1指令和数据存储器,以及在两个内核之间的一种共享128KB L2存储器。每个内核都能同等地访问范围广阔的外设-视频端口、串行口、定时器等等。这样的安排扩展了器件的可配置性,允许其工作在几种相同的有效架构下。这些模式(见图4)可以总结性地称为"MCU/DSP分离"、"串行处理"和"分离处理"。

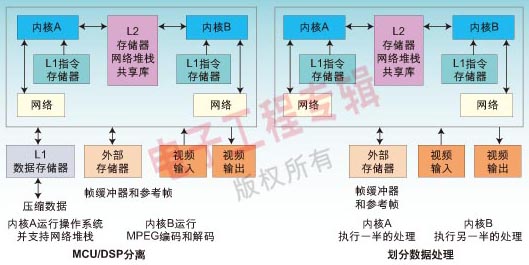

图4:双内核编程模式举例

选择合适的数据模式

"MCU/DSP分离"模式涉及到分离的以及通常运行在每个内核上的不同任务。一个内核被分配给所有的"MCU类"行为,例如图形覆盖、联网管理以及流控制。此外,如果是用了操作系统的话,该内核还支持操作系统。与此同时,第二个内核专门用于应用的高密度DSP功能。例如,压缩数据通过第一个内核从网络传递。接收到的数据包然后提供给第二个内核,该内核再进行音频和视频的处理(图4)。

这种模式非常适合那些采用分离的基于任务的团队进行软件开发的公司。拥有"控制团队"和"DSP团队"可以使开发并行实施,减少项目对关键路径的依赖性。这种编程模式还能促进设计的测试和验证阶段。例如,在一个内核上的代码改变未必使另一个内核上已经完成的测试工作变得无效。此外,拥有两个相同的内核还允许重新分配在任何内核上任何"未用"的处理带宽,以在不同的功能和任务上再分配。

在"串行处理"使用模式中,第一个内核在输入数据组上执行若干中间级控制和计算,然后传第一个中间数据流到第二个内核进行最后的处理。这种方法的一个变化方法是:将任务在每个内核上进行划分,在这种方式中,中间数据实际上在内核之间搬移几次,直到获得最后的结果。非常适合这种使用模式的算法是MPEG编码或解码。

"分离处理"模式为每个内核提供了更均衡的使用。因为在对称处理器中有两个相同的内核,传统的计算密集应用可以在每个内核之间平均划分。架构功能,像丰富的片上存储器、很宽的内部数据路径和高带宽DMA控制器都有助于基于"分离处理"的系统设计的成功。在这种模式中,运行在每个内核上的代码是相同的;只有被处理的数据不同。在一个通道流应用中,这意味着一半的通道由第一个内核处理,而另外一半由第二个内核处理。作为另外一个实例,在视频或成像应用中,可能由每个内核处理交替帧。

即使当某个应用适合某个单内核处理器,也可以利用双内核系统来降低整体的能耗。例如,如果一个应用需要600MHz的时钟速度以在一个单内核处理器(如ADSP-BF533)上运行,它还必须工作在更高的电压下(1.2V)以达到这个速度。然而,如果相同的应用在一个双内核器件(BF561)上进行划分,每个内核可以运行在大约300MHz的速度下,每个内核的电压可以极大地降低到0.8V。因为功耗与频率呈正比并与工作电压的平方成正比,电压从1.2V降低到0.8V(同时频率从600MHz降低到300MHz)能对功耗产生显著的影响,与单内核解决方案相比实际上节省了能耗。

作者:

David Katz

Rick Gentile

高级DSP应用工程师

ADI公司

多媒体 相关文章:

- 飞思卡尔嵌入式硅片为福特汽车下一代SYNC系统提供动力(01-08)

- 嵌入式系统的实时数据接口扩展(07-31)

- 一种基于MMS的低成本汽车安防系统设计与实现(09-19)

- 基于TMS320DM6446的数字电影放映系统实现方案(11-13)

- 基于CMMB的移动电视终端设计(02-03)

- West Bridge SLIM架构多媒体手机设计(03-28)