# DETAILED FREQUENCY ANALYSIS OF POWER SUPPLY REJECTION IN BROKAW BANDGAP

G. Giustolisi, G. Palumbo

DEES - Università di Catania V.le A. Doria, 6 I-95125, Catania, Italy e-mail: ggiustolisi@dees.unict.it, gpalumbo@dees.unict.it

## ABSTRACT

A detailed frequency analysis of Power Supply Rejection (*PSR*) in Brokaw bandgap voltage reference is carried out. The knowledge of the frequency behavior in a voltage reference becomes mandatory to the designer especially in RF or digital environment where disturbs coming from supply lines becomes more evident. Precise and simple models, useful for pencil and paper analysis, are developed and a compensation technique for improving the circuit frequency performance is also discussed. Results are validated by comparing the carried-out models with the actual circuit by means of SPECTRE.

#### 1. INTRODUCTION

Since its introduction, the Brokaw bandgap reference [1] (or an equivalent version [5]) has been widely used in a wide range of applications such as A/D and D/A converters, voltage regulators, measurements, instrumentation circuits, etc. The bandgap reference generates a dc voltage that is ideally temperature independent. This is achieved by adding a voltage, which is proportional to the absolute temperature (PTAT), to a baseemitter voltage in order to compensate for its first-order temperature dependency [2-3]. In the literature, performance of bandgap references has been expressed in terms of relative temperature dependency, accuracy, output impedance, power consumption, and noise [4-10]. An important parameter, such as power-supply rejection (PSR), and its frequency behavior, has not been already treated explicitly, although this feature becomes a fundamental design criterion in high performance applications (as instance, RF circuits and digital processing) [11]. Indeed, due to the reduction of the loop gain with frequency, spurious signals coming from the power supply could not be adequately rejected and this problem becomes more evident in RF or digital environment where disturbs due to coupled lines or to substrate noise arise. In these environments, a detailed knowledge of the bandgap frequency behavior is mandatory to the designer in order to better understand the possibilities and the main limitations of the used voltage reference.

In this communication, a detailed frequency analysis of the *PSR* in the Brokaw bandgap voltage reference is carried out and a simple and useful compensation technique to improve frequency performance is also given. For both the uncompensated circuit and the compensated one, two frequency models, which are in excellent agreement with simulations on the actual circuit, are carried out.

## 2. CIRCUIT ANALYSIS

### 2.1 Bandgap analysis

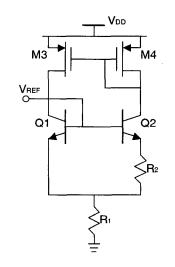

The Brokaw bandgap voltage reference is shown in Fig. 1. As well known, neglecting the base currents, the mirror sets  $I_{C1}$  equal to  $I_{C2}$ , so that the dc output voltage,  $V_{REF}$ , can be expressed by

$$V_{REF} = V_{BE1} + 2R_1 I_{C1,2}$$

(1)

Figure 1. Brokaw bandgap voltage reference.

The drop voltage across  $R_2$  sets the current  $I_{C2}$ , which is proportional to  $\Delta V_{BE1,2}$ , that is

$$I_{C1,2} = \frac{U_T}{R_2} \ln \left( \frac{A_{E2}}{A_{E1}} \right)$$

(2)

where  $A_{E1}$  and  $A_{E2}$  are the emitter areas of transistors Q1 and Q2, respectively and  $U_T$  is the thermal voltage ( $U_T \cong 26$ mV @ 27°C). Substituting (2) in (1) we get

$$V_{REF} = V_{BE1} + 2U_T \frac{R_1}{R_2} \ln\left(\frac{A_{E2}}{A_{E1}}\right)$$

(3)

#### 0-7803-6685-9/01/\$10.00©2001 IEEE

$$PSR(s) \approx \frac{r_{d3} \parallel \left(\frac{k}{2}r_{c2}\right)}{R_{1}} \cdot \frac{1 + \frac{C_{G}}{g_{m1,2}g_{m3,4}} \left(1 + \frac{1}{k}\right)s + \frac{R_{1}}{g_{m3,4}}C_{G}\left[C_{db3} + C_{cs1} + C_{\mu2}\left(1 + \frac{2}{k}\right)\right]s^{2}}{1 + \left[r_{d3} \parallel \left(\frac{2}{k}r_{c2}\right)\right]\left[2C_{\mu2} + \left(1 + \frac{2}{k}C_{cs2}\right)\right]s + \left[r_{d3} \parallel \left(\frac{2}{k}r_{c2}\right)\right]\frac{C_{G}C_{\mu2}}{g_{m3,4}}\left(1 + \frac{2}{k}\right)s^{2}}$$

(7)

A proper choice of transistor areas and of both  $R_1$  and  $R_2$  will minimize the temperature coefficient and will set the output voltage to a stable value near 1.2 V.

#### 2.2 PSR model

The PSR can be defined as

$$PSR = \frac{1}{A_{dd}} \tag{4}$$

where

$$A_{dd} = \frac{v_{ref}}{v_{dd}}$$

(5)

represents the small signal gain between the output node of the bandgap and the power supply line.

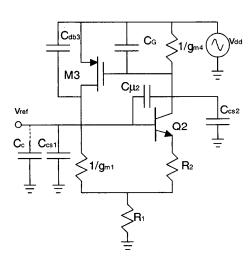

Figure 2. Small signal model of the Brokaw bandgap voltage reference.

The model used to determine the *PSR* is shown in Fig. 2. Diode connected transistors are approximated with resistors given by their transconductance. Capacitor  $C_G$  takes into account the capacitive amount between the gate of M3-M4 and the supply line and is equal to  $2C_{gs3,4} + C_{db4}$ . Capacitors  $C_{\mu1}$ ,  $C_{\pi1}$  and  $C_{gd3,4}$  can be ignored because of their small value and, despite its large value (the emitter area of Q2 is larger than Q1's, usually 8 times), capacitor  $C_{\pi2}$  can be ignored too. In fact, applying the Miller theorem to  $C_{\pi2}$  and assuming in a rough approximation

that Q2 acts as a voltage follower, its contribution can be demonstrated to be negligible.

Defining k as

$$k = g_{m1,2}R_2 = \ln\left(\frac{A_{E2}}{A_{E1}}\right)$$

(6)

a symbolic analysis yields the expression in (7) for the *PSR* where non-dominant terms have been neglected.

A fairly good approximation of poles and zeroes included in (7) can be found by evaluating the polynomial coefficient ratios [12-13], yielding

$$p_{1} = -\frac{1}{\left[r_{d3} \left\| \left(\frac{k}{2}r_{c2}\right) \right\| 2C_{\mu 2} + \left(1 + \frac{2}{k}C_{cs2}\right) \right]}$$

(8a)

$$p_{2} = -\frac{g_{m3,4}}{C_{G}} \left( \frac{2k}{k+2} + \frac{C_{cs2}}{C_{\mu2}} \right)$$

(8b)

$$z_1 = -\frac{g_{m3,4}}{C_G \left(1 + \frac{1}{k}\right)}$$

(8c)

$$z_{2} = -\frac{1 + \frac{1}{k}}{R_{1} \left[ C_{db3} + C_{cs1} + C_{\mu 2} \left( 1 + \frac{2}{k} \right) \right]}$$

(8d)

A first look at (7) shows that the *PSR* dc behavior is mainly affected by intrinsic resistances of both Q2 and M3 and by resistor  $R_1$ . This means that the dc gain mainly depends on process parameters (such as the channel length modulation factor,  $\lambda$ , in MOS or the early voltage,  $V_A$ , in BJT transistors) and is independent of the bias current,  $I_{C1,2}$ . In fact for the bandgap to work properly the voltage across  $R_1$  must be kept constant and equal to about 0.5 V, that is  $R_1$  must be chosen almost inversely proportional to  $I_{C1,2}$ . Moreover, since also both  $r_{d3}$  and  $r_{c2}$  are inversely proportional to  $I_{C1,2}$ , for typical technological parameters, a gain of no more than 40 dB can be hardly achieved.

As far as the ac behavior is concerned, from (8) we can notice that the first pole,  $p_1$ , gives the dominant contribution and depends on both  $r_{d3}$  and  $r_{c2}$  (as well as the dc gain) and on parasitic capacitors of Q2. A pole-zero cancellation is obtained between the second pole,  $p_2$ , and the first zero,  $z_1$ , since they are very close each other, while the last zero,  $z_2$ , gives its contribution at very high frequencies.

As a conclusion, in RF or in modern digital circuits where disturbs from coupling lines or from the switching activity

$$PSR(s) \cong \frac{r_{d3} \parallel \left(\frac{k}{2}r_{c2}\right)}{R_{1}} \cdot \frac{1 + R_{1}C_{c}\left(1 + \frac{1}{k}\right)s + \frac{R_{1}}{g_{m3,4}}C_{G}C_{c}\left(1 + \frac{1}{k}\right)s^{2}}{1 + \left[r_{d3} \parallel \left(\frac{2}{k}r_{c2}\right)\right]\left[2C_{\mu 2} + \left(1 + \frac{2}{k}C_{cs2}\right)\right]s + \left[r_{d3} \parallel \left(\frac{2}{k}r_{c2}\right)\right]\frac{C_{G}C_{\mu 2}}{g_{m3,4}}\left(1 + \frac{2}{k}\right)s^{2}}$$

(9)

widely affect power supply lines, this bandgap appears to have poor performance if its first pole is located in a frequency in the order of a few Megahertz.

#### 2.3 PSR model with frequency compensation

Better ac performances can be obtained by inserting a compensation capacitor,  $C_c$ , between the bandgap output and ground. In the same way, a symbolic analysis yields the expression in (9) for the *PSR* where non-dominant terms have been neglected. It is worth noting that the denominator of (9) is unchanged and so will be the poles, while numerator coefficients mainly depend on  $C_c$ . In particular, the poles are the same as in (8a) and (8b) while the new expressions for the zeroes are given by

$$z_{1} = -\frac{1}{R_{1}C_{c}\left(1 + \frac{1}{k}\right)}$$

(10a)

$$z_2^{'} = -\frac{g_{m3,4}}{C_G}$$

(10b)

A pole-zero cancellation can be obtained by choosing  $C_C$  so that  $p_1=z_1$ , that is

$$C_{c} = PSR(0) \cdot \frac{2C_{\mu 2} + C_{c s 2} \left(1 + \frac{2}{k}\right)}{1 + \frac{1}{k}}$$

(11)

In this way, we get a flat band *PSR* over a wide range of frequencies, since the main frequency limitations are given by the pole and the zero in (8b) and (10b), respectively, very close each other. A larger value of  $C_c$  would yield to an increase in the PSR for high frequency but, on the other hand, it would increase the startup time, too, when the bandgap is switched on.

### 3. VALIDATION RESULTS

The circuit was simulated and results were validated by using the SPECTRE simulator and a 0.8- $\mu$ m BiCMOS technology supplied by EUROPRACTICE. Npn transistors have a  $\beta_F$  of 90 and a maximum  $f_T$  of 8 GHz. Both n-mos and p-mos exhibit a threshold voltage of about 0.75 V and a transconductance factor of 100  $\mu$ A/V<sup>2</sup> and 36  $\mu$ A/V<sup>2</sup>, respectively.

The supply voltage was set to 3 V with a bias current of 100  $\mu$ A in each branch. Q2 emitter area was chosen 8 times Q1's. Other useful parameters are reported in Table I.

The circuit exhibit an output voltage of 1.198 V at room temperature (27 °C) and a temperature coefficient of 16.5 ppm/°C over the range -55, +125 °C. The uncompensated bandgap was compared with the *PSR* transfer function model

carried out in section 2.2. Specifically, the dc gain was carried out evaluating PSR(0) from (7) while poles and zeroes were evaluated from (8). Table II summarize the resulting transfer function model.

| TABLE I                     |

|-----------------------------|

| VALUE OF CIRCUIT PARAMETERS |

| Parameter                     | Value      |

|-------------------------------|------------|

| (W/L) <sub>3,4</sub>          | 100/4      |

| $R_1$                         | 1.93 kΩ    |

| $R_2$                         | 540 Ω      |

| Cc                            | 22.45 pF   |

| <i>g</i> <sub>m1,2</sub>      | 3.86 mA/V  |

| <i>r</i> <sub>02</sub>        | 265.1 kΩ   |

| $C_{\mu 2}$                   | 79.99 fF   |

| C <sub>cs1</sub>              | 34.65 fF   |

| C <sub>cs2</sub>              | 87.22 fF   |

| <i>g</i> <sub>m3,4</sub>      | 382.6 μA/V |

| <i>r</i> <sub><i>d</i>3</sub> | 658.76 kΩ  |

| $C_{gs3,4}$                   | 571.1 fF   |

| $C_{db3,4}$                   | 38.55 fF   |

TABLE II COEFFICIENTS OF PSR TRANSFER FUNCTION MODELS

| PSR(0)           | 40.04 dB                    |

|------------------|-----------------------------|

| Unco             | mpensated circuit           |

| $p_1$            | $-2\pi \cdot 2.47$ Mrad/s   |

| $p_2$            | $-2\pi \cdot 108.67$ Mrad/s |

| $\overline{z}_1$ | $-2\pi \cdot 34.78$ Mrad/s  |

| Z2               | -2π·533.27 Mrad/s           |

| Com              | pensated circuit            |

| $p_1$            | $-2\pi \cdot 108.67$ Mrad/s |

| 51               | $-2\pi \cdot 51.50$ Mrad/s  |

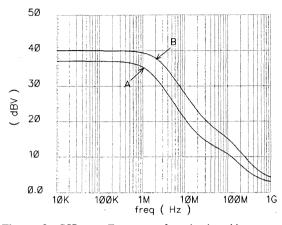

The result of the first ac simulation is reported in Fig. 3. As expected, the circuit exhibits a dc gain of about 40 dB. The error

between the actual circuit and the model is less than 3 dB while their frequency behavior matches perfectly.

Figure 3. *PSR* vs. Frequency for circuit without compensation. A) Circuit, B) Model.

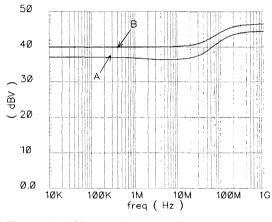

A second simulation was carried out in order to compare the compensated circuit with the model developed in section 2.3. The compensation capacitor,  $C_c$ , was chosen, according to (11), in order to obtain the pole-zero cancellation and results in 22.5 pF. The *PSR* transfer function model has the same dc gain and, due to the pole-zero cancellation, it exhibits the pole in (8b) and the zero in (10b). Their numerical values are reported in Table II.

Figure 4. *PSR* vs. Frequency for circuit with compensation. A) Circuit, B) Model.

The simulation result is depicted in Fig. 4. Even in this case, the model matches with the actual circuit that exhibit a first order transfer function as expected. This result justifies also the remark in section 2.3 which suggest not increasing the value of  $C_c$  to achieve better performances at higher frequencies. In fact, it is apparent that achieving better performance would mean having a too large value of  $C_c$  that would degrade the bandgap startup time.

#### 4. SUMMARY

In this paper the *PSR* frequency behavior of a widely used bandgap voltage reference was analyzed and a compensation technique was also carried out. Two simple models for penciland-paper analysis were given to the designer in order to estimate the *PSR* of the Brokaw bandgap at high frequencies. Both the compensation technique and models are useful in RF or modern digital circuits where disturbs from power supply becomes critical. Results were validated by comparing the models with the actual circuits and a good agreement is shown between simulated and expected results.

#### 5. REFERENCES

- A. Brokaw, "A Simple Three-terminal IC Bangap Reference," *IEEE J. of Solid-State Circuits*, Vol. SC-9, Dec. 1974, pp. 388-393.

- [2] R. Widlar, "New Developments in IC Voltage Regulators," *IEEE J. of Solid-State Circuits*, Vol. SC-6, Feb. 1971, pp.2-7.

- [3] G. Meijer, J. Verhoeff, "An Integrated Bandgap Reference," *IEEE J. of Solid-State Circuits*, Vol. SC-11, Jun. 1976, pp. 403-406.

- [4] Y. P. Tsividis, R. W. Ulmer, "A CMOS Voltage Reference," *IEEE J. of Solid-State Circuits*, Vol. SC-13, No. 6, Dec. 1978, pp. 774-778.

- [5] E. A. Vittoz, O. Neyroud, "A Low-Voltage CMOS Bandgap Reference," *IEEE J. of Solid-State Circuits*, Vol. SC-14, No. 3, Jun. 1979, 573-577.

- [6] H. J. Oguey, D. Aebischer, "CMOS Current Reference Without Resistance," *IEEE J. of Solid-State Circuits*, Vol. 32, No. 7, Jul. 1997, pp. 1132-1135.

- [7] A. Annema, "Low-Power Bandgap References Featuring DTMOST's," *IEEE J. of Solid-State Circuits*, Vol. 34, No. 7, Jul. 1999, pp. 949-955.

- [8] M. Gunawan, G. Meijer, J. Fonderie, J. Huijsing, "A Curvature-Corrected Low-Voltage Bandgap Reference," *IEEE J. of Solid-State Circuits*, Vol. 28, Jun. 1993, pp. 667-670.

- [9] I. Lee, G. Kim, W. Kim, "Exponential Curvature-Compensated BiCMOS Bandgap References," *IEEE J. of Solid-State Circuits*, Vol. 29, No.11, Nov. 1994, pp. 1396-1403.

- [10] A. van Staveren, C. Verhoeven, A. van Roermund, "The design of Low-Noise Bandgap References," *IEEE Trans. Of Circuits and Systems – part I*, Vol. 43, No. 4, Apr. 1996, pp. 290-300.

- [11] K. Tham, K. Nagaraj, "A Low Supply Voltage High PSRR Voltage Reference in CMOS Process," *IEEE J. of Solid-State Circuits*, Vol. 30, No. 5, May 1995, pp. 586-590.

- [12] P. Gray, R. Meyer, Analysis and Design of Analog Integrated Circuits (III Ed.), Wiley & Sons, 1993.

- [13] J. Millman, A. Grabel, *Microelectronics (II Ed.)*, McGraw-Hill, 1987.