# Gate-Resistance-Limited Switching Frequencies of Power MOSFET's

KRISHNA SHENAI, SENIOR MEMBER, IEEE

Abstract—High-frequency switching limitation of a power MOSFET resulting from large gate resistance is studied. It is shown that a maximum gate switching frequency ( $f_{G, max}$ ) can be identified to minimize resistive power dissipation in the gate. Power MOSFET's with refractory silicide gates are shown to result in more than a fivefold improvement in  $f_{G, max}$  compared to conventional heavily POCl<sub>3</sub>-doped polysilicon gated MOSFET's with metal gate runners.

## I. INTRODUCTION

**P**OWER MOSFET's are the key elements of highfrequency power systems such as high-density power supplies [1]. High input impedance of an MOS gate is used to provide efficient gate control in a variety of MOS-bipolar conductivity modulated high-power devices. Gate resistance of a MOSFET has been known to result in degraded frequency response [2], [3] and to cause long-term reliability problems [4]. Conventional power MOSFET's fabricated using heavily doped polysilicon gates result in large gate interconnect resistances. Metal gate runners can be used to reduce gate resistance somewhat, but this approach leads to ineffective usage of silicon. Recently, high-temperature stable process technologies using refractory metals/silicides have been reported for fabricating high-density power MOSFET structures [5].

In this paper, high-frequency switching limitation of a power MOSFET resulting from large gate resistance is studied. It is shown that in addition to conventional high-frequency switching limitations, a new gate-resistance-limited maximum gate switching frequency  $(f_{G, \max})$  can be identified. At  $f_{G, \max}$  resistive power dissipated in the gate equals the power required for charging and discharging the input capacitance. For equal die sizes, power MOSFET polysilicon gates with refractory silicides result in more than a fivefold improvement in  $f_{G, \max}$  compared to conventional power MOSFET's with heavily doped polysilicon gates and with metal gate runners. A fivefold improvement in gate-resistance-induced dV/dt capability and a significant reduction in total power loss is obtained for power MOSFET's with polycide gates.

### **II. FREQUENCY ANALYSIS AND RESULTS**

The device structure and process technology of vertical double-diffused power MOSFET's studied in this work have been described elsewhere [5], [6]. Input capacitance  $C_{in}$  is

The author is with the Corporate Research and Development Center, General Electric Company, Schenectady, NY 12301.

IEEE Log Number 9040434.

the sum of gate-source  $(C_{GS})$  and gate-drain  $(C_{GD})$  capacitances where  $C_{GS}$  consists of MOS inversion layer capacitance  $(C_{GC})$  and gate-source overlap region capacitance  $(C_{GO})$ . In this paper, the distributed *RC* input network of a power MOSFET gate is modeled as a series connection of  $R_G$  and  $C_{in}$ . Gate switching power loss  $P_{SW}$  is defined as equal to energy required for charging and discharging input capacitance and is given by

$$P_{SW} = \frac{fC_{\rm in}V_{GS}^2}{1 + \omega^2 R_G^2 C_{\rm in}^2}$$

(1)

where  $\omega = 2 \pi f$  is the angular power conversion frequency and  $V_{GS}$  is the input voltage swing. Resistive power dissipated in the gate  $(P_G)$  is separately given by

$$P_G = \frac{\omega^2 C_{in}^2 V_{GS}^2 R_G}{2(1 + \omega^2 C_{in}^2 R_G^2)}$$

(2)

under sinusoidal switching conditions. Conduction power loss  $P_C$  is equal to

$$P_C = I_r^2 R_{\rm on} \tag{3}$$

where  $I_r$  is the rms output current and  $R_{on}$  is the static on-state resistance. For a given device technology, a specific on-state resistance  $R_{sp}(=R_{on}A)$  and a specific input capacitance  $C_{sp}(=C_{in}/A)$  can be defined independent of die area A. It has been shown that the product of  $R_{sp}$  and  $C_{sp}(=$  $k_{DEV}$ ) can be used as a figure of merit for evaluating performance potential of a given device technology for application in high-frequency power conversion functions [7]. Neglecting off-state power loss and that resulting from the finite reverse recovery transient of the parasitic p-n junction drain-source diode inherent in a power DMOSFET, the total power loss in a full conversion cycle  $(P_T)$  is equal to the sum of  $P_{SW}$ ,  $P_G$ , and  $P_C$ . Accurate gate resistance characterization based on calorimetric power loss measurements indicated that  $R_G$  was a weak function of die area A, device geometry, and cell structure [8].

Table I lists important measured static parameters of 30-V power MOSFET's fabricated using scaled device technologies, where  $I_{Dsp}$  is the maximum peak output current-handling capability per unit die area. Capacitances listed in Table I correspond to input capacitances with drain-source terminals shorted and therefore represent the worst-case input impedance during gate switching. For a switching power supply with a specified output voltage, an optimum die area  $A_m$  can be determined to minimize  $P_T$ . Table II lists opti-

Manuscript received July 18, 1990; revised September 11, 1990.

### SHENAI: GATE-RESISTANCE-LIMITED SWITCHING FREQUENCIES

TABLE I Measured Static Parameters of 30-V Power MOSFET's

| Parameter        | Unit               | Polysilicon Gate | Polycide Gate |  |

|------------------|--------------------|------------------|---------------|--|

|                  |                    |                  |               |  |

| I <sub>Dsp</sub> | A /cm²             | 600              | 600           |  |

| R <sub>sp</sub>  | $m\Omega$ - $cm^2$ | 0.35             | 0.29          |  |

| C <sub>sp</sub>  | pF/cm <sup>2</sup> | 38,400           | 36,800        |  |

| k <sub>DEV</sub> | $pF \times \Omega$ | 13.5             | 10.7          |  |

| R <sub>G</sub>   | Ω                  | 1.5              | 0.3           |  |

|                  |                    | ]                | 1             |  |

TABLE II Optimum Performance of 30-V MOSFET's in a 100-W, 5-V, 10-MHz Power Supply

| Parameter          | Unit | Polysilicon Gate | Polycide Gate |  |

|--------------------|------|------------------|---------------|--|

| I,                 | Α    | 14.1             | 14.1          |  |

| V <sub>GS</sub>    | v    | 10               | 10            |  |

| P <sub>C</sub>     | w    | 2.15             | 1.6           |  |

| P <sub>SW</sub>    | w    | 1.23             | 1.33          |  |

| P <sub>G</sub>     | w    | 0.45             | 0.11          |  |

| $P_T$              | w    | 3.83             | 3.04          |  |

| Die Size mil x mil |      | 72 x 72          | 76 x 76       |  |

mized power MOSFET parameters for a 100-W, 5-V, 10-MHz power supply where die size corresponds to packaged device dimensions. These results suggest that for a 5% larger die size more than a 20% lower power loss results by replacing conventional polysilicon gates with polycide gates.

In many high-frequency power switching systems it may be possible to recover  $P_{SW}$  by using a resonant switching topology. Resistive power loss in the gate, however, cannot be recovered. Power loss calculations were performed for 30-V power MOSFET's using the static parameters listed in Table I. These calculations were first performed versus switching frequency where conduction current corresponded to maximum output current-handling capability for a 100-mil die. Power MOSFET's with polysilicon gates resulted in a significantly higher power loss. Gate power loss  $P_G$  increased rapidly with frequency and eventually exceeded  $P_{SW}$ . A maximum gate switching frequency  $f_{G, \max}$  was identified where  $P_G = P_{SW}$ . Table III lists the calculated values of  $f_{G, \text{max}}$  for the 30-V power MOSFET's studied here. For comparison, conventional switching frequencies are also listed in Table III where  $f_{in}$  corresponds to the switching frequency limited by the input gate RC time constant,  $f_M$  is the maximum frequency of operation where gate current becomes equal to output current, and  $f_T$  is the transit-time limited frequency [1]. In Table III,  $g_m$  corresponds to linear region transconductance,  $\mu_n$  is the MOS inversion-layer elecOptimized 100-mil  $\times$  100-mil, 30-V Power MOSFET's with  $V_{GS}=$  10 V,  $L_{CH}=$  1  $\mu m,~L_{D}=$  4  $\mu m,~V_{T}=$  2 V, and  $BV_{PP}=$  35 V

| Parameter       | Unit                | Formula                                                               | Polysilicon Gate    | Polycide Gate       |

|-----------------|---------------------|-----------------------------------------------------------------------|---------------------|---------------------|

| 8m              | $\Omega^{\cdot 1}$  | $\frac{\mu_n C_{ax} W_{CH} I_{Dsp} R_{sp}}{L_{CH}}$                   | 51                  | 42                  |

| ∫G,max          | Hz                  | $\frac{1}{2\pi^2 C_{in} R_G}$                                         | 14×10 <sup>6</sup>  | 73×10 <sup>6</sup>  |

| f in            | Hz                  | $\frac{1}{2\pi C_{in}R_G}$                                            | 44×10 <sup>6</sup>  | 230×10 <sup>6</sup> |

| fм              | Hz                  | $\frac{g_m}{2\pi C_{in}}$                                             | 3.4×10 <sup>9</sup> | 2.9×10 <sup>9</sup> |

| fT              | Hz                  | $\frac{6.11 \times 10^{11} B V_{PP}^{7/6}}{(1 + \frac{L_{CH}}{L_D})}$ | 7.7×10 <sup>9</sup> | 7.7×10°             |

| <u>dV</u><br>dt | V.sec <sup>-1</sup> | $\frac{V_T}{R_G C_{GD}}$                                              | 7.4×10 <sup>8</sup> | 3.8×10 <sup>9</sup> |

|                 | l                   | L                                                                     | L                   | l                   |

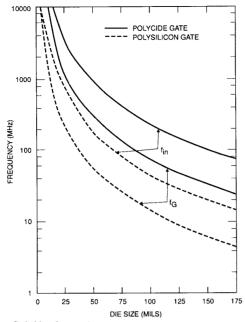

tron mobility,  $C_{ox}$  is the gate oxide capacitance per unit gate area,  $L_{CH}$  is the MOS inversion channel length,  $W_{CH}$  is the channel width,  $L_D$  is the drift region length, and  $BV_{PP}$  is the breakdown voltage of the p-base to n-epi parallel plane junction. Switching frequency limitations imposed by  $f_M$  and  $f_T$  far exceed those caused by  $f_{in}$  and  $f_{G, max}$ . Thus, the maximum switching frequency of a power MOSFET may not exceed  $f_{G, max}$ , beyond which gate resistive power dissipation becomes excessively large. Fig. 1 shows  $f_{in}$  and  $f_{G, max}$  as a function of die size assuming a square die. These results suggest that more than a fivefold improvement in  $f_{G, max}$  can be achieved using polycide MOS gates.

A important switching limitation in power devices results from the rate of change of output voltage or the dV/dtcapability. In a power MOSFET, for example, a parasitic gate turn-on may occur if the rate of change of output voltage is sufficient to produce a threshold voltage drop across gate resistance [1]. This situation results from current flow into the input circuit because of voltage fluctuations across  $C_{GD}$ . The resulting dV/dt capability is given by

$$\frac{dV}{dt} = \frac{V_T}{R_G C_{GD}}.$$

(4)

A fivefold improvement in dV/dt capability is obtained for power MOSFET's with polycide gates as shown in Table III.

Fig. 1. Switching frequencies versus die size for 30-V power MOSFET's. The values of  $f_M$  and  $f_T$  listed in Table III are independent of die size.

## **III. DISCUSSIONS AND CONCLUSIONS**

It is shown that nearly a fivefold reduction in gate resistance can be obtained by incorporating refractory metals/silicides on power MOSFET polysilicon gates. Input switching frequency limitations resulting from large gate resistances are studied. A maximum gate switching frequency  $f_{G, \text{max}}$  is identified beyond which resistive power dissipation in the gate becomes excessively large. Power MOSFET's with polycide gates are shown to result in more than fivefold improvements in  $f_{G, \text{max}}$  and output dV/dt capability. In a number of power converters such as those employed in automotive electronics, telecommunication, power supplies, display drives, motor control, and medical electronics, power devices with die sizes in excess of 100 mils on a side are common. In addition to imposing severe frequency switching limitations, large gate resistance can lead to destructive long-term failure modes of operation. In such circuits, in addition to minimizing the gate interconnect resistance, series resistance of gate driver circuit should also be reduced. However, gate interconnect resistance takes a higher precedence here as it directly impacts unit cells that constitute the power device.

#### REFERENCES

- [1] B. J. Baliga, Modern Power Devices. New York: Wiley, 1987.

- [2] H. C. Lin, Y. F. Arzoumanian, J. L. Halsor, M. N. Giuliano, and H. F. Benz, "Effect of silicon-gate resistance on the frequency response of MOS transistors," *IEEE Trans. Electron Devices*, vol. ED-22, pp. 255-264, 1975.

- [3] K. C. Saraswat and F. Mohammadi, "Effect of interconnection scaling on time delay of VLSI circuits," *IEEE Trans. Electron Device*, vol. ED-29, pp. 645-650, Apr. 1982.

- [4] G. M. Dolny, C. F. Wheatly, Jr., and H. R. Ronan, "Computer-aided analysis of gate-voltage propagation effects in power MOSFET's," *Tech. Papers 1st Int. High Frequency Power Conversion* (Intertec Commun., Inc., Ventura, CA), May 1986, pp. 149-154.

- [5] K. Shenai, C. S. Korman, J. P. Walden, A. J. Yerman, and B. J. Baliga, "Optimized silicon low-voltage power MOSFET's for highfrequency power conversion," in *IEEE Power Electron. Specialists Conf. Rec.*, vol. 1, June 1989, pp. 180-189.

- [6] K. Shenai, "Optimally scaled low-voltage vertical power MOSFET's for high-frequency power conversion," *IEEE Trans. Electron De*vices, vol. 37, no. 4, pp. 1141-1153, Apr. 1990.

- [7] K. Shenai, C. S. Korman, and B. J. Baliga, "Optimum silicon and GaAs power field-effect transistors for advanced high-density, highfrequency power supply applications," in *Tech. Papers 4th Int. High Frequency Power Conversion* (Intertec Commun. Inc., Ventura, CA), May 1989, pp. 32-61.

- [8] K. Shenai, "Accurate characterization of gate resistance and its effect on high-frequency switching efficiencies of power MOSFET's," in 1990 IEEE PESC Rec. (IEEE Cat. 90CH2873-8), vol. I, 1990, pp. 107-12.