4412开发板rfid(spi)模块问题

在使用嵌入式SCP4412精英版大内存开发板时出现问题:

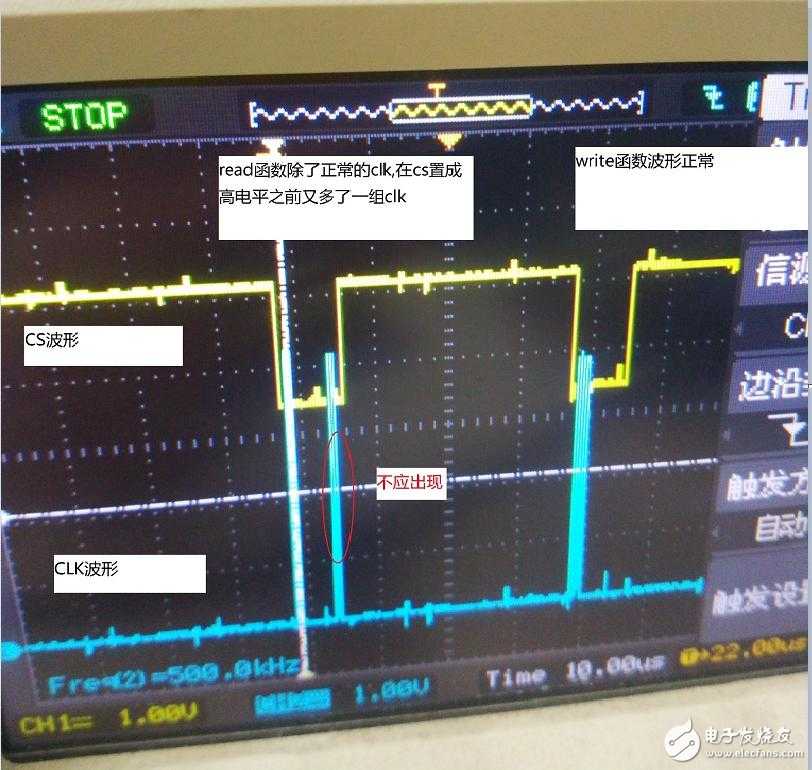

我用 4412开发板资料\iTOP4412开发板资料汇总(不含光盘内容)\iTOP-4412开发板系统源码及镜像(其他)\小模块的测试程序\RFID\rfidtest.rar 这个程序操作spi时发现管脚波形跟我想象的不一样。我直接运行rfidtest那个程序(为了方便观察波形,把cardreader.ReadCardNum()这个函数循环多次连续调用,不然按一次recv只出现很短时间的话示波器观察不到)。然后得到这张示波器波形图。问题主要是在调用read函数时,会多出一组不应该出现的clk。

这个现象在我的开发板上一直出现,包括我通过ioctl函数修改了通信频率、通信数据的长度等等参数后都存在,而且在一些情况下多出来的那一组clk会延伸到cs置为高电平之后,造成整个通讯的错误。

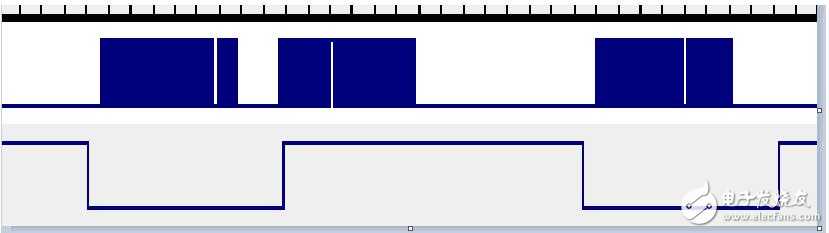

第二张是使用2Mhz,32位数据长度时跟FPGA通讯,在fpga端读到的,左边那个是read函数,可一看到多出来的一组clk已经延伸到cs置成高电平之后了[img]file:///C:\Users\鸣威\Documents\Tencent Files\1436895767\Image\C2C\3NB[A}W4REMQG~MH4SA~4A9.png[/img](多出来的这组clk在我把数据长度设成32位后也变成了32位)。

我是想拿jni里调用的read、write函数直接当做spi对外读写,就像串口那样,我试过基本是对的,就是读的过程结束之后最后会多出图片里那种clk.

比如我在我的程序里连续读了32*n个数据(此期间cs是低电平),读完之后,在cs跳变到高电平之前会出现一组32个clk的波形,不论n多长或者多短(哪怕=1)都会出现一组32个clk。而我的数据如果选择八位的通讯模式则会出现一组8位的clk

。上面的两个图就是这个现象(当然这两个图里读的长度分别是8*1和32*1)

而write函数直接用就是对的。

这组多出的clk可以复现,关键是多的这组信号虽然长度是固定的,但是会有一部分在cs低电平里,一部分在cs高电平里,多的这个东西和cs上升沿的相对位置会变化,就带来很多麻烦,而且按照spi协议来说不应该有这个。

而且数据和时钟是对的,这个多出来的东西纯粹是多余的。

麻烦大家看看这个是不是个例,或者有没有其它版本的固件可以使用spi或者rfid模块

[img]file:///C:\Users\鸣威\Documents\Tencent Files\1436895767\Image\C2C\@0PV4OAYKG[`2~_R1B0O92X.jpg[/img]

示波器波形

第二张,2Mhz,32位

已退回5积分