cortex m3的SYSCLK和内存访问时间比例问题

时间:10-02

整理:3721RD

点击:

file:///C:\Users\Administrator.KYKYOP5KIAAIPRU\AppData\Roaming\Tencent\Users\2269903095\QQ\WinTemp\RichOle\92ELR8FS{PI93SEF]NP5KH9.jpg

static void SetSysClockTo56(void)

{

__IO uint32_t StartUpCounter = 0, HSEStatus = 0;

/*!< SYSCLK, HCLK, PCLK2 and PCLK1 configuration ---------------------------*/

/*!< Enable HSE */

RCC->CR |= ((uint32_t)RCC_CR_HSEON);

/*!< Wait till HSE is ready and if Time out is reached exit */

do

{

HSEStatus = RCC->CR & RCC_CR_HSERDY;

StartUpCounter++;

} while((HSEStatus == 0) && (StartUpCounter != HSEStartUp_TimeOut));

if ((RCC->CR & RCC_CR_HSERDY) != RESET)

{

HSEStatus = (uint32_t)0x01;

}

else

{

HSEStatus = (uint32_t)0x00;

}

if (HSEStatus == (uint32_t)0x01)

{

/*!< Enable Prefetch Buffer */

FLASH->ACR |= FLASH_ACR_PRFTBE;

/*!< Flash 1 wait state */ 请看这里,系统时钟要设置为56M,应该是两个等待状态才对啊?请高手指点

FLASH->ACR &= (uint32_t)((uint32_t)~FLASH_ACR_LATENCY);

FLASH->ACR |= (uint32_t)FLASH_ACR_LATENCY_1;

/*!< HCLK = SYSCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_div1;

/*!< PCLK2 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_div1;

/*!< PCLK1 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_div2;

/*!< PLLCLK = 8MHz * 7 = 56 MHz */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLMULL));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC | RCC_CFGR_PLLMULL7);

/*!< Enable PLL */

RCC->CR |= RCC_CR_PLLON;

/*!< Wait till PLL is ready */

while((RCC->CR & RCC_CR_PLLRDY) == 0)

{

}

/*!< Select PLL as system clock source */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL;

/*!< Wait till PLL is used as system clock source */

while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08)

{

}

}

else

{ /*!< If HSE fails to start-up, the application will have wrong clock

configuration. User can add here some code to deal with this error */

/*!< Go to infinite loop */

while (1)

{

}

}

}

static void SetSysClockTo56(void)

{

__IO uint32_t StartUpCounter = 0, HSEStatus = 0;

/*!< SYSCLK, HCLK, PCLK2 and PCLK1 configuration ---------------------------*/

/*!< Enable HSE */

RCC->CR |= ((uint32_t)RCC_CR_HSEON);

/*!< Wait till HSE is ready and if Time out is reached exit */

do

{

HSEStatus = RCC->CR & RCC_CR_HSERDY;

StartUpCounter++;

} while((HSEStatus == 0) && (StartUpCounter != HSEStartUp_TimeOut));

if ((RCC->CR & RCC_CR_HSERDY) != RESET)

{

HSEStatus = (uint32_t)0x01;

}

else

{

HSEStatus = (uint32_t)0x00;

}

if (HSEStatus == (uint32_t)0x01)

{

/*!< Enable Prefetch Buffer */

FLASH->ACR |= FLASH_ACR_PRFTBE;

/*!< Flash 1 wait state */ 请看这里,系统时钟要设置为56M,应该是两个等待状态才对啊?请高手指点

FLASH->ACR &= (uint32_t)((uint32_t)~FLASH_ACR_LATENCY);

FLASH->ACR |= (uint32_t)FLASH_ACR_LATENCY_1;

/*!< HCLK = SYSCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_div1;

/*!< PCLK2 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_div1;

/*!< PCLK1 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_div2;

/*!< PLLCLK = 8MHz * 7 = 56 MHz */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLMULL));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC | RCC_CFGR_PLLMULL7);

/*!< Enable PLL */

RCC->CR |= RCC_CR_PLLON;

/*!< Wait till PLL is ready */

while((RCC->CR & RCC_CR_PLLRDY) == 0)

{

}

/*!< Select PLL as system clock source */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL;

/*!< Wait till PLL is used as system clock source */

while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08)

{

}

}

else

{ /*!< If HSE fails to start-up, the application will have wrong clock

configuration. User can add here some code to deal with this error */

/*!< Go to infinite loop */

while (1)

{

}

}

}

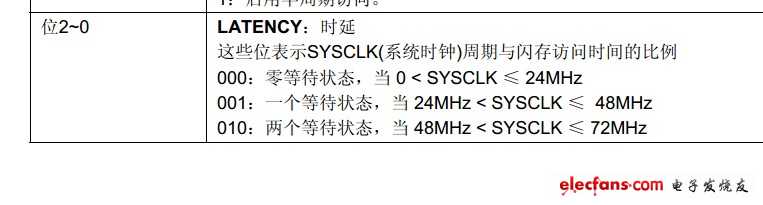

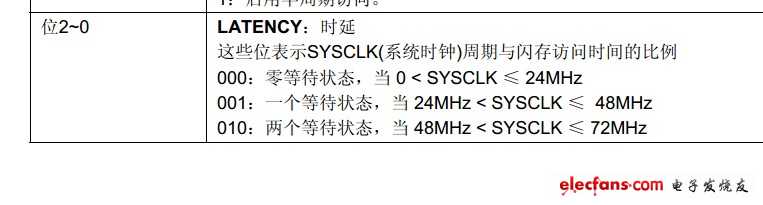

/*!< Flash 1 wait state */ 请看这里,系统时钟要设置为56M,应该是两个等待状态才对啊?请高手指点

-------------------------------

你的质疑是有道理的 不能全相信代码 官方提供的例程也是有bug的

>48MHz要设置成两个时钟延迟,按照技术手册给出的资料是这样的;

56超出48有17%,在一般设计容限上是在允许范围内的,所以此处设置一个时钟延时,程序是能够正常运行;只能说这个程序作为例子,不太严谨!

我们的电脑能够超频使用,就是根据这个原理来的