关于74hc165(并行输入,串行输出)芯片的一个小疑惑

在51单片机开发板实验中,我用到了74hc165芯片。关于根据它的时序进行编程遇到了一点疑问。

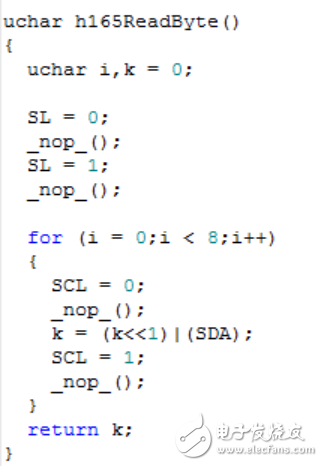

能正常实现功能的程序(只写出74H165读数据这个函数)下:

uchar h165ReadByte()

{

uchar i,k = 0;

SL = 0;

_nop_();

SL = 1;

_nop_();

for (i = 0;i < 8;i++)

{

SCL = 0;

_nop_();

k = (k<<1)|(SDA);

SCL = 1;

_nop_();

}

return k;

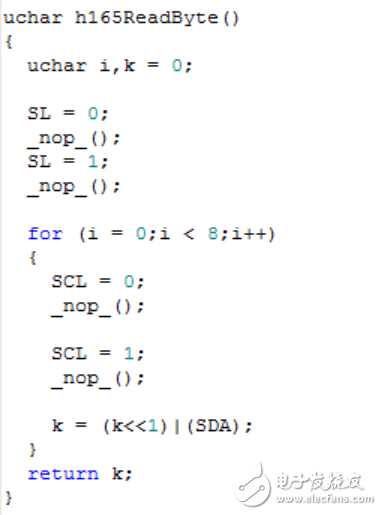

上图是正确的程序,下图是不正确的但我认为有道理的程序。

注:SL是移位/置入控制端,SCL是时钟输入端,SDA是数据输出端,

SL = 0;_nop_();SL = 1;_nop_();这一段是让数据进入移位寄存器。

我的【疑问】就是【k = (k<<1)|(SDA);】这句话的位置,数据手册貌似说时钟上升沿时,数据进入数据输出端(我看教学视频是这么说的,但在数据手册上没找到这句话),那么k = (k<<1)|(SDA)这句话不应该加在SCL = 1(上升沿完成之后)之后吗,为什么要加在SCL=0和SCL=1中间?所以数据到底什么时候开始移动到了输出端?

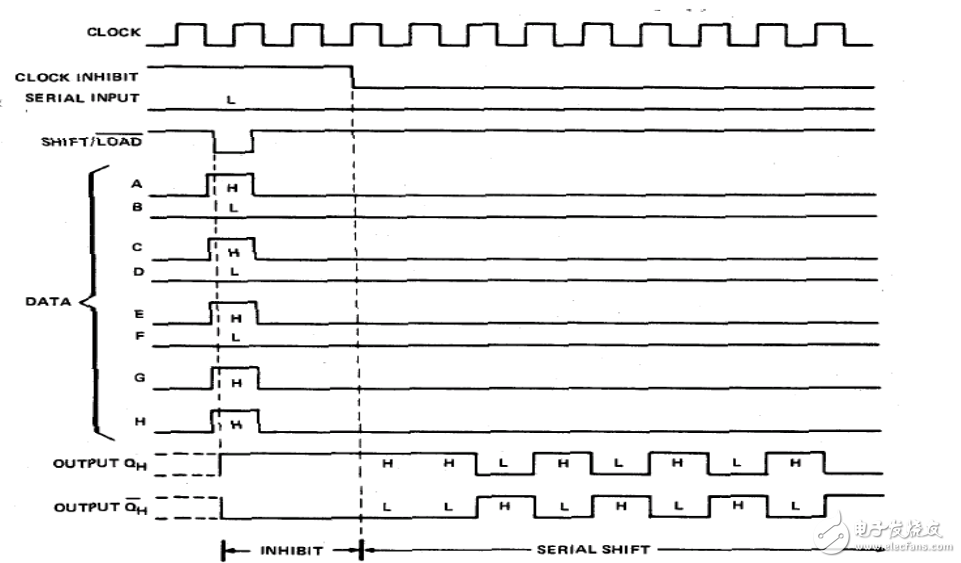

时序图如下,

图片里两段程序,下面的程序的错误不在于k = (k<<1)|(SDA)与SCL = 1的位置,而是在于SL已经把数据移到SDA,不在SCL = 1先读一位数据的话,会丢失一位数据,如果能做试验的话,可以试出读出的数据和实际数据是错了一位

是不是数据输入端的最高位D7与数据输出端(我记为SDA)在物理上是连通的,只要在D7位置上的数据,就相当于是数据输出端SDA的数据(因为二者物理连通)?可以这么理解吗?

是不是数据输入端的最高位D7与数据输出端(我记为SDA)在物理上是连通的,只要在D7位置上的数据,就相当于是数据输出端SDA的数据(因为二者物理连通)?可以这么理解吗?

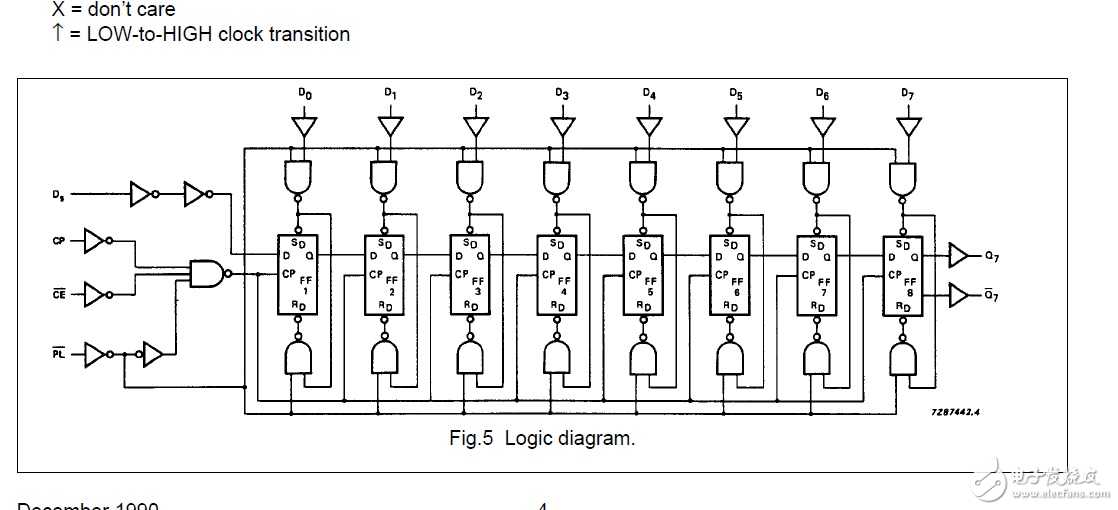

芯片内部是不连通的,SL引脚是一个信号,当有效时,将并口上D0-D7的数据移送到内部的串行寄存器,之后以SCL作为移位信号,将串行寄存器里的数据通过SDA引脚一位一位的送出。这只是数字电路里的移位寄存器和锁存器的原理。

根据165芯片手册里的真值表,在给SL引脚一个有效信号后,在使用SCL移动数据前,应该给SL引脚一个关闭信号。

有一个问题:当并行口口的数据被锁存之后,第一次执行k = (k<<1)|(SDA);显然SCL还没有上升沿,这说明没有移位就读取第一个数据了,即数据输出口SDA和最高位D7(DH)的数据是保持一致的,然后时钟信号才有一个上升沿,发生移位,我想问的是这个移位是D6的数据直接移到输出口SDA还是D6的数据移到D7的位置上

图片中红框部分是并口部分,当图片中的PL(也就是你程序里的SL)信号有效时,将并口D0-D7的数据移入到蓝框的移位寄存器电路里。这时移位寄存器电路的输出引脚QH=D7,只是电平信号相等,但是线路并不连通,所以如果在移位操作前不读取这个数据,那么最终的数据将错一位。这里的移位寄存器实际是RS触发器,所以当将并口数据移入RS触发器时,各数据位的0或1的电平信号都同时出现在各个RS触发器的Q端,这是RS触发器的原理,是可以直接读取的,对于整个165来说,移位时钟信号CP(程序里的SCL)信号的作用是把串行数据往前移,只是起到数据移动的作用。