MSP430F5172 I/O 配置以后,ADS1220 芯片上DRDY引脚为什么直接就是低电平300mV左右?

时间:10-02

整理:3721RD

点击:

MSP430F5172使用ADS1220芯片采样,但是发现系统上电以后,DOUT/DRDY和DRDY引脚是高电平,没问题。配置I/O寄存器以后发现降到300mV左右,无法触发采样完成中断,请问这是什么原因?

其中DOUT/DRDY是P1.3,DRDY引脚是P1.4,I/O寄存器配置代码如下。

void portsInit (void)

{

P1OUT = BIT0;//CS

P1DIR = 0xE7;//P1.0 P1.1 P1.2 P1.5 P1.6 P1.7 输出,P1.3 P1.4 输入

P2OUT = 0x00;

P2DIR = 0xFF;//未用引脚,配置为输出模式。

P3OUT = 0x00;

P3DIR = 0xFF;//未用引脚,配置为输出模式。

PJOUT = 0x00;

PJDIR = 0xFF;//未用引脚,配置为输出模式。

PMAPPWD = 0x02D52; // Enable Write-access to modify port mapping registers

P1MAP1 = PM_UCB0CLK;

P1MAP2 = PM_UCB0SIMO;

P1MAP3 = PM_UCB0SOMI;

P1SEL |= (ADS_CLK + ADS_DIN + ADS_DOUT);

//ADS1220 nDRDY Interrupt

P1IES |= (ADS_DRDY_N); // High to Low Edge

P1IFG &= ~(ADS_DRDY_N); // Clear any previous interrupt

P1IE |= (ADS_DRDY_N);

}

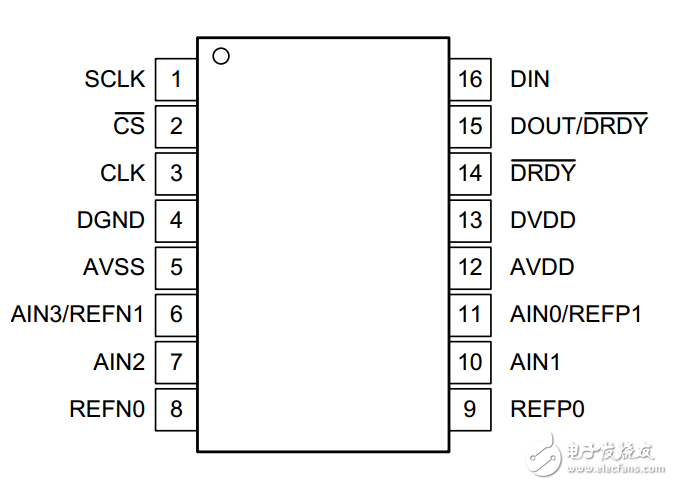

附ADS1220引脚图

其中DOUT/DRDY是P1.3,DRDY引脚是P1.4,I/O寄存器配置代码如下。

void portsInit (void)

{

P1OUT = BIT0;//CS

P1DIR = 0xE7;//P1.0 P1.1 P1.2 P1.5 P1.6 P1.7 输出,P1.3 P1.4 输入

P2OUT = 0x00;

P2DIR = 0xFF;//未用引脚,配置为输出模式。

P3OUT = 0x00;

P3DIR = 0xFF;//未用引脚,配置为输出模式。

PJOUT = 0x00;

PJDIR = 0xFF;//未用引脚,配置为输出模式。

PMAPPWD = 0x02D52; // Enable Write-access to modify port mapping registers

P1MAP1 = PM_UCB0CLK;

P1MAP2 = PM_UCB0SIMO;

P1MAP3 = PM_UCB0SOMI;

P1SEL |= (ADS_CLK + ADS_DIN + ADS_DOUT);

//ADS1220 nDRDY Interrupt

P1IES |= (ADS_DRDY_N); // High to Low Edge

P1IFG &= ~(ADS_DRDY_N); // Clear any previous interrupt

P1IE |= (ADS_DRDY_N);

}

附ADS1220引脚图

ADS1220引脚图

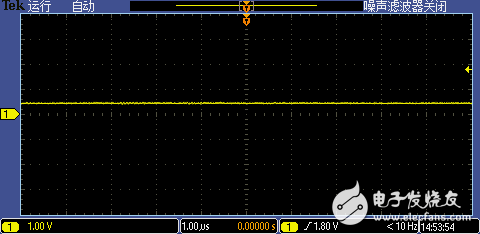

DRDY引脚电压

P1.4/PM_UCB0SIMO,这是SPI复用引脚,当P1SEL.4使能第二功能时,P1.4脚电平为模块自动控制了,肯定是设置为输出,和AD芯片的引脚冲突,如果要用SPI模块请修改电路,或者采用软件控制3个通信引脚来通信

P1.4引脚没有设置为复用。

解决方法找到了,不用的引脚取消配置低电平输出,不用管就好了。但是具体为什么我还不知道,有大神可以解释下不?