在大型的硬件设计上 晶振的冗余设计是否有必要?

时间:10-02

整理:3721RD

点击:

现在数据中心的交换机产品硬件上设计越来越大,一张板卡上时钟数量少的几路,多的要十几二十几路。经常使用一个晶振、多个buffer的设计。那么在这种情况下晶振的冗余设计是否有必要? 如果有必要如何设计晶振的冗余才好呢?能在主时钟挂掉的时候,备用时钟能迅速的顶替?请大神们发表下看法!

失效信号怎么检测最好?或者还有什么好的想法?

自己占沙发。

在数据中心的产品中个人觉得最好还是有晶振的冗余设计,提高硬件上的可靠性。

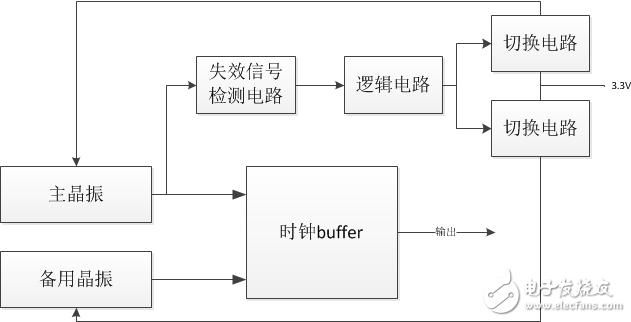

但怎么能够做到满足性能要求的主备时钟切换呢?我来抛砖引玉下,用晶振的供电做为切换源,如下图。

失效信号怎么检测最好?或者还有什么好的想法?