KL 系列 FAQ (十)——LPTMR、模拟比较器

13 LPTMR

13.1 LPTMR 计算公 式

问题:

在 FRDM-KL25Z 开发板上需要做个周期 1s 的定时器,用到了 LPTMR 模块的

定时器模式,请问如何计算比较寄存器 LPTMRx_CMR 的值?

答案:

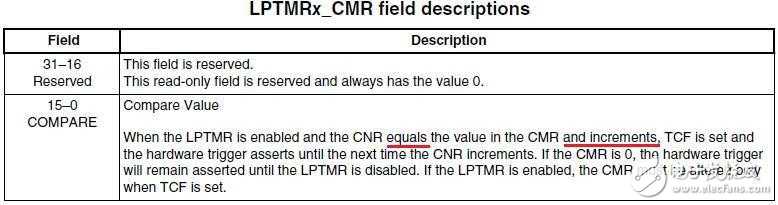

通过查看参考手册 KL25P80M48SF0RM 第三十三章 LPTMRx_CMR 寄存器

COMPARE 位的功能描述可知:当 LPTMR 的计数器 CNR 等于 CMR 并增加时,

TCF 将置位。

根据这个描述就可得到计算公式:

![]()

公式中采用 N+1,而不 是 N,是因为当 LPTMR 使能,CNR 值要等于 CMR 值

并增加 才会使 TCF 标志位置位,触发硬件定时中断。

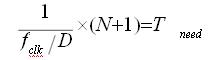

如果时钟源选择 1kHz 的 LPO 即 f clk =1kHz,不分频即 D=1,期望定时 1s 即![]()

13.2 LPTMR 时钟源

问题:

在 FRDM-KL25Z 开发板上需要做个周期 1s 的定时器,用到了 LPTMR 模块的

定时器模式,在计算比较值时如何确定 LPTMR 的时钟源频率?

答案:

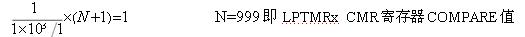

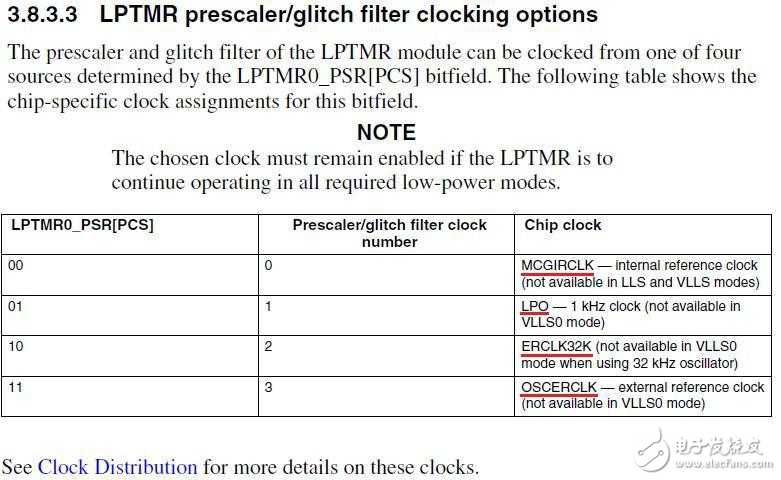

通过查看参考手册 KL25P80M48SF0RM 第三十三章 LPTMRx_PSR 寄存器

PCS 位的功能描述可知 LPTMR 定时器模式所需的分频器时钟源、计数器模式所需

的毛刺滤波器时钟源可通过该寄存器选择。PCS 必须在 LPTMR 禁止时才可改变。

具体时钟源连接参见 chip configuration details 章节(因为时钟源连接可能随芯片不

同而不同)

根据上图 NOTE 提示信 息,查询手册第三章“3.8.3.3 LPTMR prescaler/glitch

filter clocking options” 部分可知 LPTMR 的时钟源可以下四选一:MCGIRCLK、

LPO、ERCLK32K、 OSCERCLK(如下图示)

13.3 LPTMR 脉冲计 数器模式下滤波器功能

问题:

在 FRDM-KL25Z 开发板上想用 LPTMR 模块的脉冲计数器模式,但不明白

LPTMRx _PSR 寄存器 PRESCALE 位描述的滤波器配置。红线划出应如何理解?

答案:

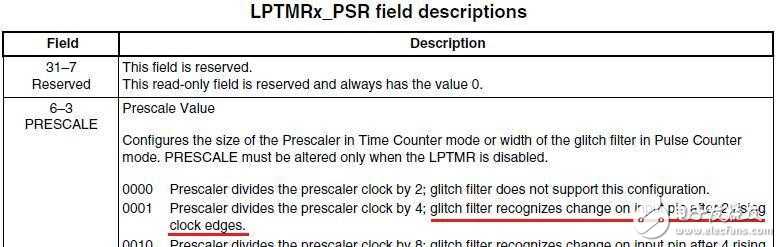

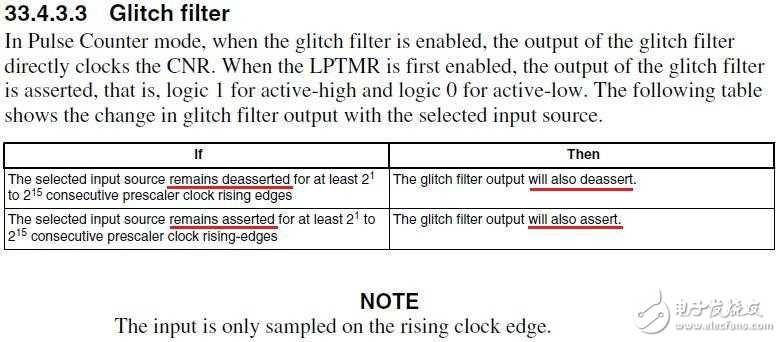

通过查看参考手册 KL25P80M48SF0RM 第三十三章 LPTMRx_PSR 寄存器

PRESCALE 位的功能描述可知:当 LPTMR 处于脉冲计数器模式时,该位用于选择

滤波器宽度。如果结合参考手册 33.4.3.3 Glitch filter 章节描述(如下图),就能更

清楚地了解红线所表达意思是:若输入引脚电平在 LPTMR 时钟源的 2 个上升沿时

间内保持不变,则毛刺滤波器输出状态将取决于输入引脚状态。

13.4 LPTMR 脉冲计 数器模式下输入脚状态解释

问题:

在 FRDM-KL25Z 开发板上想用 LPTMR 模块的脉冲计数器模式,但不明白参考

手册 33.4.3.3 Glitch filter 章节描述中提到的 asserted、deasserted 意思。

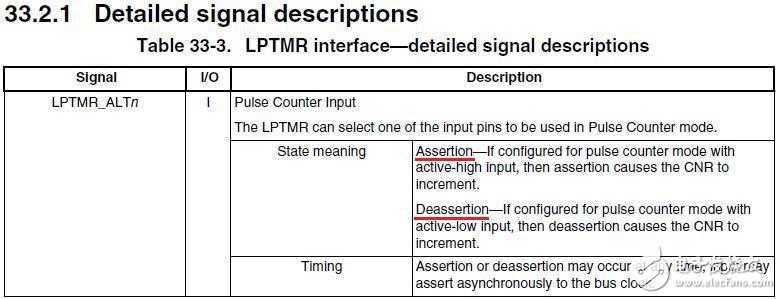

答案:根据参考手册 KL25P80M48SF0RM 的 33.2.1 Detailed signal descriptions 描述

(如下图示)以及 LPTMRx_CSR 寄存器 TPP 位描述可知脉冲计数器模式下:如果

将输入配置成 active-high 则 Assertion(输入上升沿)将导致 CNR 增加。如果将输

入配置成 active-low 则 Deassertion(输入下降沿)将导致 CNR 增加。

再看参考手册 33.4.3.3 Glitch filter 章节表格描述就容易理解毛刺滤波器工作机

理:如果所选输入引脚至少在 2 个 LPTMR 时钟源上升沿时间内保持低电平(高电

平),则毛刺滤波器也将输出低电平(高电平)。

14 模拟比较器 CMP

14.1 KL25 模拟 比较器迟滞电压

问题:

KL25 芯片的 CMPx _CR0 寄存器 HYSTCTR 为从手册上看可以设置不同等级

的迟滞电压,这个迟滞电压将会对模拟比较器产生什么样的效果?

答案:

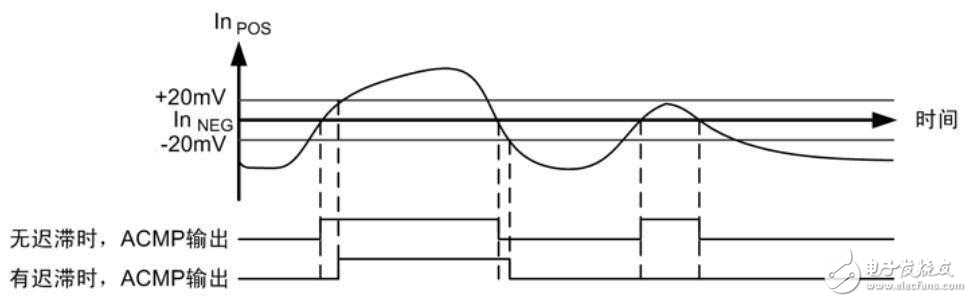

参考手册上提到了迟滞电压分为四种等级,从数据手册 KL25P80M48SF0 的

“Table 21. Comparator and 6-bit DAC electrical specifications”表中可以看到这四种

电压等级分别为 5mV、10mV、20mV、30mV。迟滞电压将避免模拟比较器两端的

输入压较接近时,因为波动或噪声而频繁改变比较器输出问题。以 20mV 迟滞电压

为例,参考下图。

15 综合问题

15.1 KL25 芯片 UID 作用

问题:

像 SIM_SDID 寄存器有相应介绍,知道可以通过读取 SIM_SDID 获得芯片系列、SRAM 大小、硅版本号、引脚数等信息。 但是 KL25 参考手册“12.2 Memory map and register definition ”中的 SIM_UIDMH、SIM_UIDML、SIM_UIDL 这些寄存器是用来 干什么的?

答案:

SIM_UIDMH、SIM_UIDML、SIM_UIDL 这几个寄存器是用于存放芯片唯

一识别号的,每个芯片这几个寄存器的值都是唯一的。

推荐阅读:

KL 系列 FAQ (九)

KL 系列 FAQ (八)

KL 系列 FAQ (七)

KL 系列 FAQ (六)

KL 系列 FAQ (五)

KL 系列 FAQ (四)

KL 系列 FAQ (三)

KL 系列 FAQ (二)

KL 系列 FAQ (一)

群主说:“看帖回帖是一种美德”

小编老虎油,耶!

赞一个,写得好认真啊