NEC单片机中断分析

时间:10-02

整理:3721RD

点击:

中断优先级:可屏蔽中断

硬件设计的默认优先级,以V850ES/Fx3为例,0~79,数字越小,优先级越高。

软件设置优先级,V850ES/Fx3可设8级中断优先级。78K0只有两级。

硬件优先级与软件优先级结合便构成了中断实际的优先级。首先判断软件优先级,若软件优先级相同再判断硬件优先级。

系统硬件设计分析:

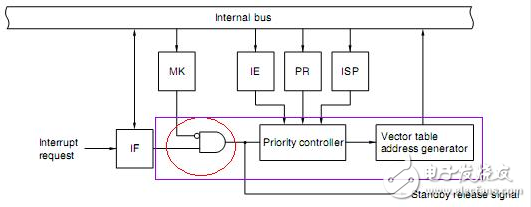

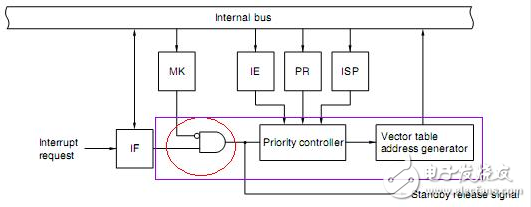

紫色对应的为INTC(中断控制器),独立于CPU。CPU与INTC之间应该有INTREQ(INTC到CPU),INTACK(CPU到INTC),表明中断源的并口线

Marco可屏蔽中断产生需要CPU相应时,将marco与INTC之间的信号线拉高,通知中断控制器有中断来了。INT controller输出INTREQ信号,通知CPU有中断产生。CPU返回INTACK信号,响应该中断。

红色对应的部分应该是每个可屏蔽中断都有一套,macro申请CPU相应时,Interrupt request拉高,不管MK为0还是为1, IF位都被置1。只有当CPU响应该中断发出INTAK信号,IF被清零,Interrupt request被拉低。

也就是说只要某外围模块被使能,即使没用其中断功能(即MK=1),当满足中断产生条件时,IF会被置1,所以写程序时,如果想采集中断使能后的中断,最好将所有的IF都清零,避免CPU响应之前的中断。

如果采用查询方式(例如读串口数据),IF不会自动清零,Interrupt request也一直拉高不会被拉低,除非软件清IF,才能将Interrupt request拉低。

INT控制器传递给CPU的是中断表地址。

NEC单片机进入中断程序前都会自动DI(关闭中断使能),默认不支持中断嵌套,如果需要中断嵌套,需要手动EI(使能中断)

硬件设计的默认优先级,以V850ES/Fx3为例,0~79,数字越小,优先级越高。

软件设置优先级,V850ES/Fx3可设8级中断优先级。78K0只有两级。

硬件优先级与软件优先级结合便构成了中断实际的优先级。首先判断软件优先级,若软件优先级相同再判断硬件优先级。

系统硬件设计分析:

紫色对应的为INTC(中断控制器),独立于CPU。CPU与INTC之间应该有INTREQ(INTC到CPU),INTACK(CPU到INTC),表明中断源的并口线

Marco可屏蔽中断产生需要CPU相应时,将marco与INTC之间的信号线拉高,通知中断控制器有中断来了。INT controller输出INTREQ信号,通知CPU有中断产生。CPU返回INTACK信号,响应该中断。

红色对应的部分应该是每个可屏蔽中断都有一套,macro申请CPU相应时,Interrupt request拉高,不管MK为0还是为1, IF位都被置1。只有当CPU响应该中断发出INTAK信号,IF被清零,Interrupt request被拉低。

也就是说只要某外围模块被使能,即使没用其中断功能(即MK=1),当满足中断产生条件时,IF会被置1,所以写程序时,如果想采集中断使能后的中断,最好将所有的IF都清零,避免CPU响应之前的中断。

如果采用查询方式(例如读串口数据),IF不会自动清零,Interrupt request也一直拉高不会被拉低,除非软件清IF,才能将Interrupt request拉低。

INT控制器传递给CPU的是中断表地址。

NEC单片机进入中断程序前都会自动DI(关闭中断使能),默认不支持中断嵌套,如果需要中断嵌套,需要手动EI(使能中断)